Intel sucht den Speicher der nächsten Generation

„Es gibt keinen guten Speicher“, mit dieser Aussage schließt einer der Vorträge im Rahmen der Intel European Reseach & Innovation Conference (ERIC). Denn alle aktuellen Speicherdesigns sind Kompromisse, sei es im Bereich der Latenz, Kapazität, des Datendurchsatzes und der Skalierbarkeit. Für die Zukunft muss etwas Neues her.

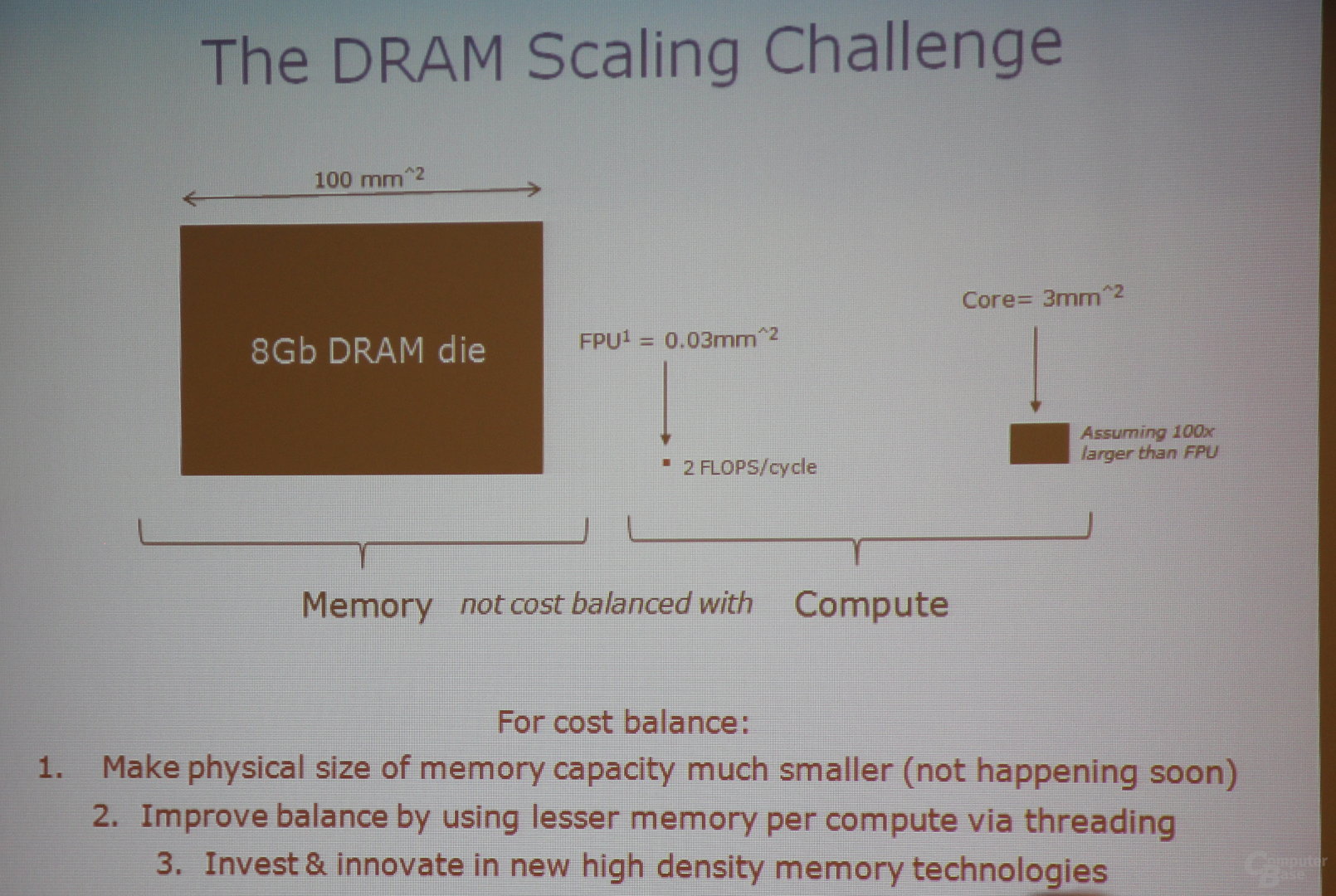

Zwei Vorträge richteten sich am ersten Tag an das Thema Speicher. Im Bereich Exascale-Supercomputer wurde ganz schnell die Skalierbarkeit des Speichers für zukünftige Aufgaben angezweifelt. Denn aktuell ist die Entwicklung in dem Segment an dem Punkt angelangt, an dem buchstäblich ein Prozessor um den Speicher herum designed werden muss, da dieser der größte Flaschenhals ist. Neu ist das Problem jedoch nicht, Firmen aus der HPC-Branche kämpfen seit Jahren damit. Auch Intel gingen dort in einigen Bereichen die Ideen aus, weshalb der Branchengigant bereits im letzten Jahr Know-How vom Supercomputer-Entwickler Cray eingekauft hat, die in der jüngeren Vergangenheit mit eigenen Interconnect-Verbindungen und Speicherdesign die Konkurrenz auf der Strecke ließen.

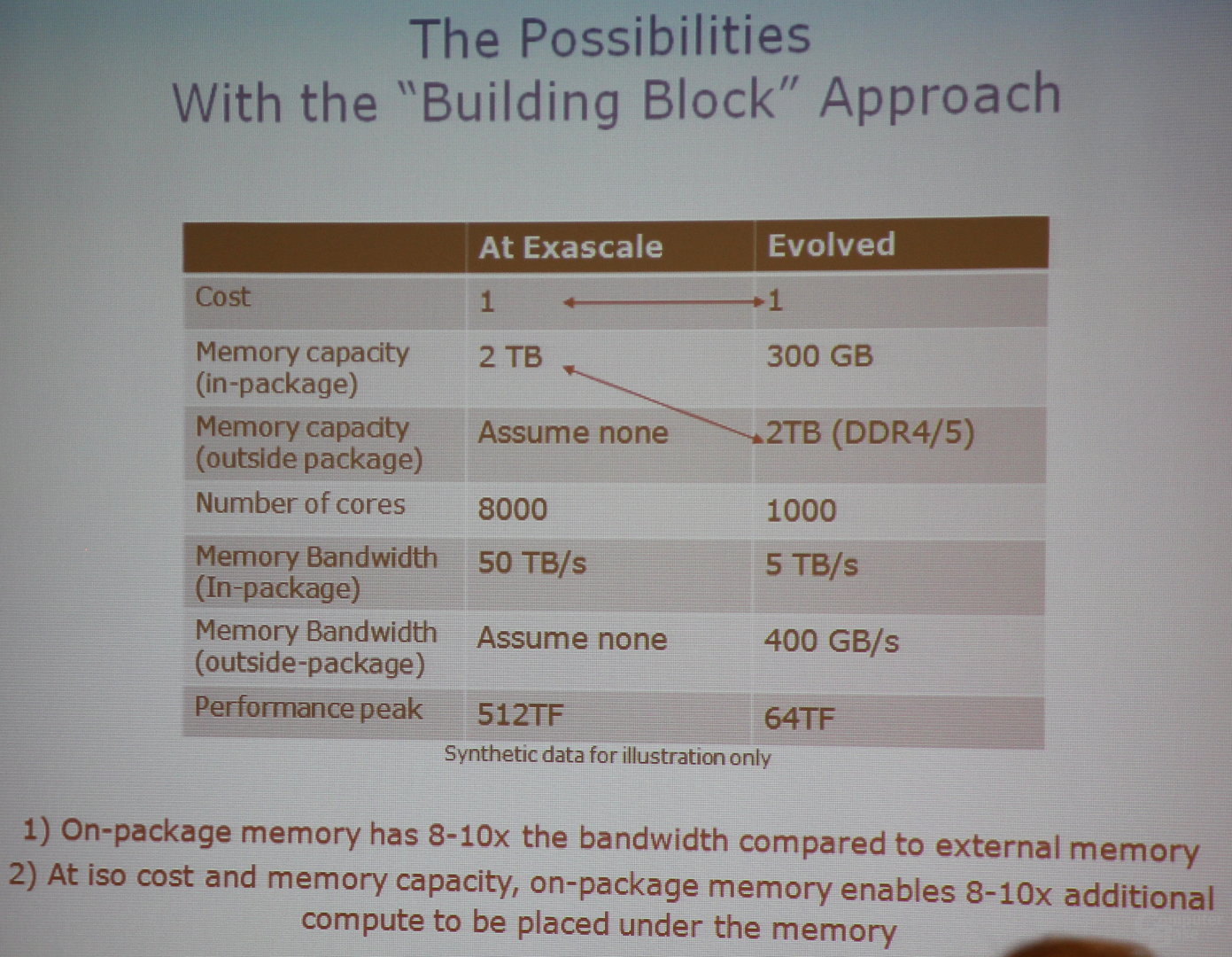

Die schnell greifbaren Lösungen funktionieren jedoch nur bedingt. Es bedarf einer Kombinationen aus diesen und weiteren Neuentwicklungen. In erster Linie gilt das sogenannte „On Package Memory“ als zukunftsweisend. Was im Sommer bei Intels Iris Pro 5200 mit 128 MByte Grafikspeicher (EDRAM) auf dem gleichen Package wie der Prozessor-Die begonnen hat, soll in Zukunft massiv ausgebaut werden. Die Datendurchsatzraten sind sehr hoch, allerdings auch in Zukunft ein insgesamt sehr teures Vergnügen. Zudem wird allein diese Technik auch nicht ausreichen.

Der On-Package-Speicher der Zukunft muss als 3D-Speicher verfügbar sein, wie es Microns Entwicklung des Hybrid Memory Cube (HMC) zeigt. Dort werden die DRAM-Schichten übereinander gestapelt und verbrauchen so keinen kostbaren Platz in der Länge und Breite des Packages, sondern „nur“ in der Höhe. In den Vorträgen ließen die Sprecher anklingen, dass sie das Konzept des HMC seitens Intel mit Sicherheit nutzen werden, ob dabei jedoch Microns Steuerungschips mit genutzt werden, wollte keiner der Beteiligten verraten. Da diese Chips eine elementare Aufgabe bei der Funktion des HMC übernehmen, ist Intel vermutlich an einem eigenen Design interessiert.

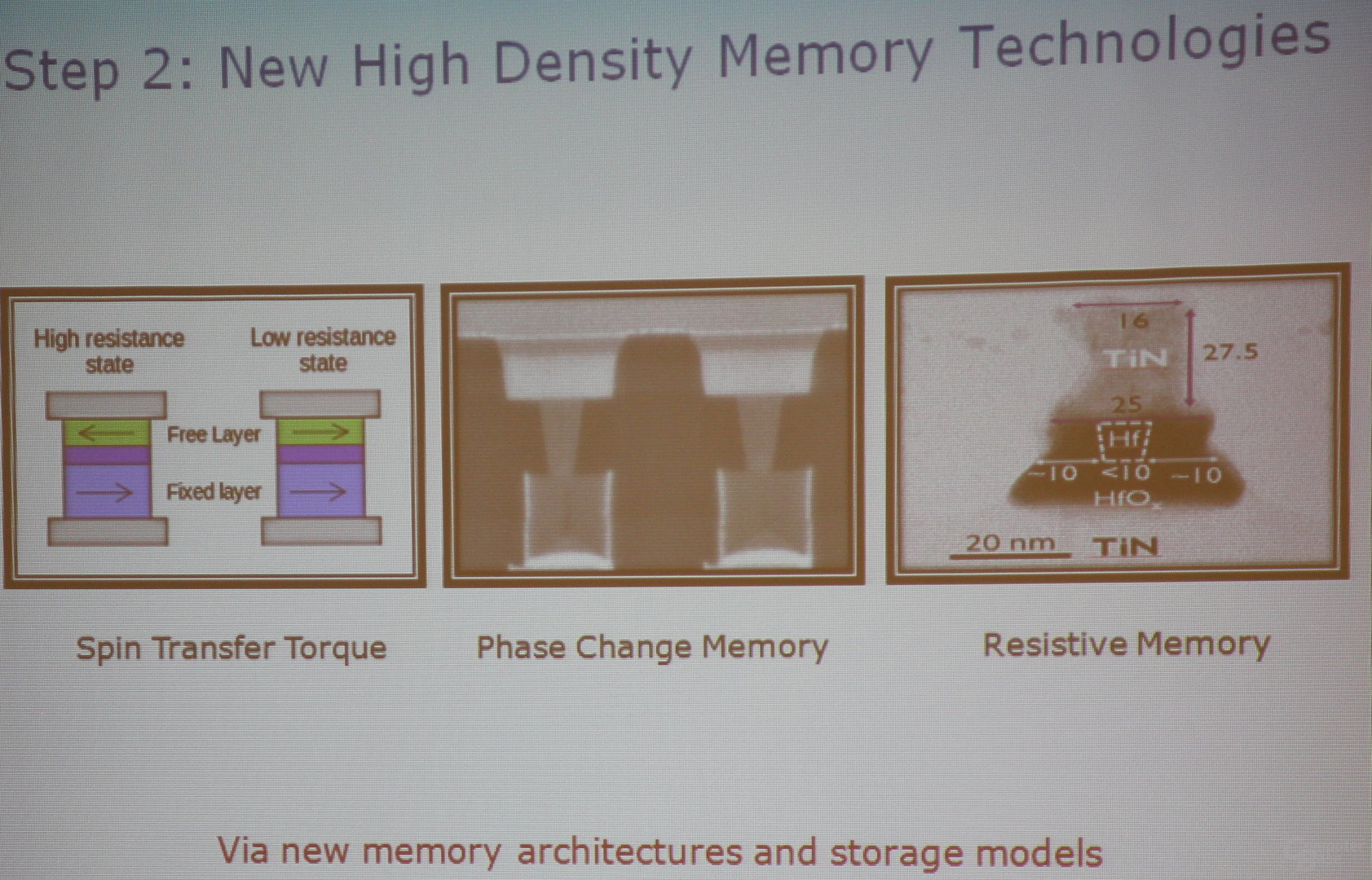

Doch auch mit dem „HMC on Package“ ist noch nicht genug getan. Weiterhin muss an der Größe der Speicherchips im Verhältnis zur Kapazität gefeilt werden. Hier sieht Intel den Vorteil im eigenen Haus, können die Forscher und Entwickler doch quasi nebenan bei den Leuten aus der Fertigung anklopfen und fragen, wann entsprechende 7-nm-Chips mit den und den Vorgaben denn möglich wären. Nach aktuellem Stand ist die besagte 7-nm-Fertigung die Problemzone für DRAM-Speicher. STT-MRAM, Phase Change Memory sowie Resistive Memory (ReRAM) tun sich dabei als drei Alternativen auf, wobei Intel insbesondere dem STT-MRAM gute Chancen als echten Nachfolger für DRAM einräumt.

Am Ende der Vorträge wurde klar, wohin die Reise geht: Hochkapazitiver Speicher soll in Zukunft auf dem gleichen Package wie die CPUs sitzen. Mit der nächsten Generation von Xeon Phi, Codename „Knights Landing“, wird Intel bereits einen Schritt in diese Richtung gehen, doch auch normale CPUs werden über kurz oder lang dieser Entwicklung folgen. Ob die rein zur Illustration gezeigten 2 TByte On-Package-Memory für den ersten Exascale-Computer annähernd zutreffen, wird die Entwicklung der kommenden Jahre im Speicherbereich zeigen. Dabei stellte Intel jedoch klar, dass die gesamte Industrie den Weg gehen muss und man nicht allein dastehen wird, wie die Prototypen der drei neuen Speichermöglichkeiten STT-MRAM, Phase Change Memory sowie (ReRAM) aus komplett unterschiedlichen Häusern zeigen.