HGST: Schnellste SSD der Welt mit Phasenwechselspeicher

Auch bei Western Digitals Tochterunternehmen HGST rückt Flash-Speicher immer mehr in den Fokus. Anlässlich des Flash Memory Summit stellt HGST neue Speicherlösungen für die heutige Zeit sowie die Zukunft vor. Phase Change Memory (PCM) soll künftige SSDs massiv beschleunigen.

An Phasenwechselspeicher, der die Vorzüge von RAM und Flash-Speicher vereinen soll, wird schon seit vielen Jahren geforscht. Meist stand dabei der Einsatz als Arbeitsspeicher (PRAM) im Fokus. Die nicht-flüchtige Speichertechnik soll aber auch bei künftigen Massenspeicherlösungen zum Einsatz kommen.

HGST gibt nun einen Ausblick darauf, was mit PCM im SSD-Bereich möglich sein wird. Das Unternehmen demonstriert eine SSD, die über eine nicht näher beschriebene PCI-Express-Schnittstelle 3 Millionen IOPS beim wahlfreien Lesen (random read) von 512-Byte-Blöcken erreichen soll. Die Zugriffslatenz soll dabei lediglich 1,5 Mikrosekunden betragen. Als technische Basis dient eine Kombination aus nichtflüchtigen PCM-Speicherbausteinen und „latenzoptimierten Schnittstellenprotokollen“.

Um die geringen Latenzen zu ermöglichen, hat HGST zusammen mit Forschern der University of California, San Diego, ein neues Kommunikationsprotokoll (DC Express) entwickelt, das bereits Anfang des Jahres auf der Usenix-Konferenz FAST 2014 vorgestellt wurde. HGST erklärt, dass das neue NVMe-Protokoll zwar bestens für NAND-Flash geeignet ist, für PCM jedoch unzureichend sei.

Die Marke von einer Million IOPS fiel bereits vor acht Jahren, weshalb heute drei Millionen IOPS nicht sehr überraschen. Beeindruckender ist die äußerst geringe Zugriffslatenz, die mit herkömmlichen SSD-Techniken nicht zu erreichen ist. Selbst die schnellen Beschleunigerkarten von Fusion-io benötigen mit 15 Mikrosekunden beim wahlfreien Schreiben die zehnfache Zeit, beim Lesen liegt die Latenz sogar bei mindestens 47 Mikrosekunden. Eine Zugriffszeit von 10 Mikrosekunden gilt noch immer als Bestwert bei herkömmlichen SSDs. Aktuelle Consumer-SSDs für die SATA-Schnittstelle bringen es auf etwa 30 oder mehr Mikrosekunden.

Drei Millionen IOPs sind herausragend, aber dies ist nicht der aufregendste Teil der Demonstration [...] Der wirklich aufregende Teil ist die Fähigkeit, Latenzen von fast 1 µs für Random Reads in kleinen Blöcken zu liefern. Das ist mit NAND-Flash und heutigen Controller- und Schnittstellentechnologien einfach nicht möglich.

Dr. Zvonimir Bandic, Manager für Speicherarchitekturen in der Forschung bei HGST

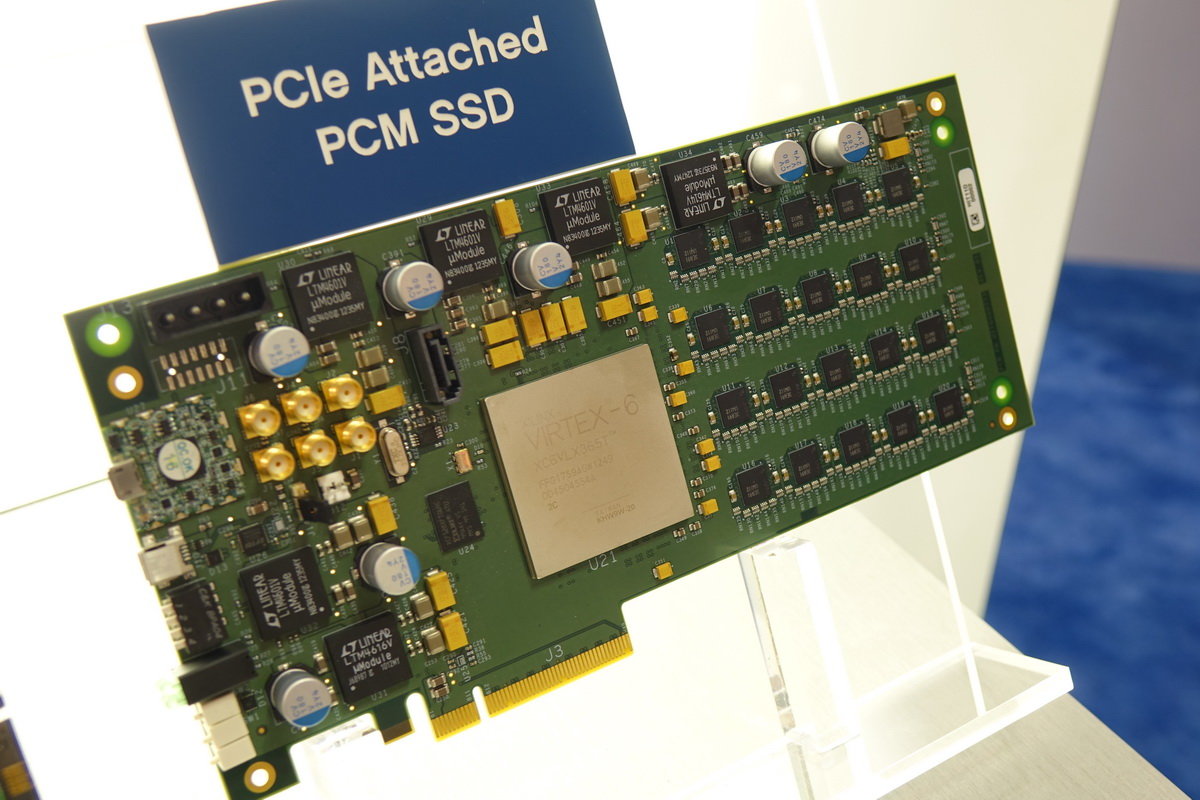

„Diese Leistung ist um Größenordnungen schneller als existierende, flashbasierte SSDs, was eine neue Klasse von blockbasierten Speichergeräten zur Folge hat“, heißt es weiter in der Pressemitteilung von HGST. Bei der für den am 6. August beginnenden Flash Summit anberaumten Demonstration werden PCM-Bausteine mit einer Kapazität von jeweils 1 Gigabit eingesetzt, die in einem 45-nm-Prozess hergestellt werden. Der Prototyp ist eine Steckkarte im Vollformat (Full-Height/Full-Length – FHFL) mit vier PCIe-2.0-Lanes.

Bekanntlich arbeiten unter anderem Samsung, Intel, Micron und IBM an Phase Change Memory. Wer die Speicherchips für HGST produziert, geht aus der Meldung nicht hervor. Micron würde sich anbieten, da der Hersteller bereits 1-Gigabit-PCM-Chips ausgeliefert hat, die in Nokia-Smartphones in Kombination mit LPDDR2-DRAM zum Einsatz kommen sollten. Jedoch ruderte Micron Anfang des Jahres in Sachen PCM zurück.

Bei SSDs gilt momentan der sogenannte 3D NAND mit Vorteilen bei den Herstellungskosten als Speicher der nahen Zukunft. Erste SSDs lieferte Samsung unter anderem mit der 850 Pro für Verbraucher. PCM könnte künftig in High-End-Enterprise-Lösungen Fuß fassen, bei denen die Leistungsfähigkeit höher als die Kosten gewichtet wird. Mit Fortschritten bei der Herstellung und der Verbreitung eines geeigneten Protokolls dürfte PCM langfristig auch in Consumer-SSDs Verwendung finden. Doch zeigt der Umstand, dass bis heute das SATA-Protokoll vorherrscht und NVMe erst allmählich seinen Weg in den Enterprise-Markt findet, dass bis dahin noch eine Menge Zeit vergehen wird.

Auf der Usenix-Konferenz FAST 2014 stellten Forscher von HGST und der University of California, San Diego, ein spezielles Protokoll für besonders kurze Latenzen mit Phase Change Memory vor.

Wie angekündigt, hat HGST einen Prototypen der neuartigen SSD-Technik auf dem Flash Memory Summit 2014 vorgeführt. Die PCIe-Steckkarte zeigt neben den Phasenwechselspeicherchips ein Virtex-6-FPGA von Xilinx.

-

HGSTs SSD-Prototyp mit Phasenwechselspeicher (Bild: pcper.com)

HGSTs SSD-Prototyp mit Phasenwechselspeicher (Bild: pcper.com)

Die Fotos von PC Perspective zeigen, dass die SSD bei wahlfreien Lesezugriffen auf 512-Byte-Blöcke mindestens 400.000 bis über 600.000 IOPS erreichte. Die versprochenen 3 Millionen IOPS werden damit nicht belegt, jedoch lag zum Zeitpunkt des Fotos die Zahl der ausstehenden Befehle (IOs) bei nur eins, mit mehreren IOs sollten deutlich mehr IOPS erreicht werden.