3D-NAND: Intel und Micron legen Grundstein für 10-TByte-SSDs

Intel und Micron haben die anstehende erste Generation des gemeinsam entwickelten 3D-NAND vorgestellt. Die TLC-Variante mit 384 Gbit bietet eine dreimal so hohe Kapazität wie aktuelle Lösungen der Konkurrenz. Mit näheren technischen Details hält sich Intel aber weiterhin bedeckt.

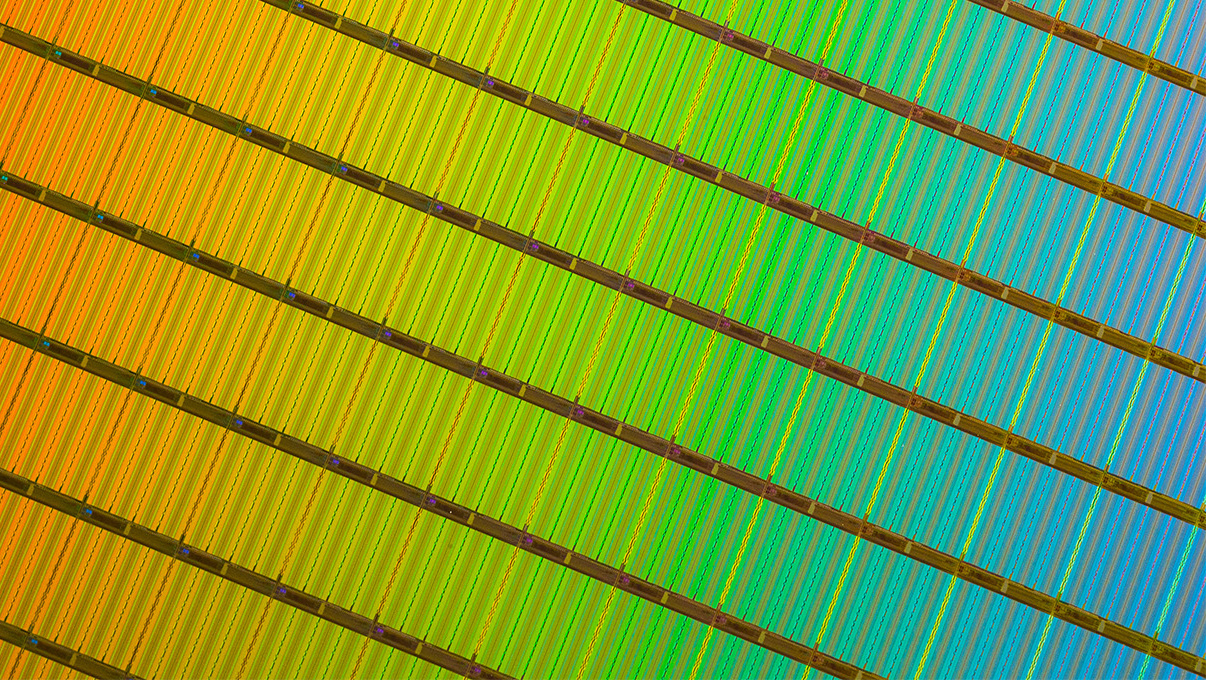

Durch eine Kombination der auch bei 2D-NAND verwendeten Floating-Gate-Technik mit einem universellen Design und optimierter Architektur haben die im Flash-Bereich unter dem Namen IMFT kooperierenden Unternehmen 3D-NAND mit der bisher größten Datendichte entwickelt. Die MLC-Variante speichert 2 Bit pro Zelle und bringt es auf 256 Gigabit pro Die. Die TLC-Version mit 3 Bit pro Zelle steigert die Kapazität auf 384 Gigabit, was dem Dreifachen bisher üblicher 2D- und 3D-NAND-Produkte mit 128 Gigabit entspricht.

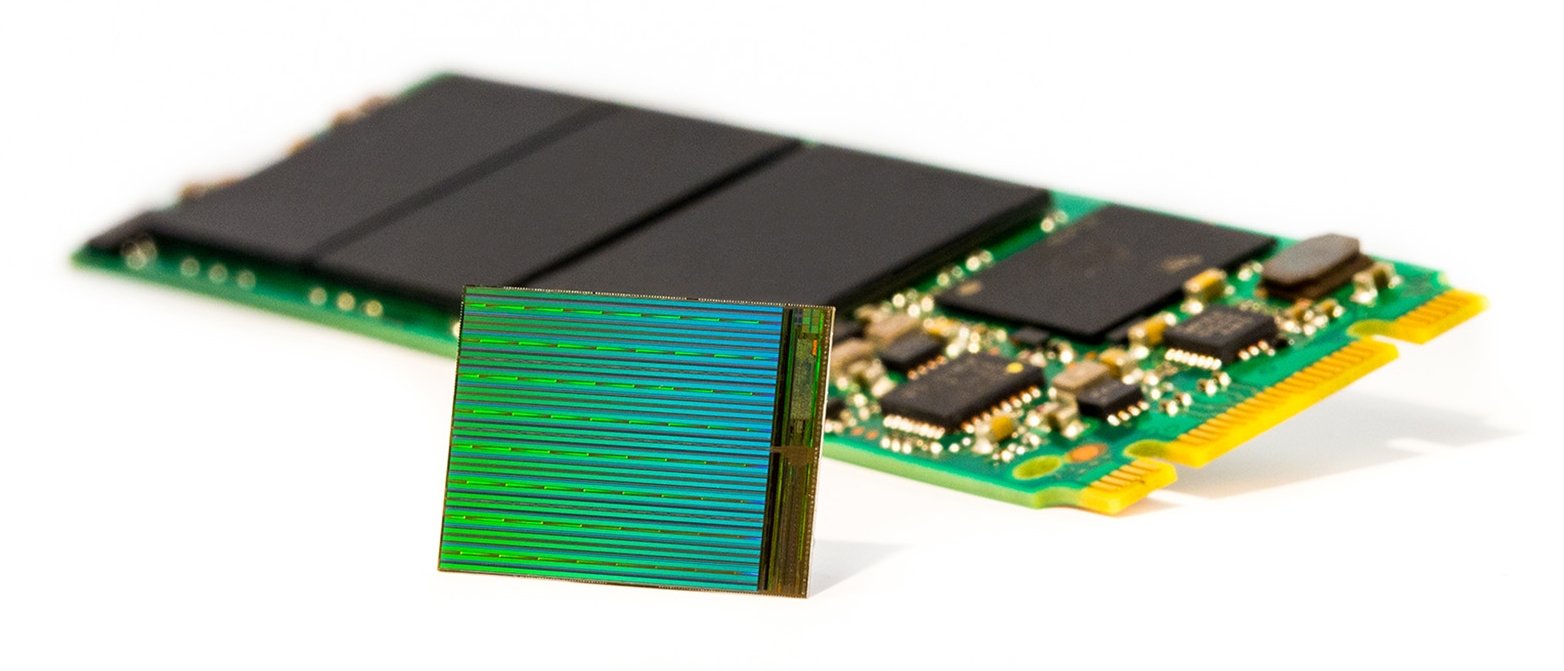

Somit werden Datenträger wie SSDs mit deutlich höherer Kapazität bei gleichbleibender Anzahl von Speicherchips ermöglicht. Der MLC-3D-NAND, von dem bereits Muster hergestellt werden, bietet 32 GByte pro Die. Kommen bis zu 16 dieser Dies in einem Chip-Package unter, bietet ein einzelner Speicherchip 512 GByte – so viel wie manche SSD. Mit der späteren TLC-Variante, von der es noch „in diesem Frühjahr“ erste Muster geben soll, sind entsprechend 48 GByte pro Die und bis zu 768 GByte pro Chip möglich.

Davon ausgehend, dass herkömmliche Consumer-SSDs derzeit bis zu 16 Chip-Packages besitzen, wären somit 12 TByte Speicher auf einer SSD realisierbar. Intel spricht lediglich von 2,5-Zoll-SSDs mit mehr als 10 TByte. Im kompakten M.2-Format sollen mehr als 3,5 TByte ermöglicht werden. Die Massenproduktion beider Varianten soll im vierten Quartal 2015 beginnen, für erste Endprodukte mit dem neuen Speicher noch in diesem Jahr wird es somit eng. Intel und Micron gehen nun selbst davon aus, dass eigene SSDs mit 3D-NAND erst 2016 erhältlich sein werden.

Zum verwendeten Herstellungsverfahren wollte Intel auch auf Nachfrage gegenüber der Presse keine Details verraten. Die vertikale Struktur von 3D-NAND ermöglicht Herstellern die Datendichte durch mehrere Zellschichten signifikant zu erhöhen, ohne Strukturbreiten zu verkleinern. Es ist davon auszugehen, dass die Strukturbreite höher als bei aktuellen 2D-NAND-Produkten liegt. Dies bietet Vorteile bei der Haltbarkeit, die durch immer enger liegende Speicherzellen abnimmt. IMFTs 3D-NAND verfügt wie Samsungs zweite Generation des V-NAND über 32 dieser übereinander liegenden Zellschichten. Beide Techniken unterscheiden sich aber grundlegend, weil Samsung auf Charge Trap Flash (CTF) statt der seit über 40 Jahren eingesetzten Floating-Gate-Technik setzt.

Vom 3D-NAND versprechen sich die Unternehmen nicht nur sinkende Kosten pro Gigabyte und höhere SSD-Kapazitäten, sondern auch Verbesserungen bei der Leistung. Durch neue Sleep-Modi, bei denen die Stromzufuhr zu nicht aktiven Zellen innerhalb eines Packages unterbunden wird, soll die Leistungsaufnahme im Standby-Modus „erheblich sinken“.

Diese 3D NAND Technologie hat das Potenzial, den Markt fundamental zu ändern. Bislang können wir bei Flash-Speichern nur einen kleinen Teil dessen überblicken, was möglich ist.

Brian Shirley, Vice President Memory Technology and Solutions bei Micron

Toshiba und SanDisk haben heute ebenfalls ihre erste kommerzielle Generation 3D-NAND für 2016 angekündigt, die zwar bereits über 48 Ebenen verfügt, aber als MLC-Variante nur 128 Gbit pro Die liefert.