Samsung Foundry: 10-nm-SRAM-Zelle 38 Prozent kleiner als in 14 nm

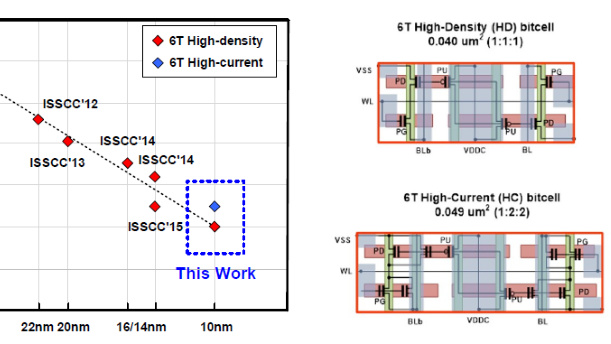

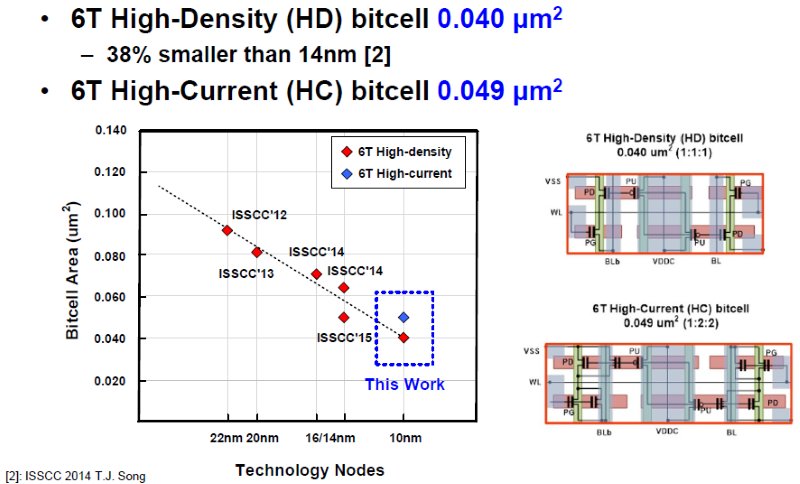

Zum ISSCC hat Samsung einige Details zur kommenden 10-nm-Fertigung preisgegeben. Die 6T-SRAM-Zelle ist 38 Prozent kleiner als noch in 14-nm-FinFET-Fertigung und belegt in der High-Density-Konfiguration eine Fläche von nur 0,040 µm².

Parallel zur High-Density-Variante (HD), also der extrem auf kleine Fläche optimierten Version, hat Samsung auch eine High-Current-Version (HC) aufgelegt, die 0,049 µm² groß ist. Die HC-Version geht mit minimalen Spannungen von 45 mV um, die HD-Variante agiert bei 130 mV. Mit der Größe der SRAM-Zelle trifft Samsung ziemlich genau die Erwartungen an die 10-nm-FinFET-Fertigung, die durch die Produkte der letzten Generationen prognostiziert wurden.

Samsung betont dabei, dass wie bereits in der aktuellen 14-nm-Fertigung nicht nur die FinFETs eingeführt und angepasst, sondern auch Interconnects verkleinert wurden. Dies ist erneut eine kleine Stichelei gegen TSMC, deren 16-nm-Fertigung im Grunde genommen einfach eine Fertigung mit bereits zuvor genutzten 20-nm-Interconnects zuzüglich neuen FinFETs ist. Dies hatte bereits die Folge, dass Samsungs für Apple gefertigter A9-SoC nur 96 mm² groß war, TSMCs Chip brachte es auf 105 mm² Fläche.

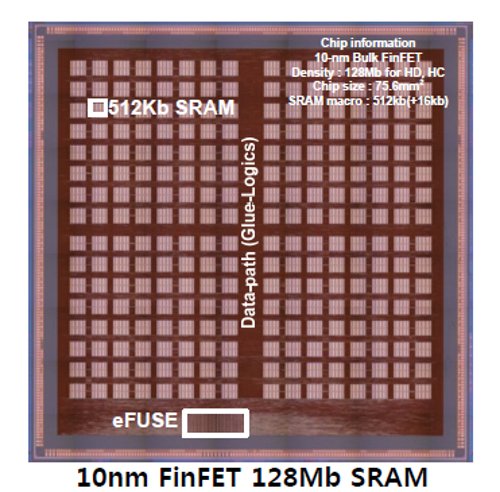

Die anstehende 10-nm-Fertigung hat aber auch ihre Tücken, erklärte Samsung zur International Solid-State Circuits Conference (ISSCC) in dieser Woche. Die Spannungen seien noch nicht attraktiv genug für einen Serieneinsatz, zudem gebe es Probleme mit erhöhten Widerständen, dessen Verhalten sich im Vergleich zur 14-nm-Fertigung nicht verbessert hat – und dies auch in Zukunft bei 7 nm nicht soll. „Man erwartet, dass mit einem neuen Verfahren alles besser wird, aber das ist nicht der Fall,“ erklärte Taejoong Song von Samsung gegenüber EETimes. Für die 128 Mb SRAM musste Samsung deshalb auf ein „Assist Adjustment System for Power, Performance, and Area Optimization“ – so auch die Thematik des gesamten Vortrags – zurückgreifen, ohne letztlich die exakten Details dazu zu verraten.

Samsungs 10-nm-Chips sind und bleiben deshalb noch einige Zeit in der Testphase. Das Tape-out diverser Testchips laufe, Produkte sind bisher aber nicht angekündigt. Welche exakten Verbesserungen die fertigen Produkte dann im Bereich der Leistung und/oder Leistungsaufnahme hervorbringen, ist deshalb noch nicht bekannt. Die 38 Prozent Einsparung in der Fläche gelten nur für SRAM, der in einem Smartphone-SoC nur etwa 30 Prozent der Fläche ausmacht. Viele andere Bausteine können nicht vergleichbar gut optimiert werden, sodass die Verbesserungen des Gesamtpakets am Ende in geringeren Prozentzahlen beim Vergleich mit einem etwaigen Vorgänger resultieren.