Western Digital: BiCS4-3D-NAND nutzt 96 Layer und TLC oder QLC

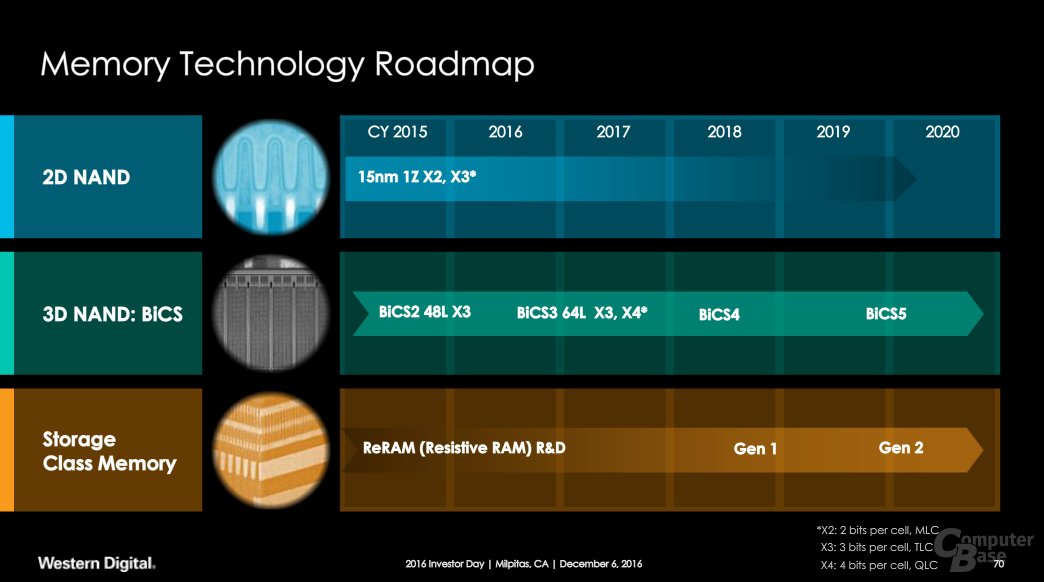

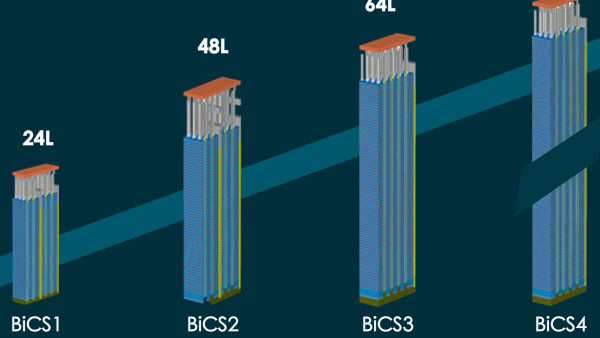

Western Digital und Toshiba haben gemeinsam die nächste Generation 3D-NAND-Flash-Speicher entwickelt. BiCS4 heißt die inzwischen vierte Generation, bei der die Zahl der übereinander liegenden Zellschichten von 64 (BiCS3) auf 96 Layer steigt. Geplant sind TLC-Varianten mit 3 Bit sowie erstmals QLC-Flash mit 4 Bit pro Zelle.

Die Ankündigung der erfolgreichen Entwicklung von BiCS4 übernimmt Western Digital. Demnach sollen bereits in der zweiten Jahreshälfte Samples für OEM-Kunden bereitstehen. Der Beginn der Serienfertigung („initial production“) wird aber erst für 2018 angepeilt. Den Anfang sollen wie schon bei BiCS3 256-Gigabit-Chips machen. Geplant ist aber eine „Reihe von Kapazitäten“, die auch erste Terabit-Chips (1.024 Gigabit) und vermutlich 512-Gigabit-Chips als Zwischenschritt beinhaltet.

QLC-Flash für die Terabit-Klasse

Spätestens bei der Terabit-Variante ist der Einsatz einer QLC-Architektur (Quadruple-Level Cell) mit vier Bit pro Speicherzelle zu erwarten. Das Debüt dürfte dagegen mit TLC-Flash mit drei Bit pro Zelle (Triple-Level Cell) erfolgen. Die weitere Erhöhung der Zellschichten birgt Potenzial für mehr Kapazität bei gleicher Chipfläche oder aber bei gleicher Kapazität kleinere Chips.

Dies soll vor allem die Kosten pro Bit senken, obgleich die zusätzlichen Schichten mehr Arbeitsschritte in der Fertigung bedeuten. Der QLC-NAND wird aber voraussichtlich deutlich weniger Schreibzyklen überdauern. Toshiba hatte vor knapp zwei Jahren bereits eine Beschränkung auf Archiv-Medien, die selten beschrieben werden, angedeutet.

Vorerst volle Fahrt für BiCS3

Die Partner hatten im Vorfeld erklärt, dass 3D-NAND erst seit BiCS3 und 64 Layern kostengünstig zu produzieren ist. Die ersten beiden Generationen waren nur in geringer Auflage hergestellt worden. Mit BiCS4 wollen die Unternehmen ihren Kunden „die höchste 3D NAND Speicherkapazität, Leistung und Zuverlässigkeit zu attraktiven Kosten“ anbieten, erklärte Dr. Siva Sivaram, der Executive Vice President of Memory Technology bei Western Digital.

Zunächst gilt es aber, die Produktion der gerade erst in den Markt eingeführten BiCS3-Generation hochzufahren. Noch in diesem Jahr soll der BiCS3-Ausstoß mehr als 75 Prozent der 3D-NAND-Produktion der Unternehmen erreichen, so das Ziel. Die mit Toshiba kombinierte Produktionsmenge an 64-Layer-3D-NAND könnte zumindest aus Sicht von Western Digital in diesem Jahr größer als bei der Konkurrenz ausfallen.

In diesem Jahr ist die Konkurrenz auf Augenhöhe

Intel und Micron, die Flash-Speicher gemeinsam im Joint Venture IMFT herstellen, sind ebenfalls bereits bei 64-Layer-3D-NAND angekommen. Die erste Client-SSD in Form der Intel SSD 545s wird bereits mit dem laut Micron kleinsten 256-Gbit-NAND-Flash bestückt. Zuvor hatte Toshiba die OEM-SSD-Serie XG5 mit BiCS3 vorgestellt, Western Digital will die SSD-Serien WD Blue sowie SanDisk Ultra mit dem neuen 3D-NAND ausrüsten. Zur Computex gab es diverse weitere Ankündigungen von SSDs mit BiCS3-Flash.

Samsungs technischer Vorsprung schwindet. Der Konzern hatte bereits 2013, Jahre vor der Konkurrenz, 3D-NAND in Serie gefertigt. Doch bei der vierten Generation des V-NAND gibt es Verzögerungen. Statt zum Jahresende 2016 erfolgte der Start der echten Massenfertigung erst kürzlich. Statt 512-Gbit-Chips gibt es vorerst ebenfalls 256 Gigabit als 3D-TLC-Flash mit 64 Lagen. Allerdings überraschte Samsung mit einer hohen Datenrate von 1.000 Mbit/s und dürfte bei der Leistung abermals in Führung liegen. SK Hynix als vierter im Bunde der Flash-Hersteller will im zweiten Halbjahr mit seiner vierten Generation (3D-V4) auf 72 Layer erhöhen.

96 Layer sind auch bei der Konkurrenz geplant

Erst vor einigen Wochen hatte SK Hynix die Arbeiten an 3D-NAND mit 96 und sogar 128 Layern bestätigt. Ein Zeitplan wurde aber noch nicht veröffentlicht. Samsung hat ebenso „mehr als 90 Layer“ für eine nachfolgende Generation mit Chips der Terabit-Klasse in Aussicht gestellt. Und auch bei Intel und Micron ist eine weitere Steigerung bei den Zellebenen zu erwarten.

Mittlerweile hat auch Toshiba eine Pressemitteilung herausgegeben. Darin liegt der Fokus auf die erste Umsetzung der QLC-Technik. Nach Angaben des Unternehmens wurde damit die weltweit höchste Speicherkapazität von 768 Gigabit respektive 96 Gigabyte pro Die erreicht. Diese Speicherkapazität hatte Micron schon einmal auf einer Roadmap präsentiert, doch bis heute keine derartigen Chips vorgelegt.

Bereits in diesem Monat sollen Prototypen an Hersteller von SSDs und SSD-Controllern zur Evaluierung verschickt worden sein.

Achieving QLC technology posed a series of technical challenges, as increasing the number of bit-per-cell by one within same electron count requires twice the accuracy of TLC technology. Toshiba Memory has drawn on its advanced circuit design capabilities and industry-leading 64-layer 3D flash memory process technology to create the QLC 3D flash memory.

Toshiba

Mit dem neuen Speicher werden bis zu 1,5 Terabyte in nur einem Chip-Package möglich, wenn 16 der Dies übereinander gestapelt werden. Toshiba sieht den Einsatz des QLC-3D-NAND sowohl für Consumer-SSDs und Speicherkarten als auch für Enterprise-SSDs vor. Auf dem Anfang August stattfindenden Flash Memory Summit in Kalifornien will Toshiba Musterchips präsentieren.

In einer weiteren Pressemeldung spricht Toshiba explizit eine 512-Gigabit-Version an. Ferner ist von einer Kapazitätssteigerung in Relation zur Chipgröße von 40 Prozent gegenüber dem 64-Layer-NAND die Rede.

Going forward, Toshiba Memory Corporation will apply its new 96-layer process technology to larger capacity products, such as 512 gigabit (64 gigabytes) and 4-bit-per-cell (quadruple-level cell, QLC) technology, in the near future.

The innovative 96-layer stacking process combines with advanced circuit and manufacturing process technology to achieve a capacity increase of approximately 40% per unit chip size over the 64-layer stacking process. It reduces the cost per bit, and increases the manufacturability of memory capacity per silicon wafer.

Toshiba