Quad-Level Cell: Intel und Micron liefern ersten QLC-3D-NAND für SSDs

Mit QLC-NAND-Flash steht eine neue Klasse von 3D-NAND für SSDs und Co. bereit. Intel und Micron sind die ersten Hersteller, die die Verfügbarkeit von QLC-Flash angekündigt haben. Mit vier Bit pro Zelle wird die Speicherdichte erhöht. Die Micron 5210 ION ist die erste SSD-Serie mit QLC-NAND.

QLC-Flash ermöglicht 1 Terabit pro Chip

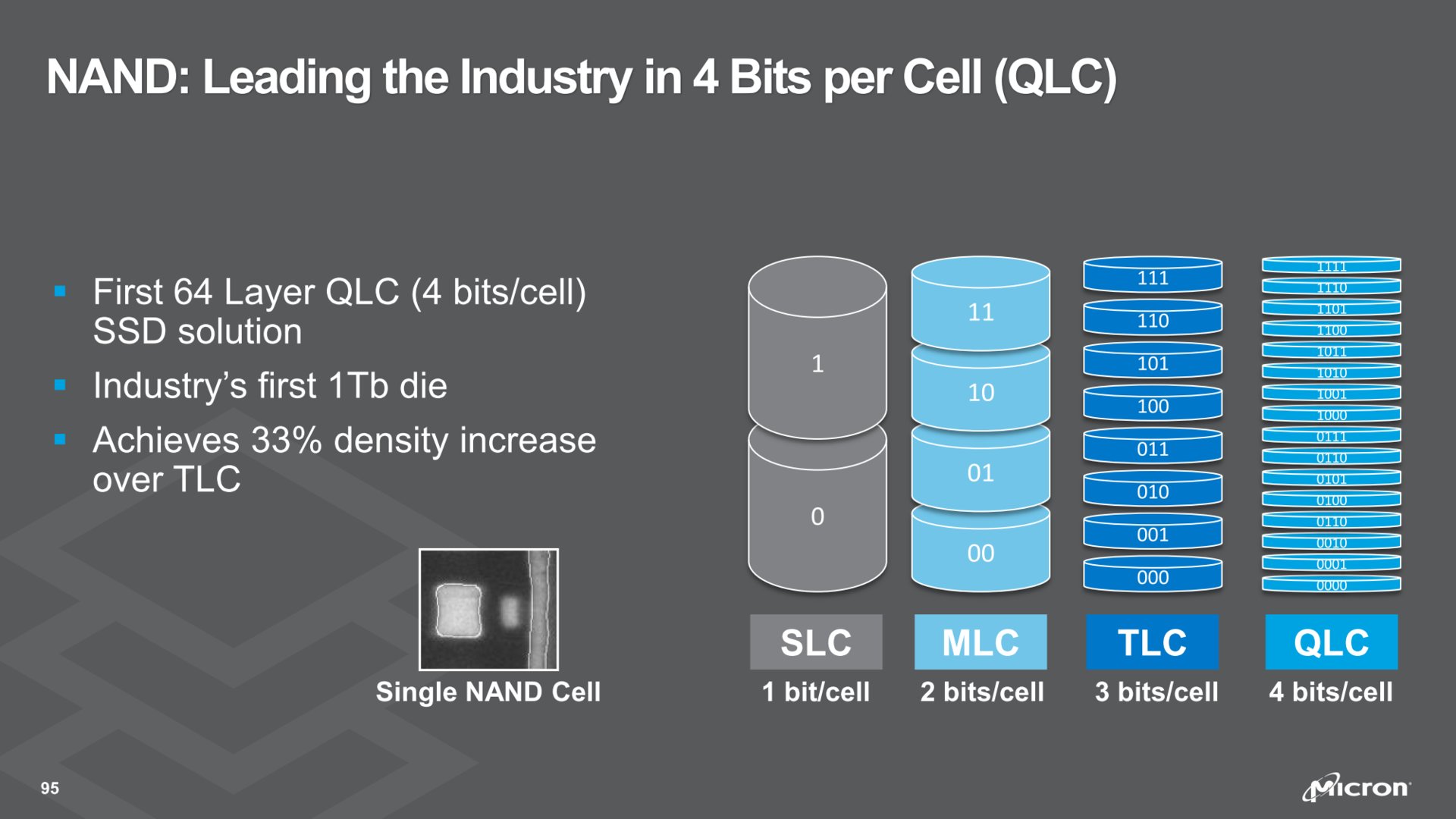

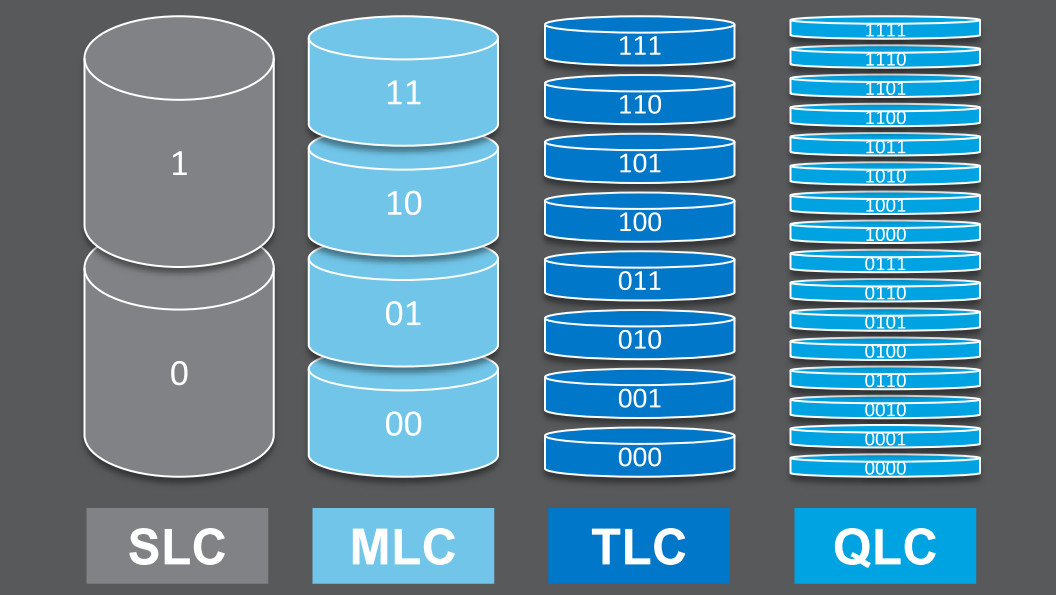

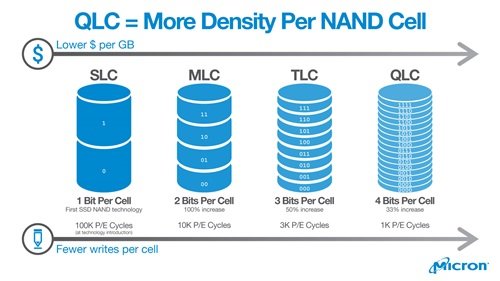

Das Hinzufügen eines weiteren Bit pro Speicherzelle ist eine Maßnahme, um die Speicherdichte pro Chip und Wafer zu erhöhen und damit die Kosten pro Bit zu senken. Nach SLC mit einem Bit, MLC mit zwei Bit und TLC mit drei Bit pro Zelle ist QLC (Quadruple- oder Quad-Level Cell) der nächste logische Schritt. Der Sprung von drei auf vier Bit bedeutet eine Kapazitätssteigerung von einem Drittel gegenüber TLC-NAND.

Micron hatte im Vorfeld bereits einen Wafer mit QLC-Flash mit 512 Gigabit pro Die gezeigt. 512 Gigabit entspricht auch dem letzten Stand bei TLC-Flash. Im QLC-Design ist dieses Speichervolumen allerdings mit nochmals kleineren Chips möglich. Im Fokus der heutigen Ankündigung von Intel und Micron steht aber der erste Terabit-Flash: Dank QLC-Technik soll die Speicherkapazität auf 1.024 Gigabit respektive 128 Gigabyte pro Die verdoppelt werden. Die Chips müssten hierfür allerdings wachsen, denn die 33 Prozent mehr Speicherplatz von TLC auf QLC genügen dafür nicht. Wie groß der neue QLC-Flash ausfällt, haben die Partner aber noch nicht verraten.

Mehr Bit pro Zelle macht das Speichern komplizierter

Wie so oft hat die Sache einen Haken: Mit dem zusätzlichen Bit steigt die Komplexität des 3D-NAND nochmals an. NAND-Flash speichert die Informationen über unterschiedliche Spannungen (Voltage Level). Waren bei SLC-NAND nur zwei Spannungen für ein Bit (0 und 1) nötig, verdoppelte sich die Zahl bei 2-Bit-MLC bereits auf vier Voltage-Level, bei TLC waren es dann acht und bei QLC sind es nun ganze 16 unterschiedliche Spannungen, die pro Speicherzelle vorliegen. Dies hat nicht nur die Folge, dass das Schreiben der Daten aufwendiger und langwieriger ist und entsprechend die Leistung sinkt, sondern beeinflusst auch die Haltbarkeit, die anhand der möglichen Schreibzyklen (P/E Cycles) eingestuft wird.

In puncto Leistung soll der QLC-Flash dank eines 4-Plane-Designs nicht viel langsamer als TLC-Flash im 2-Plane-Design agieren. Der Einsatz eines Pseudo-SLC-Cache hat bereits TLC-SSDs beschleunigt und dürfte bei QLC-SSDs erst Recht zum Standard werden.

Bei den möglichen Schreibzyklen ist der Rückschritt aber unverkennbar. Von den 3.000 P/E-Zyklen des TLC-Flash bleiben beim QLC-Design nur noch 1.000 P/E-Zyklen übrig. Bei einem Drittel mehr Speichervolumen reduziert sich die Haltbarkeit folglich auf ein Drittel.

Die Befürchtung, dass sich QLC-NAND dadurch nur für einmaliges Schreiben und anschließendes Abrufen von Daten – auch Write-Once, Read-Many (WORM) genannt – eignet, ist aber übertrieben. Denn 1.000 Schreibzyklen genügen noch für viele Einsatzgebiete und auch im heimischen PC werden Daten viel häufiger gelesen als geschrieben. Dennoch soll sich der Einsatz von QLC vornehmlich auf Gebiete mit Fokus auf Leseoperationen beschränken.

Die erste SSD mit QLC-NAND: Micron 5210 ION

Das Debüt gibt der QLC-Speicher in der Enterprise-SSD-Serie Micron 5210 ION, die mit höherer Leistung und Effizienz vor allem Enterprise-HDDs den Kampf ansagen soll. Zu den 2,5-Zoll-SSDs mit SATA-Schnittstelle hat Micron noch keine näheren Details verraten. Ein Dokument (PDF) deutet aber Durchsatzraten von 540 MB/s respektive 360 MB/s beim sequenziellen Lesen/Schreiben sowie 90.000/5.000 IOPS beim wahlfreien Lesen/Schreiben an.

Um den Controller ranken sich Spekulationen, dass es wie schon bei den TLC-Modellen der 5200-Serie der Marvell 88SS1074 mit angepasster Firmware sein könnte. Der Einsatz eigener Controller mit Technik aus der Übernahme von Tidal sei dagegen unwahrscheinlich.

Die 5210 ION soll mit Speicherkapazitäten von 1,92 TB bis 7,68 TB angeboten werden. Geschäftskunden von Micron sollen schon jetzt mit ersten 5210-SSDs versorgt werden. Der breite Marktstart wird aber erst im Herbst erwartet. Weitere SSD-Serien mit QLC-Flash sollen folgen und auch andere Schnittstellen und noch größere Speicherkapazitäten seien vorgesehen.

QLC noch Teil der 64-Layer-Generation

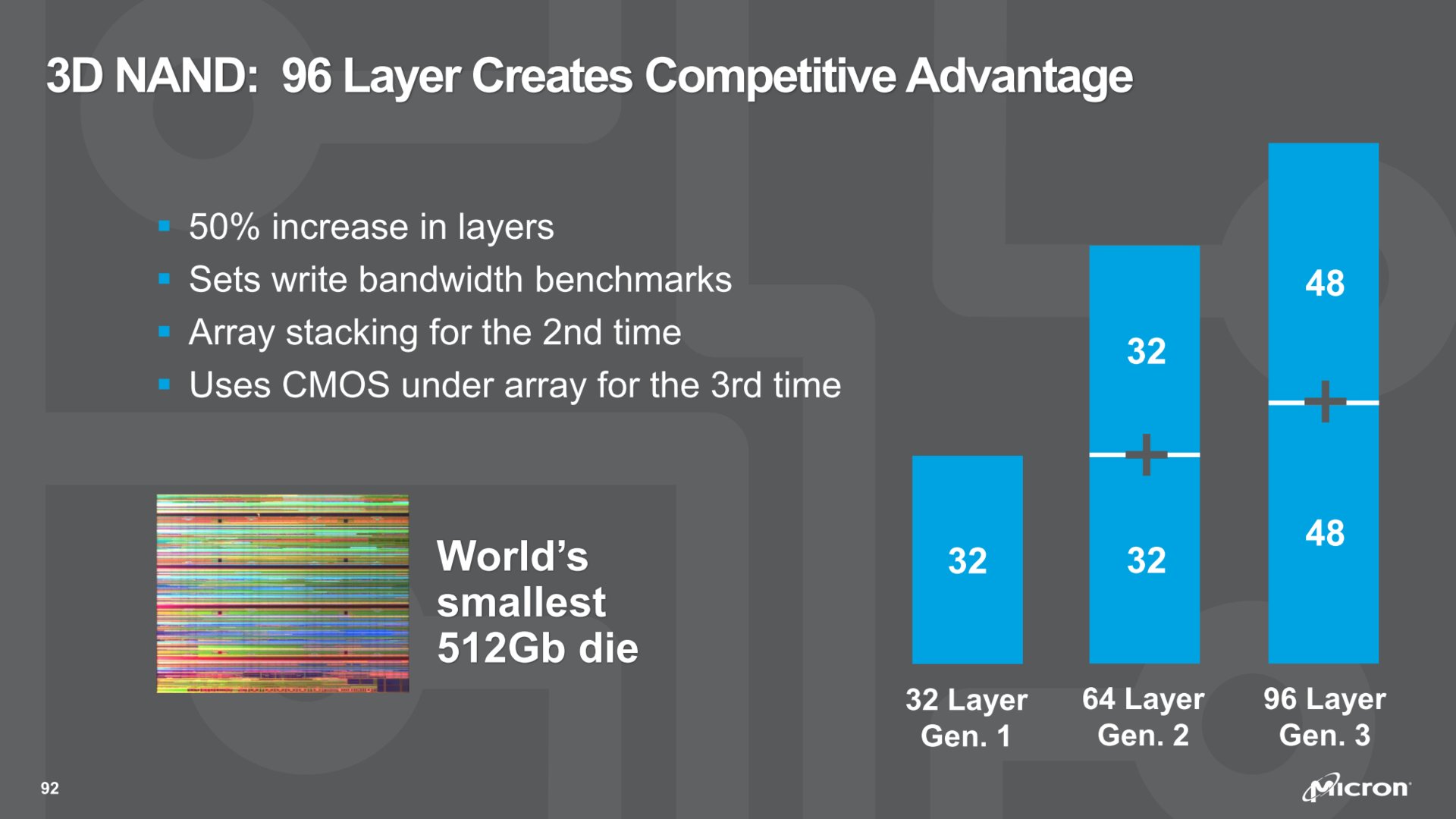

Intel und Micron läuten die QLC-Ära allerdings nicht mit einer neuen Generation 3D-NAND ein, sondern bleiben zunächst bei der zweiten Generation mit 64-Layer-Architektur, die 64 Ebenen von Speicherzellen besitzt. Im Grunde handelt es sich um ein verdoppeltes 32-Layer-Design, denn es werden praktisch zwei 32-Layer-Stapel übereinander gestapelt, was die Hersteller Array Stacking nennen. Diese Methode ist offenbar wirtschaftlicher als die Herstellung eines nativen 64-Layer-Chips.

Die CMOS-Schaltkreise (CMOS Logic) liegt dabei nicht neben, sondern in einer weiteren Schicht unter den Speicherzellen, was Chip-Fläche spart. Diese CMOS Under Array (CUA) genannte Technik hatten Intel und Micron den Konkurrenten voraus, womit bereits der 64-Layer-TLC-Flash bei der Speicherdichte (Gigabit pro Wafer) führend ist. Bei der dritten Generation im 96-Layer-Design sollen CUA und Array Stacking erneut Verwendung finden.

Auch die Konkurrenz plant mit QLC

QLC-3D-NAND mit 1 Terabit pro Die wird auch der Weltmarktführer Samsung auf den Markt bringen. Nach letztem Stand soll in diesem Jahr eine SSD mit 128 TByte Speicherplatz mit dem neuen Speicher der fünften Generation V-NAND (V5) realisiert werden. Bei Toshiba und Western Digital soll QLC-Flash zunächst in der dritten Generation (BiCS3 X4) und später in der vierten Generation (BiCS4 X4) Einzug halten.

Microns 4. Generation 3D-NAND wird die erste ohne Intel

Die 96-Layer-Generation wird die dritte und zugleich letzte NAND-Flash-Generation sein, die Micron in Partnerschaft mit Intel entwickelt und produziert. Denn wie schon seit Januar offiziell bekannt ist, endet danach die Kooperation und Micron wird fortan 3D-NAND in Eigenregie herstellen.

Das erste Produkt der Eigenständigkeit soll die vierte 3D-NAND-Generation werden. Wie viele Layer diese besitzen wird, ist noch unklar, doch gelten 128 Layer als nächster logischer Schritt. Die Architektur wird sich allerdings radikal verändern: Micron kündigt ein „einzigartiges Design“ an, das CUA mit Charge-Trap-Flash-Technik kombiniert und die sogenannte Replacement Gate (RG) Technology zur Herstellung nutzt.

Intel und Micron nutzen bisher als einzige NAND-Flash-Hersteller ein Floating-Gate-Prinzip für ihren 3D-NAND, während alle anderen Hersteller (Samsung, SK Hynix, Toshiba/Western Digital) stattdessen die Charge-Trap-Technik verwenden. Künftig zählt also auch Microns 3D-NAND zumindest grundlegend zur letzteren Art.

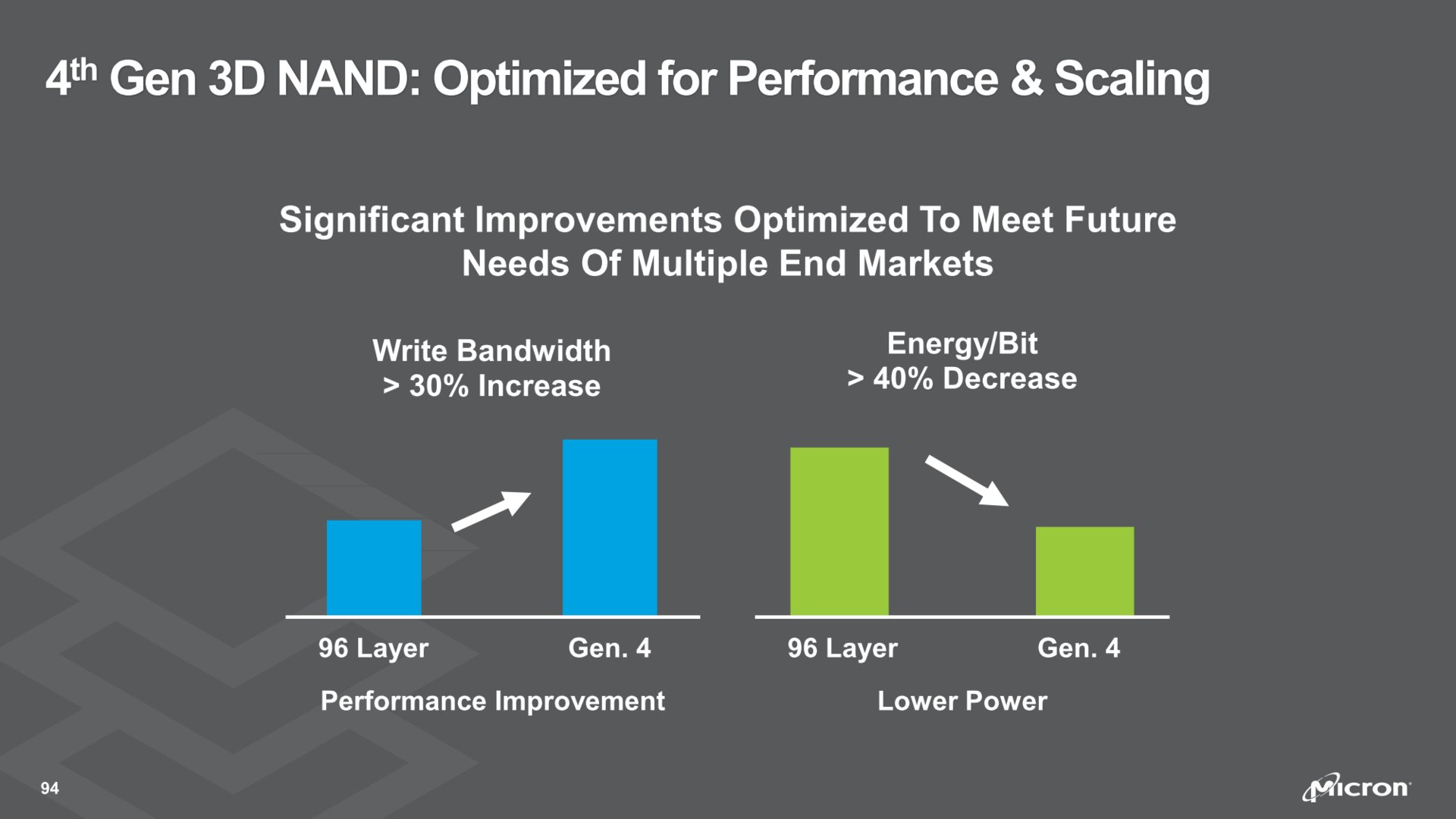

Micron verspricht mit der vierten Generation 3D-NAND nicht weniger als eine Steigerung der Schreibrate um mehr als 30 Prozent gegenüber der dritten Generation (96 Layer). Parallel soll die Energieeffizienz steigen. Die Leistungsaufnahme pro Bit soll um über 40 Prozent sinken, so die Prognose. Das Ziel von Micron ist es, in puncto Leistung und Die-Größe die Branche anzuführen.