Vor-Ort-Besuch: Einblicke in Intels Test- und Packaging-Prozess in Malaysia

Millionen an Chips, beispielsweise für Core- und Xeon-Prozessoren, durchlaufen Intels Test- und Packaging-Prozess in Malaysia – Woche für Woche. ComputerBase durfte mehrere Einrichtungen besuchen und in Augenschein nehmen, wie der andernorts gefertigte Chip vom Wafer auf das Packaging kommt und wie es dann weitergeht.

Auf Packaging-Tech-Tour bei Intel

Packaging steht schon länger im Fokus der Unternehmen, wenngleich das Thema medial erst kürzlich übergekocht ist. Kein Wunder, denn mit immer mehr Multi-Chip-Designs ist Packaging, also die Integration von einem respektive mehreren Chips auf einem Träger-PCB, mitunter das Nadelöhr geworden, das die Hersteller vor immer größere Herausforderungen stellt.

Packaging wird zum Erfolgsfaktor

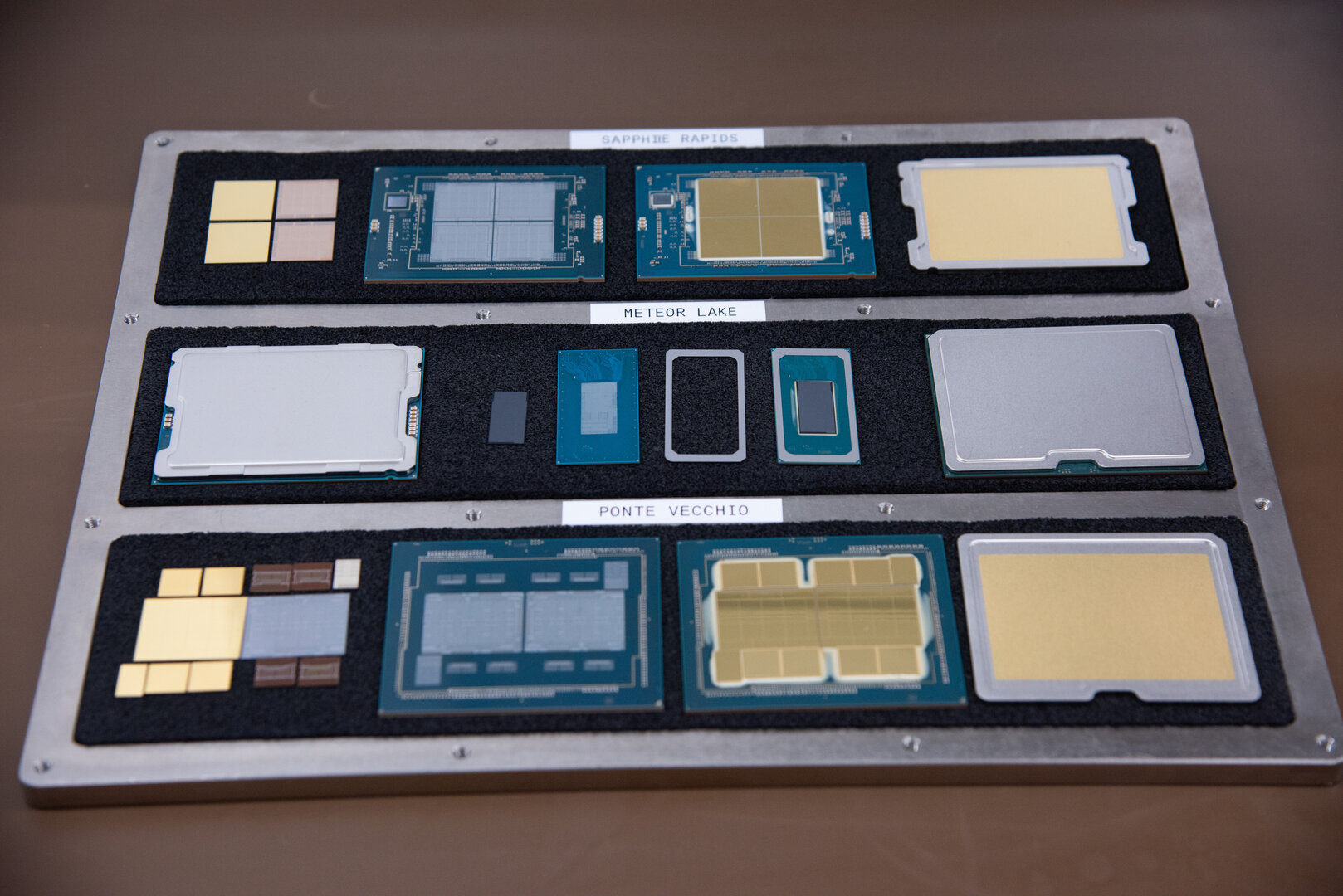

Vor allem bei speziellen Beschleunigern wie Intels Ponte Vecchio, den H100/GH200-GPUs von Nvidia oder AMDs Instinct-MI300X-Serie.

Aber nicht nur dort: Ryzen oder RDNA 3 setzen im Endkundensegment schon heute auf ein – teils gestapeltes – Multi-Chip-Modul, Intel wird die Core-(Ultra-)Serie mit Meteor Lake gegen Ende des Jahres darauf umstellen, was den Bedarf an Einrichtungen für das „Advanced Packaging“ deutlich steigern wird. Und die seinerzeit geplanten Neubauten sowohl von TSMC als auch Intel sind dafür (zu) spät dran. Genug Packaging-Kapazitäten vorhalten zu können, wird in Zukunft ein entscheidender Faktor sein.

Eine Einladung, aber kein Freibrief

Da das Thema so heiß ist und auch Intels zukünftige Produkte viel mehr mit dem Thema Packaging gemein haben, hat sich der Hersteller für eine besondere Tech-Tour entschieden. Statt nur in Konferenzräumen ohne Fenster in Powerpoint-Präsentationen darüber zu reden, hat Intel Journalisten aus aller Welt direkt in die Anlagen gelassen, die auf Penang Island (Bundesstaat Penang) und im Bundesstaat Kulim, beides Malaysia, stehen. ComputerBase gehörte dazu.

Natürlich kam die Einladung keinem Freibrief gleich. Was man vor Ort sah und erfuhr, durfte man erzählen, eigene Bilder waren aber nicht erlaubt. Diese stellte Intel bereit, natürlich nachdem die Rechtsabteilung darüber gesehen hatte, um auch ja keine Geheimnisse zu verraten. Doch selbst bei den bereitgestellten Bildern gab es am Ende noch kleinere Probleme, denn trotz tausender überklebter Typenschilder in den Einrichtungen und vielen Versteckspielchen waren offenkundig immer noch Informationen zu erhaschen, sodass ein paar Bilder am Ende noch zurückgezogen wurden.

Davon unabhängig gestattete die Tour der Redaktion einen Blick in diesen Fertigungsschritt wie nie zuvor. Was genau „Packaging“ und „Testing“ bedeutet, erfuhr ComputerBase erstmals vor Ort und erlebte auch den Unterschied zwischen „Packaging“ und „Packaging“ und den Rattenschwanz, der sich daran anschließt, hautnah.

Über 50 Jahre Intel in Malaysia

Über 50 Jahre ist Intel in Malaysia vertreten, damals war die Freihandelszone im malaysischen Bundesstaat Penang gerade ins Leben gerufen worden.

Aus den seinerzeit 100 Mitarbeitern sind im Land inzwischen 15.000 geworden, 98 Prozent sind aus Malaysia – und über 40 Prozent sind Frauen. Intel hat hierbei einen ziemlich großen Einfluss und vor allem auch viele weitere Unternehmen angelockt, aus den zehn Firmen vor 50 Jahren sind inzwischen 400 geworden.

Wenn man sich vom Flughafen auf Penang Island nach Norden in Richtung George Town bewegt, merkt man ganz schnell, dass quasi die gesamte Branche vertreten ist. In direkter Nachbarschaft finden sich Unternehmen wie Osram, Infineon, Bosch oder AMD. Und direkt im Herzen sitzt Intel.

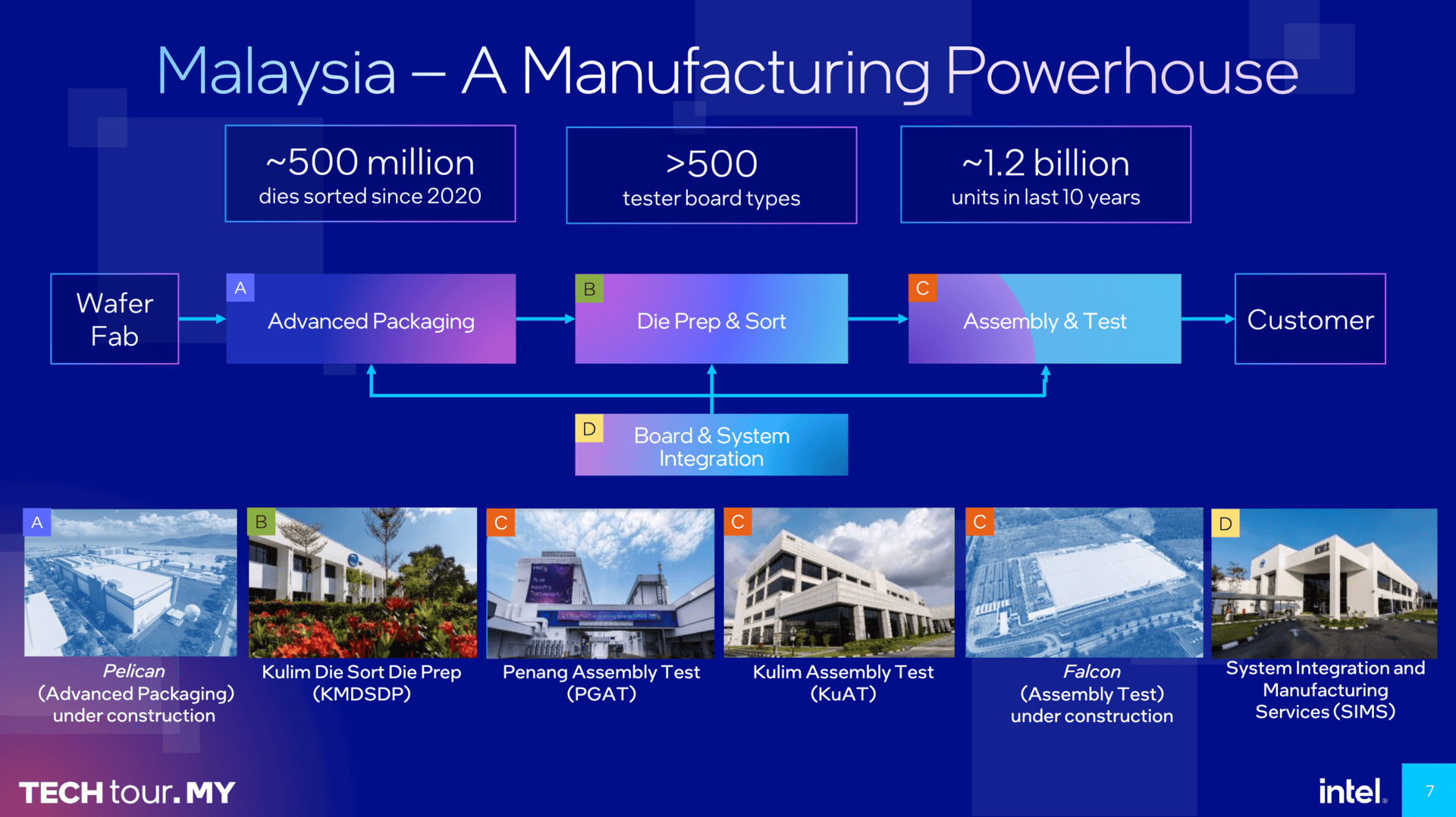

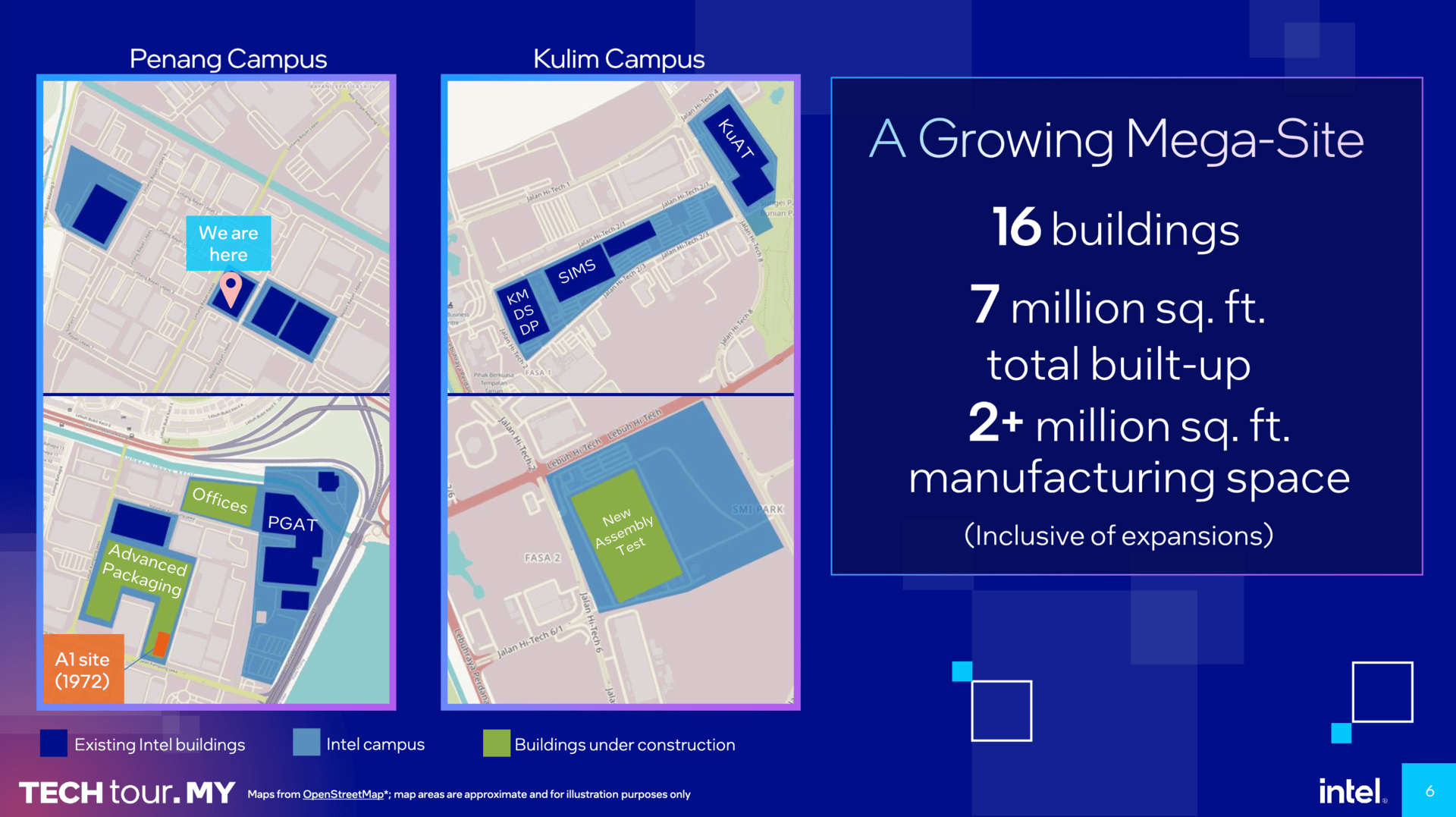

PGAT, KM1 und KM2

Der Komplex auf der Insel Penang hört auf den Namen Intel Penang Assembly and Test (PGAT). Diese Anlage umfasst in typischer Intel-Manier mehrere Gebäude, beispielsweise einen Komplex mit PG14, PG15 und PG16, dann aber auch etwas weiter nördlich PG8 und PG9 plus Anhang. Die Google-Maps-Suche zeigt die Standorte ziemlich gut an und verdeutlicht so schnell, welchen Fußabdruck Intel hier in Malaysia doch bereits hat. Und dort, wo das ursprüngliche erste Gebäude stand, wird aktuell die Advanced-Packaging-Fabrik, Codename Pelican, hochgezogen. Sie macht schon von der Straße aus etwas her, obwohl sie sich erst im Rohbau befindet.

Weitere Einrichtungen von Intel in Malaysia stehen im Bundesstaat Kulim (KM1, KM2 usw.), sprichwörtlich nur einen Steinwurf entfernt auf der Festlandseite. Hier entsteht aus der ehemaligen Panasonic-Solar-Fabrik Intels neue Mega-Einrichtung für Assembly und Test, Codename Falcon. Und die wiederum liegt in unmittelbarer Nähe von Infineons großen Ausbauten, keine 2 km weiter hatte Infineon hier zuletzt noch einmal Geld nachgeschoben.

Packaging vs. Advanced Packaging

Intel betont bereits heute regelmäßig, der Hersteller zu sein, der die größte Packaging-Kapazität hat. Doch Packaging ist nicht gleich Packaging, selbst Intel unterscheidet inzwischen zwischen dem einfachen Packaging, also quasi das Packen eines Chips auf ein Substrat/PCB, und dem „Advanced Packaging“ mit hochgerüstetem Interposer (Foveros), multiplen Chips und mehr.

Letzteres kann in Malaysia aktuell eben noch gar nicht umgesetzt werden, New Mexico geht im nächsten Jahr als Erstes dafür online, Malaysia erst 2025. Foveros wird derzeit nur in Oregon bepackt, das fertige Konstrukt dann aber für sein PCB/Substrat und den Versand wiederum nach Malaysia geschickt.

Meteor Lake kommt in Zukunft in Malaysia also schon „advanced gepackt“ an, also alle einzelnen Tiles sind auf dem Foveros-Tile verdrahtet. In Malaysia geht es von der Rolle dann aufs FC-BGA-Package. Packaging kann vieles bedeuten.

Das packt Intel in Malaysia

Sechs große Schritte durchläuft ein Chip derzeit in der Assembly-Einrichtung, je nach Modell gibt es stellenweise aber auch Wiederholungen einzelner Teilschritte und leichte Abweichungen. Die sechs Schritte umfassen:

- Chip attach: Dies auf PCB/Interposer (Substrat)

- Epoxy: Epoxidharz zwischen Die und Substrat

- Lid attach for assembly: Installation „Heatspreader“

- Burn-in-Test: Stresstest unter Volllast

- Test: Weitere Tests

- Platform performance validation (PPV): „Binning“

ComputerBase im Bunny Suit im Reinraum

Nicht das erste Mal hatte der vor Ort anwesende ComputerBase-Redakteur einen sogenannten Bunny Suit für die Reinräume an, doch das erste Mal stand er in einer Packaging-Einrichtung in Malaysia. Da ein Ungeübter viel zu lange brauchen würde, diesen Anzug anzulegen, bekam jeder (!) Besucher einen lokalen „Anzieher“. Dieser half einem ziemlich flott hinein, denn der strenge Zeitplan sollte nicht schon am ersten Punkt zerfallen. Und dann ging es auch direkt los.

Tag 1: Entlang der Fertigung im PGAT

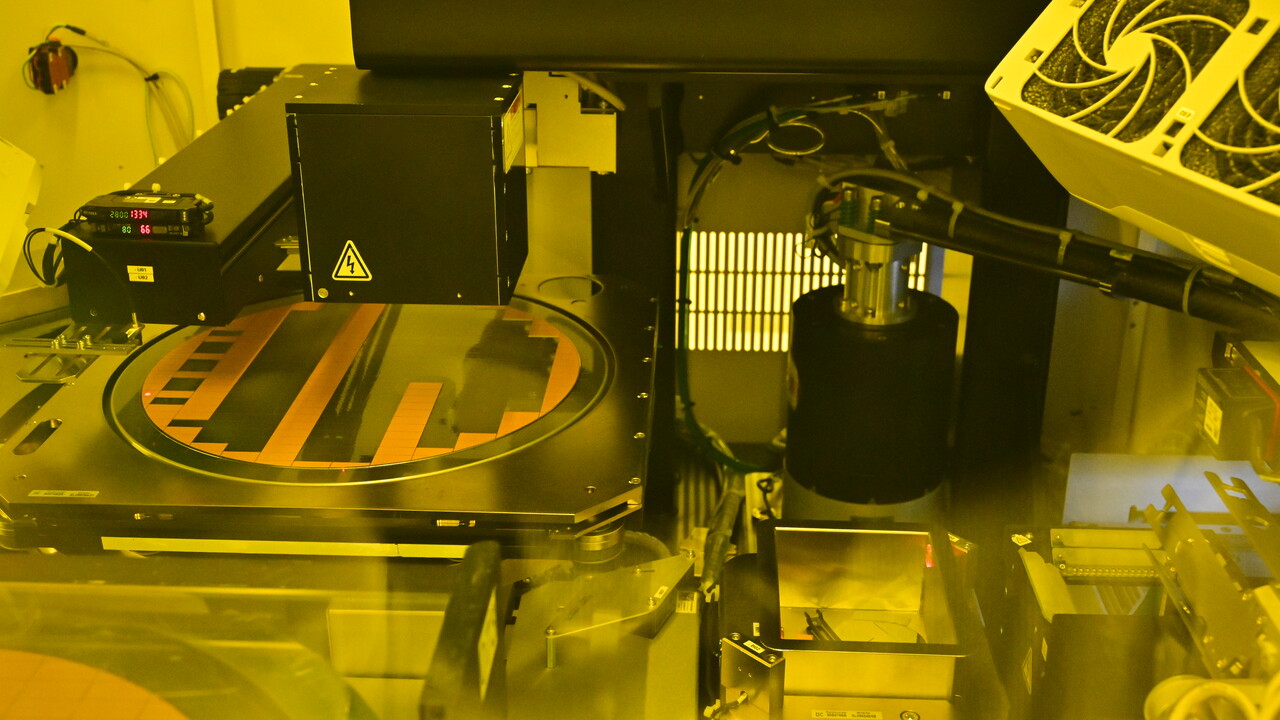

Die erste Tour führte durch das PGAT und folgte dem beschriebenen Prozess. Dementsprechend war „Die attach“, also das Aufbringen des CPU-Dies auf das Substrat, live in Aktion zu sehen. Im vorliegenden Fall wurden von vier Rollen die vier Chips von Sapphire Rapids-XCC auf das Package gebracht. Dabei wurde das erste Mal klar, dass dieser Prozess bei so einer großen CPU nicht in Sekundenbruchteilen vonstatten geht, sondern Zeit dauert.

Anschließend wurden im 2. Schritt („Epoxy“) die Lücken zwischen den Lötpunkten von Die und Substrat aufgefüllt, was Stabilität bietet, aber auch der Wärmeabfuhr zugute kommt. Je nach Chipgröße kommen unterschiedliche Verfahren zum Einsatz. Das einfachste ist, auf einer der vier Seiten eines Dies das Epoxidharz aufzutragen. Der Kapillareffekt sorgt dafür, dass sich die anfangs flüssige Substanz unterhalb des Dies bis zur anderen Seite verteilt, überflüssige Reste werden abgesaugt. Bei großen Chips kann es aber nötig sein, dass um den Die quasi ein „U“ gezeichnet wird, also von drei Seiten das Epoxy unter dem Chip verteilt wird.

Weiter ging es mit dem dritten Schritt, der ebenfalls unterschiedlich gehandhabt werden kann: Der Installation eines „Deckels“ („Lid attach for assembly“). TIM, also Wärmeleitpaste, und ein Heatspreader sind gängige Lösungen, alternativ kommt Indium bei verlöteten Heatspreadern zum Einsatz. Notebook-Chips bekommen hingegen oft nur einen Rahmen um den Die verpasst, der verhindert, dass ein verkanteter Kühler den Die beschädigt – ältere Leser werden sich eventuell noch an abgebrochene Die-Ecken bei Athlon-XP- oder Duron-CPUs erinnern.

Interessant zu beobachten war an dieser Station, dass quasi jeder Chip sein eigenes System bekommt, wie die Wärmeleitpaste aufgetragen wird. Das Indium wird quasi wie ein Wärmeleitpad erst auf den Die gelegt, nach dem Auflegen des Heatspreaders dann gemeinsam erhitzt und so verbunden.

Nach Schritt 3 ist im Endeffekt der Prozessor fertig, es folgen umfassende Tests. Als Erstes der Burn-in-Test mit maximaler Last um zu erkennen, ob die Limits bei Temperatur und Spannung eingehalten werden können. Es folgen weitere Tests ganz unterschiedlicher Art, die sicherstellen, dass die CPU auch das erreicht, was verlangt wird.

Das Binning, also die exakte Einordnung der CPU in seine Leistungsklasse, findet erst ganz am Ende statt. Zuvor hätte das keinen Sinn, da jeder der vorangegangenen Schritte dazu geführt haben könnte, dass die CPU ihre Einordnung am Ende doch nicht mehr erfüllt. Zum Abschluss bekommt die CPU ihre Gravur.

Tag 1: Packaging und Testing ist zeitaufwändig

Der erste Tag lieferte einen imposanten Eindruck davon, was das Zusammensetzen (von Intel früher einmal liebevoll als „Zusammenkleben“ bezeichnet) und Testen wirklich bedeutet, gerade eben auch bei den fortschrittlichsten Chips, die Intel aktuell fertigt und die mit Meteor Lake zwar auf kleinerem, aber nichtsdestoweniger extrem komplexem Package im Endkundensegment ankommen werden. Insbesondere die Tatsache, dass jeder dieser Schritte mehr Zeit braucht als im Vorfeld angenommen wurde, war ein echter Erkenntnisgewinn.

Diese Eindrücke haben der Notwendigkeit hinter den Ausbauplänen nicht nur von Intel hinsichtlich Assembly & Test, sondern eben auch mit Blick auf das ganze Thema Packaging noch mal deutlich mehr Nachdruck verliehen. Es wurde klar, warum nicht nur Intel in drei Anlagen gleichzeitig investiert hat und nun in Polen die nächste plant, sondern auch warum TSMC so viel investiert und investieren muss. Denn während Intel die Anlagen vorerst in erster Linie für die eigenen Produkte nutzt, stellt TSMC die Technologien für Kunden wie AMD, Nvidia oder Apple bereit. Und wenn Intel in Zukunft nicht nur Chips für andere bauen, sondern das Komplettpaket bieten will, geht ohne AT und Packaging einfach gar nichts.

Tag 2: Wafer zersägen und Dies sortieren in Kulim

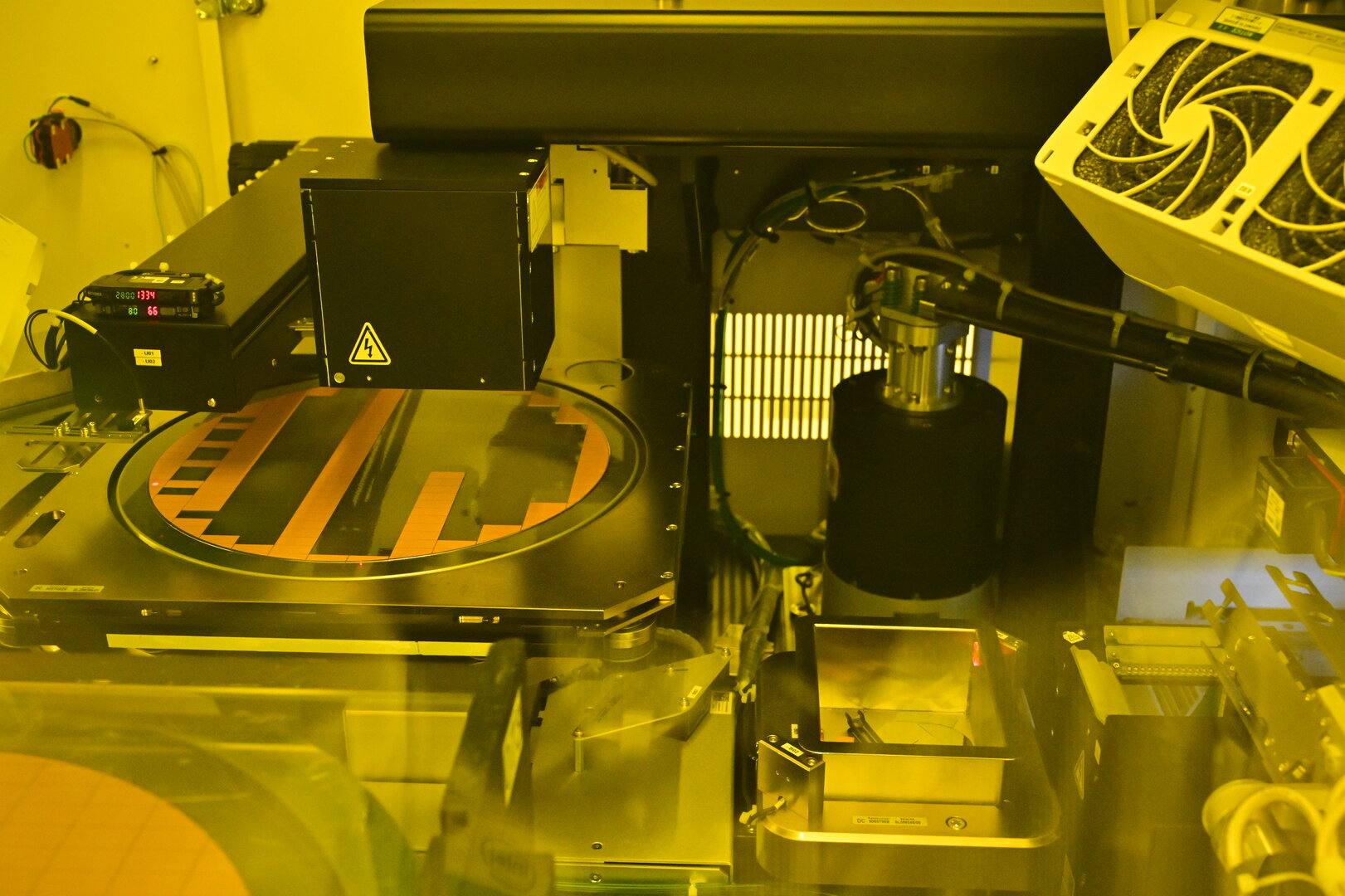

Tag 2 der Fab-Tour in Malaysia brachte die Journalisten raus aus der Freihandelszone Penang in die Nachbarschaft Kulim. Dort findet eine Fertigungsstufe statt, die produktabhängig ist und auch etwas mit den alten Wurzeln zu tun hat: Es werden Wafer zersägt und die Chips für die Weiterverarbeitung vorbereitet. In modernen Fabs wird dieser Schritt oftmals bereits direkt nach dem Belichten der Wafer vorgenommen, trotzdem wird Intel diese Dienstleistung auch in Zukunft noch separat anbieten und ihn je nach Produkt auch selbst nutzen. Denn zur Foundry kann ja schließlich auch ein Kunde kommen, der vollständige Wafer von einer anderen Foundry abnimmt, aber auf der Suche nach der Dienstleitung „Zersägen“ ist.

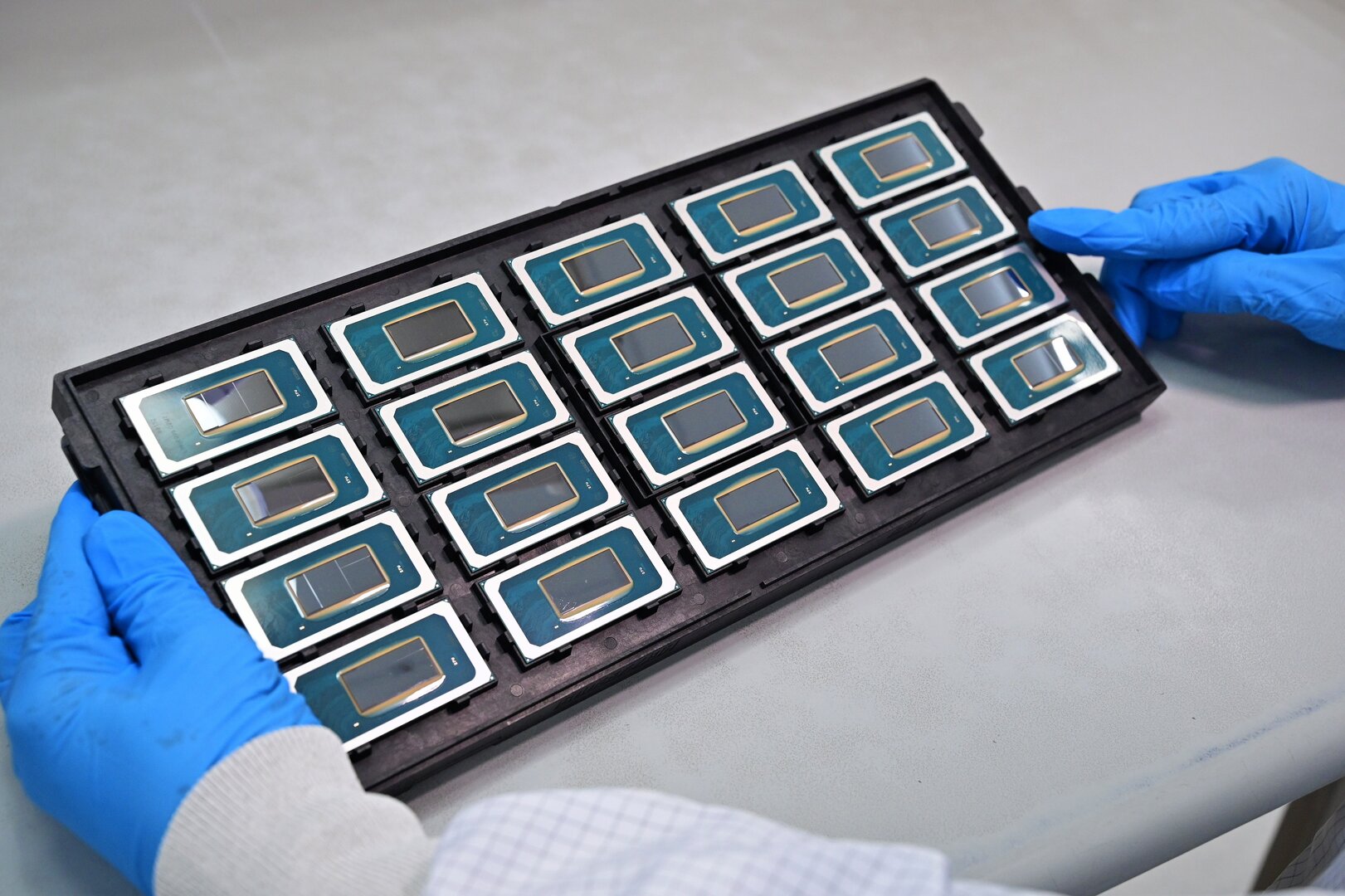

Beim Zersägen der Wafer werden die Chips von einer echten wassergekühlten Säge zerlegt und anschließend auf kleine rechteckige, standardisierte Trays gepackt, die für die weitere Verarbeitung einfach zu handhaben sind. Das Ziel ist dabei immer das gleiche: Mit Chips von einem Wafer werden drei Trays bestückt, deshalb weisen sie meist in der Mitte oder auch mal am Rand keine Chips auf, je nachdem wie groß der Wafer und/oder die Chips sind. Diese Trays werden in großen Containern verstaut und von einem fahrerlosen Transportsystem in die anderen Abteilungen gefahren. Basiert das Transportsystem in den Front-End-Wafer-Fabs auf einem Schienensystem an der Decke, sind es in diesem Fall selbstfahrende Roboter. Ein Arbeiter überwacht 300 dieser Roboter, die über 10.000 Carrier sind alle mit Barcodes und RFID versehen, verloren geht nichts.

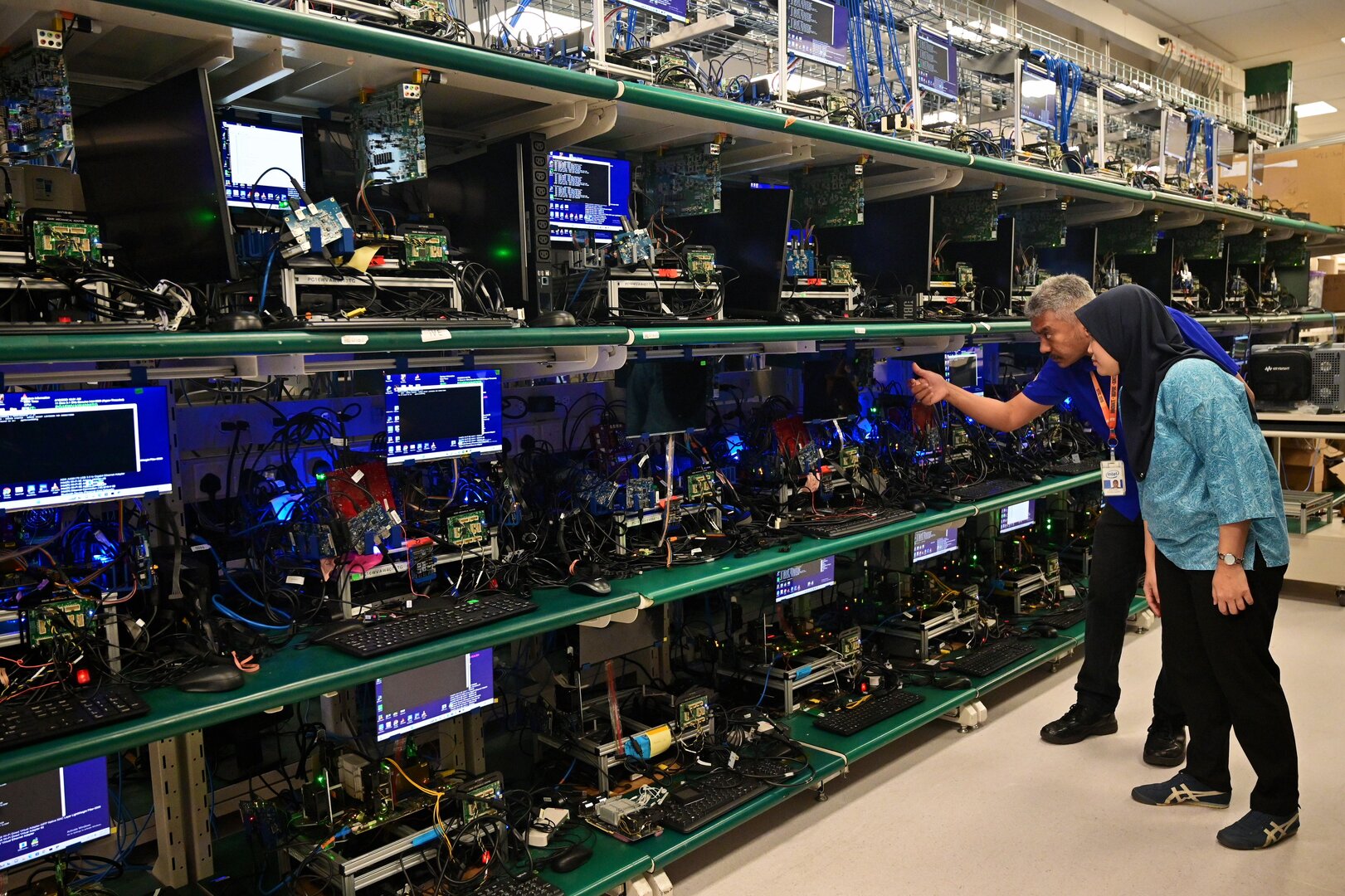

Die Trays voller Dies (vor Ort sichtbar waren neben Meteor-Lake-Chips auch die ersten XCC-Dies von Emerald Rapids) wandern anschließend in die Testanlage. Jeder Chip wird einzeln getestet. Abermals wurde deutlich, wie viel Parallelität nötig ist, um eine hohe Stückzahl an Chips zu bekommen. Eines dieser großen Testsysteme enthält 20 einzelne Einheiten, die je einen Chip testen können. Um am Ende des Tages viele Chips für die nächsten Schritte zu erhalten, benötigt es unzählige dieser Systeme, ansonsten wird dieser Schritt schnell zu einem weiteren Nadelöhr.

Nach dem Testen landen erst einmal wieder alle Dies im Tray. Ist ein Die durch den Test gefallen, wird er im nächsten Prozess aussortiert. Rausgeworfen wird er, wenn die Chips aus dem Tray auf die Rolle zur Weiterverarbeitung gebracht werden. Auf so eine Rolle passen 700 bis 800 große Serverchips, von kleineren Lösungen können es auch problemlos 3.000 sein. Pro beobachteten Tray blieben immer einige Chips zurück, die dann nicht zur Weiterverarbeitung ans PGAT geschickt wurden. Konkrete Yields nannte Intel natürlich nicht, sie hängen letztendlich auch vom Produkt ab.

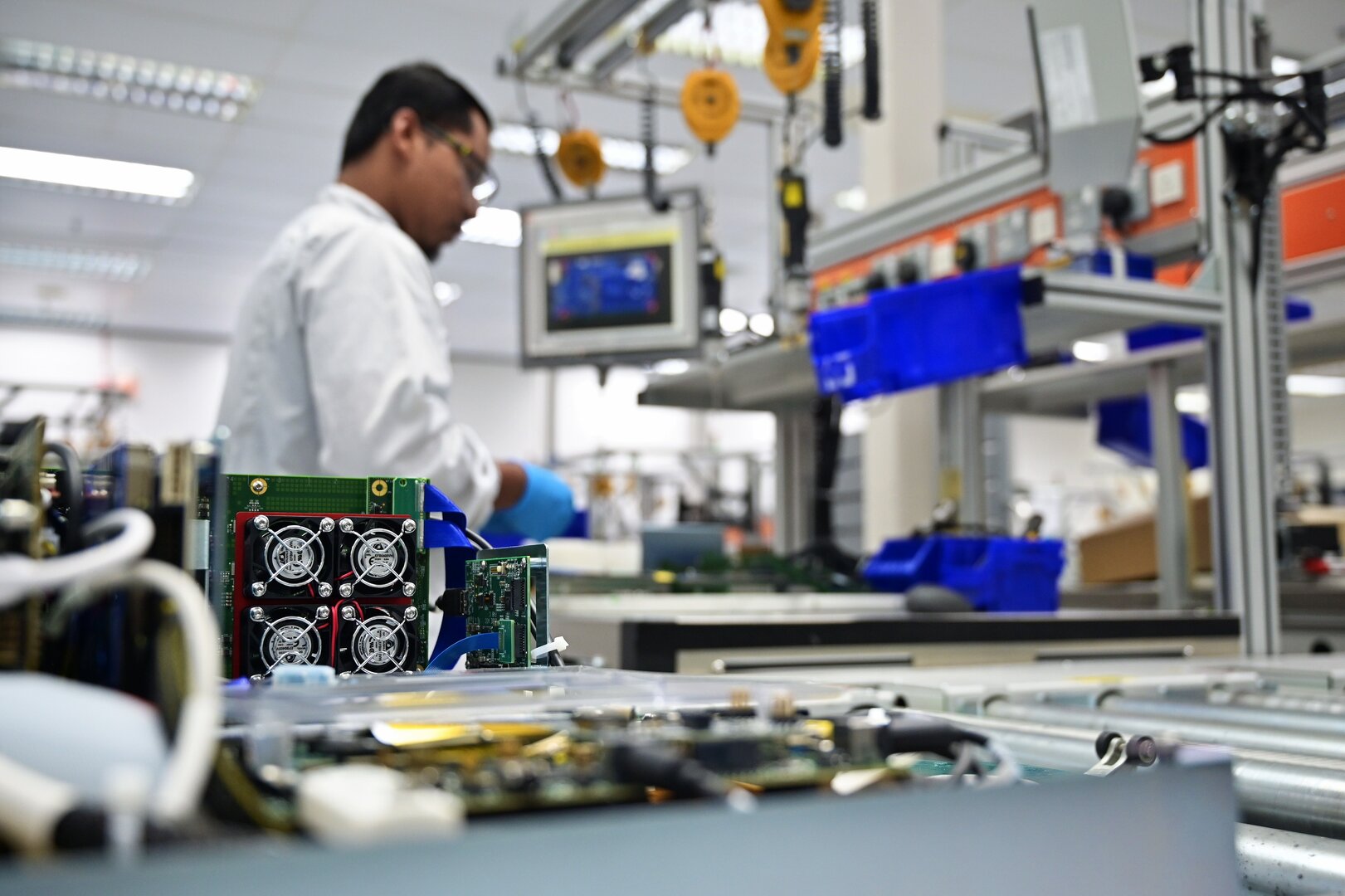

Tag 2: Auch Test-Tools wollen getestet sein

In Kulim entwickelt Intel auch eigene Testanlagen und natürlich werden diese Test-Tools mit anderen Test-Tools vorher getestet, bevor sie als dann funktionsfähige Testeinheit in den anderen Intel-Fabriken zum Einsatz kommen können. Der Komplex, in dem es um die Test-Tools geht, ist überraschend groß und verdeutlicht, was notwendig ist, um am Ende ein funktionsfähiges Produkt anbieten zu können. Genau das geschieht im SIMS („System Integration and Manufacturing Services“).

Die entwickelten Test-Tools können ganz unterschiedlich, zum Teil auch extrem groß ausfallen. Ab einem gewissen Gewicht kommen spezielle Geräte zum Einsatz, die die Testsysteme entfernen oder auch drehen können – viele Sachen werden beim Testen schließlich von der Unterseite abgegriffen.

Zu den großen neuen Systemen gehört unter anderem der Testaufbau für die neue Birch-Stream-Plattform, die im Jahr 2024 die Basis für Sierra Forest bilden wird. Diese neuen Tester liefen in Kulim gerade in größerer Anzahl vom Band, zwölf Speicherkanäle (mit DDR5-5600 bestückt) waren oft zu sehen. Zum Einsatz kommt diese Testplattform ab dem ersten Halbjahr des nächsten Jahres.

Haben Test-Tools alle Tests bestanden, werden diese Systeme zum Testen in die Fabrikteile geschickt, in denen sie benötigt werden. Aktuell werden von Intel nur die eigenen Fabriken beliefert.

Weitere Einrichtungen in Malaysia

Das PGAT auf Penang Island und die Einrichtungen in Kulim sind nicht alle Standorte von Intel in Malaysia.

Im Malaysia Design and Development Lab auf Penang Island entwickeln Intel-Ingenieure beispielsweise im globalen Verbund an aktuellen und zukünftigen Produkten. Das Spektrum ist dabei sehr groß und spricht eigentlich fast jeden Bereich bei Intel an, sodass unterm Strich an über 80 Prozent aller Produkte des Konzerns auch Intels 6.000 Mitarbeiter starkes Malaysia-Team beteiligt war.

Zu guter Letzt ist in Penang auch noch ein Labor zu finden, das sich um die genaue Fehleranalyse kümmert. Hier gibt es mitunter exotische Aufbauten, es kann jedes Produkt untersucht werden.

Und das schließt nicht nur die CPUs ein, denn an den Werkzeugkästen waren ebenfalls Aufkleber wie DG2-128, Intels aktuelle Arc-Grafikkarte, und BMG zu sehen – auch Battlemage, Intels nächster Grafikchip, wurde in Malaysia demzufolge schon mal gesehen.

Fazit

Es war für die geladenen Journalisten durchaus eine einmalige Gelegenheit, bisher hat Intel seine Packaging-Anlagen so noch keinem gezeigt. Natürlich war der Zeitpunkt bewusst gewählt, steht mit Meteor Lake doch die erste für Endkunden relevante Architektur, die auf „Advanced Packaging“ setzt, vor der Tür. Das schmälert den vor Ort gewonnen Eindruck, der sich auf Einrichtungen mit demselben Fokus bei Konkurrenten wie TSMC übertragen lassen sollte, allerdings nicht.

Eine Kernerkenntnis: Packaging und Testing ist noch viel komplexer als gedacht und obwohl die Anlagen schon heute enorme Ausmaße annehmen, müssen die Kapazitäten schnell gravierend ausgebaut werden, damit diese Fertigungsschritte nicht zum Flaschenhals werden. Weil auch diese Bauten obendrein mit der komplexesten Technik bestückt sind, geht das ins Geld und erklärt neben dem stetig schrumpfenden Fertigungsprozess die gestiegenen Kosten für Anlagen in der Industrie. Doch am Ende braucht es diese Anlagen in großer Form, um überhaupt auf nennenswerte Stückzahlen zu kommen.

Beeindruckend war deshalb vor allem die Skalierbarkeit, die nötig ist, um Millionen an Chips auszuliefern. Denn viele der unzähligen einzelnen Schritte brauchen doch mehr Zeit als erwartet. Schon den Wafer in der Fab zu belichten, dauert bis zu vier Monate, und danach folgt erst noch der gesamte Test- und Packaging-Prozess.

Dass man vor Ort in Malaysia so „frei“ unzählige Meteor-Lake-Chips, aber auch zukünftige High-End-Produkte wie Emerald Rapids-XCC bereits begutachten konnte, überraschte auf den ersten Blick ebenfalls. Doch wirklich etwas verraten, was nicht ohnehin schon bekannt war, wurde letztendlich nicht.

In Polen baut Intel zurzeit eine weitere Einrichtung, wie sie das PGAT in Malaysia darstellt, mit der Option auf mehr Erweiterungen für das Advanced Packaging. Mit einer Fab in Irland, in Zukunft auch Deutschland, könnte so zusammen mit Polen wirklich eine halbwegs europäische Kette aufgebaut werden. Natürlich sind immer noch viele Dinge dafür von externen Quellen nötig, es wurde vor Ort aber deutlich, warum mehr davon (und auch an anderen Standorten) durchaus sinnvoll ist. Und in Anbetracht von Intels Bestreben, als Foundry aktiv zu werden, kann das eine ohne das andere letztlich nicht funktionieren.

ComputerBase wurde von Intel zum Event nach Malaysia eingeladen. Flug und Hotel sowie alle Transfers sowie die Verpflegung vor Ort wurden von Intel gezahlt. Die Fab- und Laborbesuche standen nicht unter NDA, ein zweiter Teil vom Event hat ein NDA zu einem späteren Zeitpunkt. Eine Verpflichtung zur Veröffentlichung bestand nicht.

Dieser Artikel war interessant, hilfreich oder beides? Die Redaktion freut sich über jede Unterstützung durch ComputerBase Pro und deaktivierte Werbeblocker. Mehr zum Thema Anzeigen auf ComputerBase.