Ob eine feste Zuordung von GCD und CCD sinnvoll ist kann ich nicht beurteilen. Wenn sich die Programmierer zu Fuß darum kümmern müssen, sicher nicht.

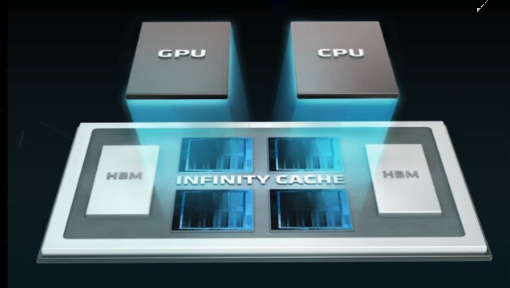

Ich interpretiere diese hübsche Grafik mit der schweben CPU und GPU einem Interposer mit Infinity Cache in der Mitte und den HBMStacks nicht als exakte Darstellung der APU.

Auf dieses Package kommt IMO keine CPU sondern CCDs. Wo und wie die IO-Funktionen der APU umgesetzt werden wird man sehen. IMO ist der IOD in einer CPU, die als ganzes darauf gesetzt wird der falsche Ort.

Beim Bard Peaks Node sind die NICs an die GPUs angeschlossen, und nicht an die CPU. Ich gehe nicht davon aus, dass es sich bei El Capitan ändert. Neben dem enger zusammenrücken hat eine APU auch den Vorteil, dass man nur die Funktionen integriert die die APU benötigt.

Das 3D Chiplet Packaging bezieht sich IMO nicht nur auf den Infinity Cache.

Darauf wollte ich mit den Grafiken hinaus.Colindo schrieb:Und diese Zuteilung wird bei El Capitan ja anscheinend wieder aufgehoben, da mehr CPU-Chiplets und weniger GCDs da sein werden. Zumindest sieht es momentant so aus.

Ich interpretiere diese hübsche Grafik mit der schweben CPU und GPU einem Interposer mit Infinity Cache in der Mitte und den HBMStacks nicht als exakte Darstellung der APU.

Auf dieses Package kommt IMO keine CPU sondern CCDs. Wo und wie die IO-Funktionen der APU umgesetzt werden wird man sehen. IMO ist der IOD in einer CPU, die als ganzes darauf gesetzt wird der falsche Ort.

Beim Bard Peaks Node sind die NICs an die GPUs angeschlossen, und nicht an die CPU. Ich gehe nicht davon aus, dass es sich bei El Capitan ändert. Neben dem enger zusammenrücken hat eine APU auch den Vorteil, dass man nur die Funktionen integriert die die APU benötigt.

Das 3D Chiplet Packaging bezieht sich IMO nicht nur auf den Infinity Cache.