Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

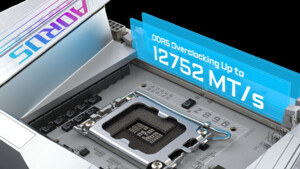

News Arbeitsspeicher: Adata rüstet sich mit MSI und Gigabyte für das DDR5-Debüt

- Ersteller MichaG

- Erstellt am

- Zur News: Arbeitsspeicher: Adata rüstet sich mit MSI und Gigabyte für das DDR5-Debüt

Naxtrumrar

Ensign

- Registriert

- Mai 2011

- Beiträge

- 128

Nein, ECC ist optional. Hängt aber dann direkt vom Speicherriegel selbst ab und nicht mehr von CPU/Mainboardicywiener schrieb:Sehe ich das Richtig, dass DDR5 immer ECC hat und nicht vom Mainboard abhängt?

Troy McClure

Lieutenant

- Registriert

- Jan. 2008

- Beiträge

- 820

Hab ich einen Knick in der Optik, oder sind die Pins in der Mitte des Moduls länger als Außen?

Entgegen der Meinung vieler hier, denke ich, dass AMD es sogar besonders einfach haben wird, DDR5 einzuführen.

Das praktische an ihren aktuellen CPUs ist ja, dass der Speichercontroller in einem eigenen Chip sitzt. D.h. theoretisch müsste AMD die ganz normalen Zen3-Kerne weiterproduzieren können, die kommunizieren ja per Infinitiy Fabric untereinander und mit dem Speichercontroller.

D.h. eine Revision des Speichercontrollers reicht, um ihm DDR5 beizubringen. Der Controller selbst wird wahrscheinlich auch einfacher aufgebaut sein (und wird in einem günstigeren Verfahren gefertigt) als die CCX-Chiplets. Experimentieren und Revisionen werden also wahrscheinlich ebenfalls günstiger sein.

Je nachdem, wie viel Platz pro Speichercontroller benötigt wird bzw. wie einfach es zu implementieren ist, kann AMD also auch einen dualen DDR4/DDR5-Controller entwickeln (spart Fabrikationslinien) oder parallel zwei Speichercontroller fertigen und mit minimalen Änderungen weiter CPUs für DDR4 bedienen, als auch günstig DDR5-CPUs anbieten.

Dass sich DDR5 im ersten Jahr aufgrund des langsameren Takts (für Spieler) nicht lohnen wird, haben ja einige schon geschrieben. Da Server-RAM ohnehin nicht übertaktet, sondern nach Spezifikation betrieben wird, wird sich dort jedoch von Anfang an der niedrigere Stromverbrauch etc. bemerkbar machen.

Das praktische an ihren aktuellen CPUs ist ja, dass der Speichercontroller in einem eigenen Chip sitzt. D.h. theoretisch müsste AMD die ganz normalen Zen3-Kerne weiterproduzieren können, die kommunizieren ja per Infinitiy Fabric untereinander und mit dem Speichercontroller.

D.h. eine Revision des Speichercontrollers reicht, um ihm DDR5 beizubringen. Der Controller selbst wird wahrscheinlich auch einfacher aufgebaut sein (und wird in einem günstigeren Verfahren gefertigt) als die CCX-Chiplets. Experimentieren und Revisionen werden also wahrscheinlich ebenfalls günstiger sein.

Je nachdem, wie viel Platz pro Speichercontroller benötigt wird bzw. wie einfach es zu implementieren ist, kann AMD also auch einen dualen DDR4/DDR5-Controller entwickeln (spart Fabrikationslinien) oder parallel zwei Speichercontroller fertigen und mit minimalen Änderungen weiter CPUs für DDR4 bedienen, als auch günstig DDR5-CPUs anbieten.

Dass sich DDR5 im ersten Jahr aufgrund des langsameren Takts (für Spieler) nicht lohnen wird, haben ja einige schon geschrieben. Da Server-RAM ohnehin nicht übertaktet, sondern nach Spezifikation betrieben wird, wird sich dort jedoch von Anfang an der niedrigere Stromverbrauch etc. bemerkbar machen.

Excel

Lieutenant

- Registriert

- Juli 2011

- Beiträge

- 773

Philanthrop schrieb:@black-wizard

@Darkblade08

@Excel

@Lord_X

Aus meiner Erfahrung heraus (DDR3, DDR4) ist dies AMD´s große Problemzone. Nicht das es keine Speicherkompatibilitätsprobleme auch bei Intel geben würde, aber AMD hat dort schwerer zu kämpfen und deswegen auch mein Vorurteil.

Wäre naturlich Hammer wenn AMD das in den Griff bekommt, dann gibt es nähmlich 0 Argumente um auf ein Intelsystem zu setzten.

Anfangs waren die Systeme durchaus zickig und wählerisch, was RAM angeht. Nicht jeder Riegel und nicht jede Art von Bestückung hat funktioniert, übertakten war schwierig. Das war zu Zeiten von Ryzen 1000.

Aber mittlerweile hat AMD dermaßen nachgebessert, dass die Situation diesbezüglich gar nicht mehr vergleichbar ist. Schon Ryzen 2000 war besser, Ryzen 3000 sowieso. Es sind ja auch 3 Jahre vergangen.

Mittlerweile konzentriert man sich eher schon auf Feinheiten wie Undervolting und dem Ausreizen des RAM-Taktes.

Siehe auch https://www.computerbase.de/news/pr...0-overclocking-undervolting-agesa-bios.74215/

Update:

https://www.computerbase.de/news/prozessoren/amd-agesa-comboam4v2pi-1-1-9-0-overclocking.74942/

Zuletzt bearbeitet:

(Link ergänzt)

0x8100

Fleet Admiral

- Registriert

- Okt. 2015

- Beiträge

- 10.078

das ist auch bei ddr4 schon so. damit muss beim stecken weniger kraft aufgewendet werden. besser für das modul, den slot und auch den userTroy McClure schrieb:Hab ich einen Knick in der Optik, oder sind die Pins in der Mitte des Moduls länger als Außen?

lynx007

Commodore

- Registriert

- Feb. 2011

- Beiträge

- 4.991

Meinen sie mit "Vogel" Torvalds?H3llF15H schrieb:Wenn ECC immer an Board sein sollte, verstehe ich die Aussagen von dem Linux-Vogel von gestern nicht...

"Der ECC-Speicher löst diese Probleme - na ja, im Fall von Rowhammer - und ist seit über 50 Jahren verfügbar, wird jedoch von den meisten PCs nicht verwendet. Die Kosten sind ein Faktor, aber was Torvalds ärgert, ist, dass Intel die ECC-Unterstützung zu einer Funktion seiner Xeon-Reihe gemacht hat, die auf Server und High-End-Workstations abzielt, und sie in anderen Bereichen wie der Core-Serie nicht unterstützt."

https://www.theregister.com/2021/01/04/linus_torvalds_intel_killed_ecc/

Was gibt es da nicht zu verstehen? Laut ihm gibt es gegen den Angriff Rowhammer seit 50 Jahren eine technisch umsetzbare und günstige Lösung. Der Angriff wiederum wieuderm seit 2015 bekannt. Intel bietet die Lösung wiederum für viel Geld ausschließlich für ihre Workstations und Server an. Das findet Torvalds wiederum von Intel halt scheiße.

https://de.wikipedia.org/wiki/Rowhammer

https://www.wired.com/story/rowhammer-ecc-memory-data-hack/

Zuletzt bearbeitet:

Steven Coolmay

Ensign

- Registriert

- März 2020

- Beiträge

- 166

Nur mal so als Frage, was habt ihr alle mit der Volt Zahl? Von wie viel Watt sprechen wir hier, so 5-8W?

Wenn juckts das? Meine RGB Beleuchtung verbraucht mehr wie mein RAM.

Oder hab ich da nen Denkfehler?

Wenn juckts das? Meine RGB Beleuchtung verbraucht mehr wie mein RAM.

Oder hab ich da nen Denkfehler?

Botcruscher

Commodore

- Registriert

- Aug. 2005

- Beiträge

- 4.169

Die Gewinne bei CPUs kommen fast ausschließlich aus der Lantenz. Da sieht es im Moment laut hynix nicht so gut aus:

PS: Und wenn man sich LP-DDR4X ansieht sollte man womöglich mal endlich von dem Slot Format einige Kilometer von der CPU entfernt wegkommen.

- DDR5-4800A: 34-34-34

- DDR5-4800B: 40-40-40

- DDR5-4800C: 42-42-42

PS: Und wenn man sich LP-DDR4X ansieht sollte man womöglich mal endlich von dem Slot Format einige Kilometer von der CPU entfernt wegkommen.

Man redet halt drüber und ist doch erfreulich, wo Undervolting ja auch so beliebt ist.Steven Coolmay schrieb:Nur mal so als Frage, was habt ihr alle mit der Volt Zahl? Von wie viel Watt sprechen wir hier, so 5-8W?

Steven Coolmay

Ensign

- Registriert

- März 2020

- Beiträge

- 166

Ok, danke und ich dachte schon ich hab etwas verpasst.Nickel schrieb:Man redet halt drüber und ist doch erfreulich, wo Undervolting ja auch so beliebt ist.

Excel

Lieutenant

- Registriert

- Juli 2011

- Beiträge

- 773

Gerade bei mobilen Geräten rein wichtiger Faktor!Steven Coolmay schrieb:Nur mal so als Frage, was habt ihr alle mit der Volt Zahl? Von wie viel Watt sprechen wir hier, so 5-8W?

Wenn juckts das? Meine RGB Beleuchtung verbraucht mehr wie mein RAM.

Oder hab ich da nen Denkfehler?

foofoobar

Captain

- Registriert

- Dez. 2011

- Beiträge

- 3.978

icywiener schrieb:Sehe ich das Richtig, dass DDR5 immer ECC hat und nicht vom Mainboard abhängt?

Klares Jein, die Chips intern machen ECC. Die Übertragung RAM <-> CPU muß nach wie vor mit normalen ECC gesichert werden.

pmkrefeld

Captain

- Registriert

- Feb. 2012

- Beiträge

- 4.043

Wegen DDR5 ?!?!?eRacoon schrieb:Gut das ich bei Intel 10/11 und Ryzen die Finger still halten konnte/kann.

Selbst mit ganz grobem Halbwissen ist das schnell als Spannungsversorgung etc. auszumachen.-Ps-Y-cO- schrieb:

Weiter oben steht aber schon: On die. D.h. das sitzt in den Chips selber. Dennoch wird es auch Module mit 10 (bzw. einem Vielfachen davon) Chips geben, die dann pro 4 Chips einen Parity haben.

IIRC fällt die Spannungsversorgung deutlich auffälliger aus, weil die Spannungsversorgung der Module damit vereinfacht wird.

Jenergy

Rear Admiral

- Registriert

- Dez. 2008

- Beiträge

- 5.459

Aber nur beim sogenannten "Dual-Parity". Ansonsten benötigt man pro 8 Chips nur einen zusätzlichen (7 Check-Bits pro 64 Bit).Nagilum99 schrieb:[...] die dann pro 4 Chips einen Parity haben.

DDR5 Speicher Module werden dieses Jahr in einer geringen Anzahl erscheinen.

Daher wird der Preis pro Modul/Kit dementsprechend hoch ausfallen!

Exakt das gleiche Spiel hatten wir mit DDR4 im dritten Quartal 2014.

Falls der neue Speicher zum Einsatz kommen soll, benötigt man natürlich ein neues Mainboard!

Daher wird der Preis pro Modul/Kit dementsprechend hoch ausfallen!

Exakt das gleiche Spiel hatten wir mit DDR4 im dritten Quartal 2014.

Falls der neue Speicher zum Einsatz kommen soll, benötigt man natürlich ein neues Mainboard!

lynx007 schrieb:---Vollzitat entfernt---

bitte Zitierregeln beachten

Ich hatte gestern echt keine Lust mehr zu diesem Thema zu schreiben. Torvalds möchte gerne mit Consumer Hardware, auch gerne mit "Bastellösungen" eben "kommerzielle" Systeme betreiben.

Wie jetzt einige mit gefährlichen Halbwissen auf Rowhammer kamen.....

Weil 99,99 % aller überhaupt nicht verstehen was Rowhammer ist: Rowhammer ist ein Konzept der beschreibt wie man den Umstand ausnutzen kann, dass die Packdichte etc. der "Speicherzellen" zugenommen hat und man durch entsprechende "Zugriffsmuster" auf bestimmte Zellen "Fehler" auf benachbarten Zellen provozieren kann und somit Angriffe kreieren kann. Das ist das Konzept. Praktische Lücken funktionieren in der Regel nur mit dem Kippen von mehren Zellen bzw. selbst bei der gezielten Manipulation einer Zelle ist die Wahrscheinlichkeit hoch, dass andere Zelle kollateral betroffen sind. Somit war und wird ECC kein Schutz vor Rowhammer sein. Zusätzlich gibt es mit dem RAMBleed Beispiel auch ein Single Bit Exploit welcher auch mit aktiven ECC funktioniert und das Konzept ECC komplett aushebelt. Entsprechend wurde mit der LPDDR4 Spec das sogenannte Targert Row Refresh Verfahren durch die JEDEC in die Spezifikation aufgenommen was auch viele DDR4 Hersteller implementiert haben. Das löst das Problem auf einer anderen Ebene und grundsätzlicher als es jemals mit ECC erfolgen könnte und mittlerweile haben fast alle DDR4 DRAM Chiphersteller es implementiert. Allerding ist Anfang des Jahres eine neuer Ansatz erarbeitet worden, womit man auch TRR absurdum führt.

Zurück zum Thema DDR5:

1. Mit LPDDR5 wurde schon RFM als Nachfolger für TRR in die Spezifikation aufgenommen. RFM dürfte vom Ansatz her eine Lösung sein für "Rowhammer" - artige Sicherheitslücken und theoretisch ist bisher kein Weg bekannt es zu umgehen.

2. Rowhammer war eine "Sicherheitslücke" welche durch die Packdichte der DRAM Zellen entstanden ist und hat NICHTS mit CPU zu tun sondern es ist ein Problem der DRAM Hersteller. Diese haben es mit TRR und jetzt mit RFM angegangen.

3. ECC bietet KEIN Schutz gegen Angriffe basierend auf Rowhammer Methoden weil es eben auf Konzeptebene schon bewiesen ist, dass man selbst mit Single Flips Möglichkeiten hat ECC auszuhebeln.

Zum Thema ECC und DDR5:

DDR5 bringt optional einen On-Die ECC Controller mit. Einen solchen setzt schon heute Micron in diversen DRAM Zellen an. Single Bit Fehler werden dabei On Die korrigiert. Multi Bit Fehler muss die "Kette" weiter hinten logen. Allerdings muss die CPU etc. keine eigenen ECC implementieren sondern es nur durchschleifen. Soweit mir bekannt war es bisher optional für DDR5 den On-Die ECC mitzubringen allerdings dürften es wohl die meisten DRAM Hersteller tun.

Zuletzt bearbeitet von einem Moderator: