Nein. Für die Chiplets wird kein Interposter (CoWoS) benötigt. Es wird InFo OS verwendet, dafür braucht man keinen Interposer.ragnarok666 schrieb:Anstelle von stacked Cashe könnte AMD nicht einfach so einen 32Gbit HBM4 Chip als L4 Cache mit aufs Package setzen? Interposer haben sie ja eh schon wegen den Chiplets.

https://semiwiki.com/semiconductor-manufacturers/tsmc/306329-advanced-2-5d-3d-packaging-roadmap/

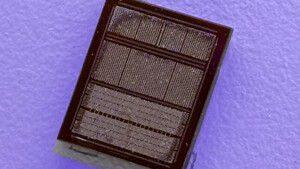

Deswegen heisen die Verbindungen bei AMD auch "Fanout" Links

https://www.hardwareluxx.de/images/..._memory_xk/amd-rdna3-breakout-014_1920px.jpeg

https://www.hardwareluxx.de/images/...old_app_qx/amd-rdna3-breakout-015_1920px.jpeg

Zuletzt bearbeitet: