1. Der Yield muß ja richtig schlecht sein wenn Intel nur so ein mini-Chiplet in Intel 4 hinbekommt. Dieses Packaging wird die Kosten ganz schön hochtreiben. Das ist ja auch kein günstiges multi-chip Packaging wie fan-out wafer-level-packaging.

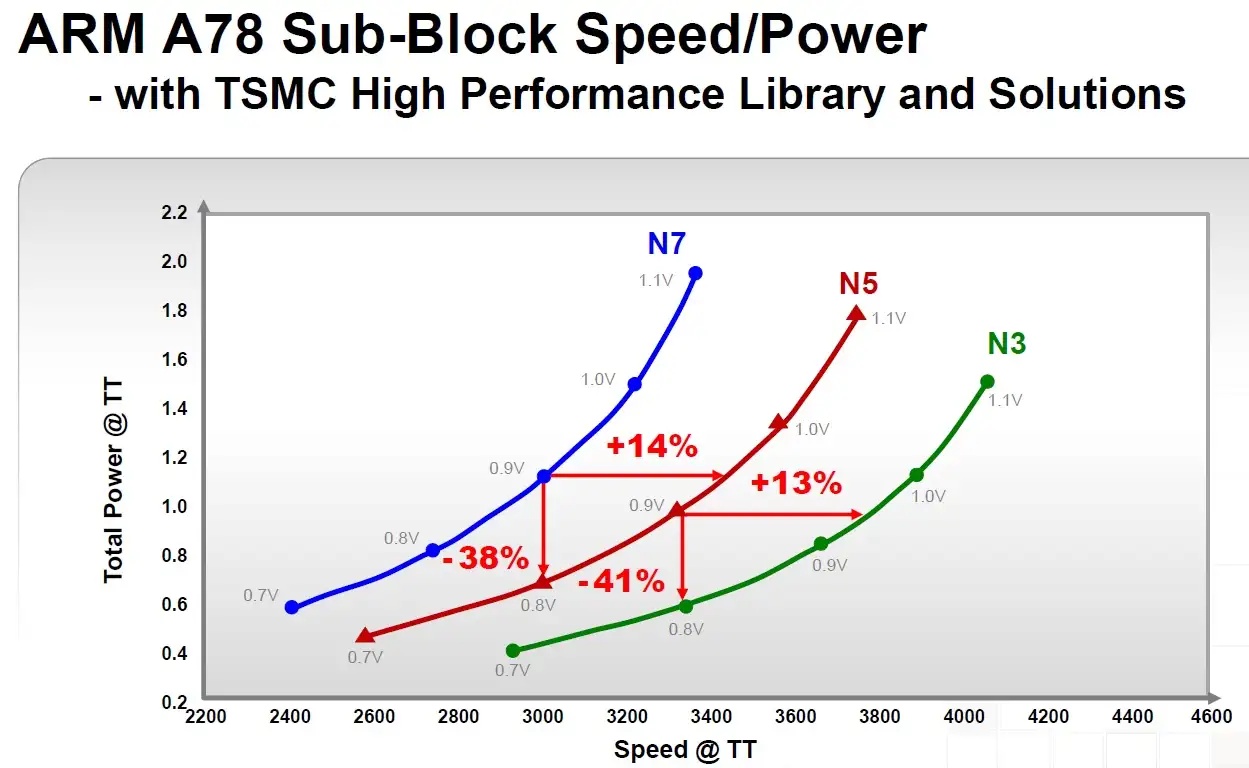

2. Intel versucht mit den >20% Frequenz zu tricksen: TSMC und Co geben bei den PPAs wenigstens an wie viel Frequenz mehr man wirlkich erreichen kann (zusätzlich zum Stromsparen). Wenn man sich das Diagramm hier anschaut sieht man aber, daß hier nur im mittleren Bereich die >20% gelten. Bei höheren Strömen sind es offensichtlich weniger als 20%. Außerdem bleibt unklar ob man überhaupt hohe Frequenzen mit diesem Prozess erreichen kann. Das war ja schon ein Riesenproblem von 14 nm zu 10 nm.

Wenn sie als Foundry ernst genommen werden möchten sollte Intel wirklich PPAs wie TSMC/SS/GF veröffentlichen.

hab gerade erst gemerkt, daß man Bilder hier einfügen kann:

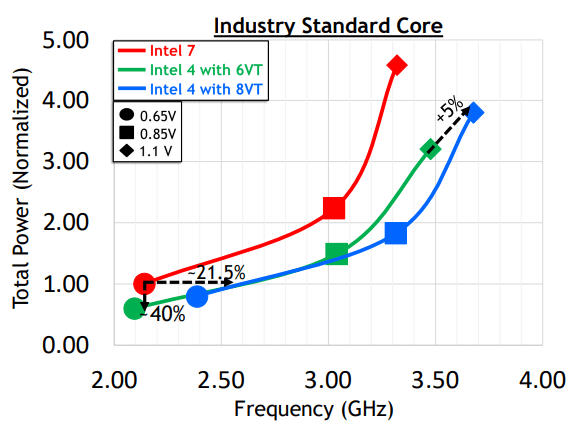

Auch ein "Industry Standard Core" zum Vergleich. Wenn TSMC auch bei niedrigeren Frequenzen vergleichen (~2,1 Ghz, oder von mir aus 0.65V TSMC N7) würde, wären die Frequenzsprünge ja deutlich größer sein @ iso power. Kurz: Die 3 Ghz für A78 bei N7 sind ein realistischer Punkt für nen Vergleich, die ~2,1 Ghz für Intel 7 hingegen nicht weil der quasi-lineare Bereich noch bis knapp 3 Ghz geht.

2. Intel versucht mit den >20% Frequenz zu tricksen: TSMC und Co geben bei den PPAs wenigstens an wie viel Frequenz mehr man wirlkich erreichen kann (zusätzlich zum Stromsparen). Wenn man sich das Diagramm hier anschaut sieht man aber, daß hier nur im mittleren Bereich die >20% gelten. Bei höheren Strömen sind es offensichtlich weniger als 20%. Außerdem bleibt unklar ob man überhaupt hohe Frequenzen mit diesem Prozess erreichen kann. Das war ja schon ein Riesenproblem von 14 nm zu 10 nm.

Wenn sie als Foundry ernst genommen werden möchten sollte Intel wirklich PPAs wie TSMC/SS/GF veröffentlichen.

Ergänzung ()

hab gerade erst gemerkt, daß man Bilder hier einfügen kann:

Auch ein "Industry Standard Core" zum Vergleich. Wenn TSMC auch bei niedrigeren Frequenzen vergleichen (~2,1 Ghz, oder von mir aus 0.65V TSMC N7) würde, wären die Frequenzsprünge ja deutlich größer sein @ iso power. Kurz: Die 3 Ghz für A78 bei N7 sind ein realistischer Punkt für nen Vergleich, die ~2,1 Ghz für Intel 7 hingegen nicht weil der quasi-lineare Bereich noch bis knapp 3 Ghz geht.

Zuletzt bearbeitet: