bensen schrieb:

Steig nicht ganz durch was du jetzt sagen willst. Wenn alles gleich ist, bis auf die Anzahl der Lagen, dann hat man die Kapazität pro Lage verringert, sonst nichts. Wo kommt denn da ne höhere Datendichte her?

Die Datendichte ergibt sich aus der Kapazität geteilt durch die Die-Fläche, baut man höher, also 32 statt 24 Layer, steigt also auch die Kapazität bei gleicher Grundfläche und damit die Datendichte, das ist doch logisch.

bensen schrieb:

Aber ich habe was komplett anderes gelesen, u.a bei Anandtech:

Code:

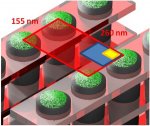

Samsung 1st Gen V-NAND Samsung 2nd Gen V-NAND

Die Capacity 128Gbit 86Gbit

Die Size 133mm2 ~95.4mm2

Wenn die Zahlen von Anand stimmen, die er ja nur aus einen Foto eines Dies (wer weiß was das wirklich für ein Wafer war?) auf einer Messe ermittelt hat, dann wäre das der Effekt des kleineren Diessize welcher das Verhältnis der Fläche der Zellen zur Gesamtfläche des Chip negativ beeinflusst, da man im Verhältnis zur Fläche der eigentlich Speicherzellen mehr Platz für die restliche Logik braucht und der Platz dafür ist kaum von der Kapazität abhängig.

Man sieht das an den Werten von Microns 20nm NAND, welches als 64Gigabit und als 128 Gigabit Chip verfügbar ist:

Das

128Gigabit 20nm NAND Die von Micron ist 202mm² groß, das mit 64 Gigabit aber 118mm². Lösen wir die Gleichungen:

x + y = 118mm² und 2x + y = 202mm² so kommen wir für x auf 84mm² (Fläche für 64Gigabit Daten) und y = 34mm² (Fläche der übrigen Logik).

Bei dem Samsung NAND müsste es ja ähnlich sein, die knapp 86Gigabit (es sind ja nicht ganz 86 sondern nur 85,3, aber die NANDs haben in Wirklichkeit alle mehr als an angegebenen Gigabit, da jede Page und jeder Block noch Extrakapazitäten aufweisen) wären nur 64Gigabit, wäre es nur 24 Layer. Damit wären die Gleichungen dann:

x + y = 95,4mm² und 2x + y = 133mm², X ist dann nur 37,6mm² (Grundfläche für 64 Gigabit) und y ist 57,8mm² für die Logik, die einmal aufwendiger sein könnte und zum anderen aufgrund des großen Fertigungsprozesses sehr groß ausfallen dürfte. Das hat in der Tat die Steigerung der Datendichte durch die Verwendung von 1/3 mehr Layern mehr als kompensiert und am Ende für eine geringere Datendichte bei der zweiten Generation gesorgt, weil dort eben eine kleinere Diesize gewählt wurde. Bei dem krassen Verhältnis dürfte aber Samsung bald auch V-NAND mit größeren Diesize bringen, denn auf den 133mm² ließen sich mit 32 Layern ja auch schon 170,7Gigabit realisieren und als TLC dann 256Gigabit.

Laut

Chipworks soll das Die der zweiten Generation übrigens nur 85mm² groß sein und damit wäre dann die Datendichte auch leicht gegenüber dem der ersten Generation gestiegen:

Machen wir die Rechnung damit noch mal, kommen wir auf 48 mm² als Grundfläche für 64 Gigabit mit 24 Layern bzw. 86Gbit mit 32 Layers und auf 37mm² für die Logik, was nur wenig mehr wäre als die Logik bei Micron 20nm NAND beansprucht.

Auf

dem Bild des Dies welches

Anandtech bei seinen Berechnungen zugrunde gelegt hat beansprucht die Logik etwa 35% der Diefläche, was aber zu keiner der Berechnungen passen würde. Damit müsste das ein anderer Chip gewesen sein, denn wenn man unterstellt das die Logik bei mehr Speicherzellen auch mehr Platz einnimmt, dann würde diese auf dem Chip einen noch größeren Anteil der Fläche belegen und weniger Logik bei mehr Zellen kann ja auch nicht sein.

bensen schrieb:

20nm für den 3D-NAND?

Hast du da genaue Daten? Bei Samsung sollns ja 40nm sein. Intel sagt durch die Blume auch 40nm, aber nichts konkretes.

Stimmt, da habe ich wohl irgendwo was falsches gelesen, finde jetzt aber nicht wo das war. Vielleicht ging es da auch um die 2mm Dicke von der Intel auch spricht und das wurden irgendwie in 20nm verwandelt:

Ein 3d NANDs in einem 2xnm Prozess zu fertigen wäre im Anbetracht der Fläche die für die Zellen zur Verfügung steht sicher nicht das Problem, eher schon die Durchkontaktierung der Layer.

bensen schrieb:

Das ist definitv so, heißt aber nicht, dass andere nicht schnell aufholen können. Wird auf jeden Fall vielleicht etwas spannender 2015.

Wie schnell die anderen Aufholen wird man sehen, es soll ja noch eine Weile dauern, bis die 3d NANDs von Intel dann auch in SSDs kommen und das wird sicher zuerst in Enterprise SSDs der Fall sein, aber 2015 verspricht spannend zu werden, da geben ich Dir recht.