Schildbrecher

Lt. Junior Grade Pro

- Registriert

- Feb. 2020

- Beiträge

- 489

Hallo zusammen,

haben wir hier RAM Spezialisten, die sich mit A-DIE DR auskennen?

Ich habe mein A-DIE Kit (6400 CL30; 32 (2x16) GB; SR) erst einmal meiner Schwester geliehen. Und mir ein 6600 CL32 (64 (2x32) GB; DR) geholt.

6600, 6400 und 6200 MHz habe ich kaum ans laufen bekommen und es hat Blue Screen gehagelt.

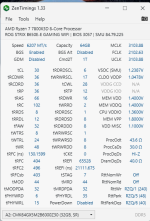

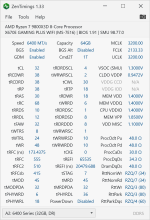

Aktuell habe ich diese Config stable:

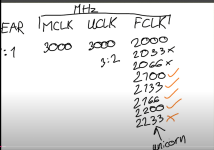

Bei den Timings versuche ich mich an dieser Liste hier zu orientieren:

https://www.computerbase.de/forum/threads/ddr5-timing-calculator-for-amd.2175124/#post-29175776

Bin aber auch noch nicht ganz durch - muss mich wieder etwas einarbeiten...

Was mich interessieren würde, warum bekomme ich 6600 / 6400 / 6200 MHz nichts ans Laufen? Erreicht der IMC bei DR schnell seine Grenzen?

Ich hatte erst überlegt ein 48 GB M-DIE Kit zu nehmen, vllt hätte ich das mal besser getan - wobei ich den RAM bis zum 15.01.2025 bei Amazon zurückgeben kann 🙈 😅

😅

haben wir hier RAM Spezialisten, die sich mit A-DIE DR auskennen?

Ich habe mein A-DIE Kit (6400 CL30; 32 (2x16) GB; SR) erst einmal meiner Schwester geliehen. Und mir ein 6600 CL32 (64 (2x32) GB; DR) geholt.

6600, 6400 und 6200 MHz habe ich kaum ans laufen bekommen und es hat Blue Screen gehagelt.

Aktuell habe ich diese Config stable:

Bei den Timings versuche ich mich an dieser Liste hier zu orientieren:

https://www.computerbase.de/forum/threads/ddr5-timing-calculator-for-amd.2175124/#post-29175776

Bin aber auch noch nicht ganz durch - muss mich wieder etwas einarbeiten...

Was mich interessieren würde, warum bekomme ich 6600 / 6400 / 6200 MHz nichts ans Laufen? Erreicht der IMC bei DR schnell seine Grenzen?

Ich hatte erst überlegt ein 48 GB M-DIE Kit zu nehmen, vllt hätte ich das mal besser getan - wobei ich den RAM bis zum 15.01.2025 bei Amazon zurückgeben kann 🙈