M.tze schrieb:Hab Elektrotechnik mit der Fachrichtung Mikro- und Nanoelektronik in Aachen studiert. Hab in Aachen ziemlich viel Prozess- und Bauteiltechnologie für GaN gemacht. Jetzt machen ich Analog-Mixed-Signal ICs (Silizium, natürlich...). Also Schaltungsdesign analog, Layouten und ein kleines bisschen Digitalstuff (aber synthetisiert aus Verilog).

Komme gar nicht aus diesem Gebiet, deswegen eine dumme Frage.

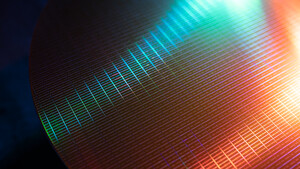

Werden Chips in der Serienfertigung gegossen oder per Laser hergestellt?

Rein vom Gefühl hätte ich gesagt Werkzeugmuster werden gelasert und Produktionschips gegossen.

Im Internet bekommt man viel Markering zu dem Thema, speziell Youtube, aber wenig Inhalt.