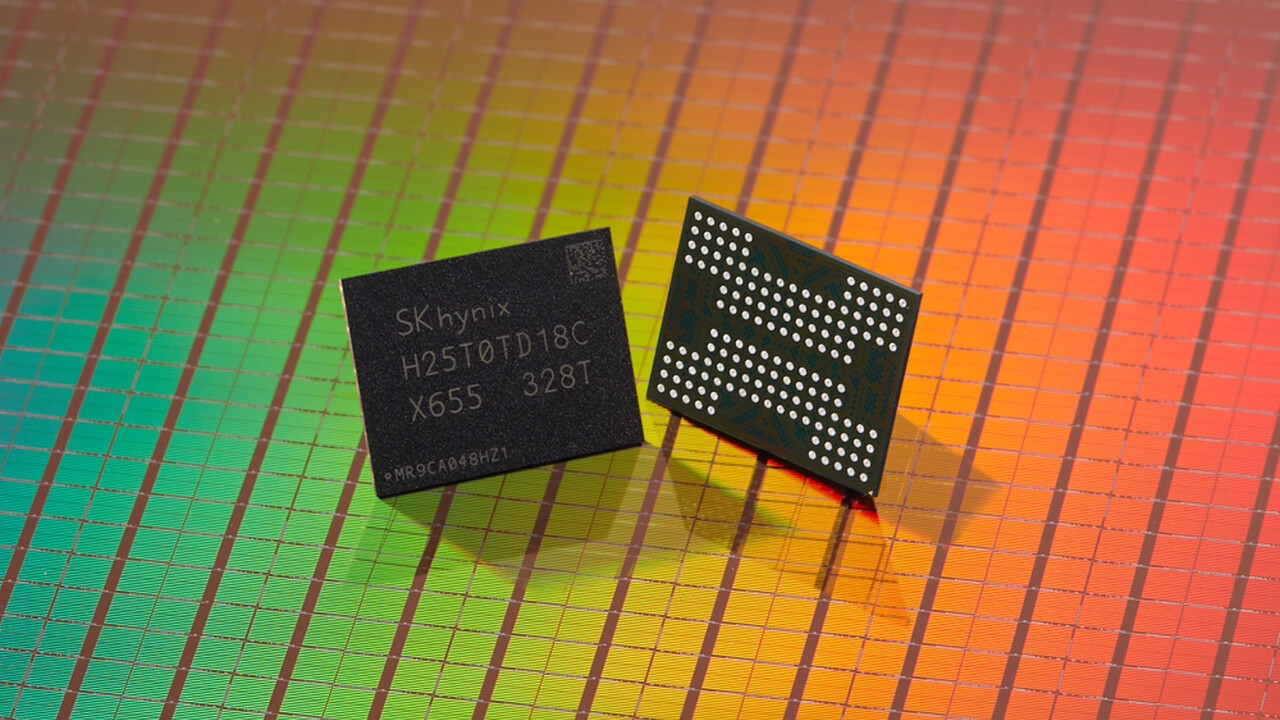

Flash Memory Summit: SK Hynix entwickelt 321-Layer-TLC-NAND

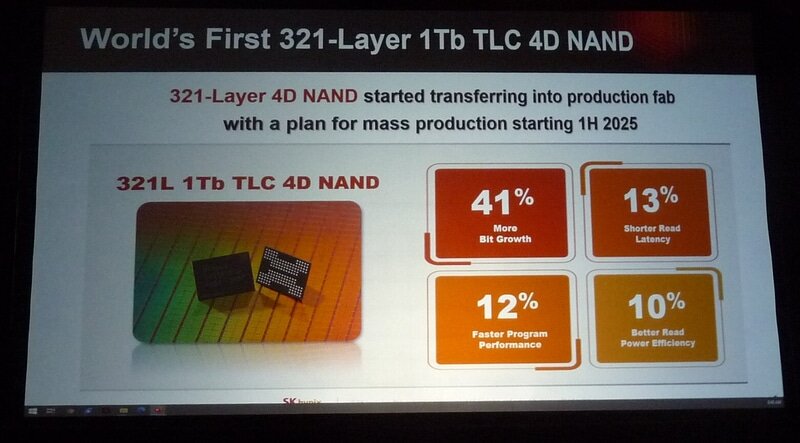

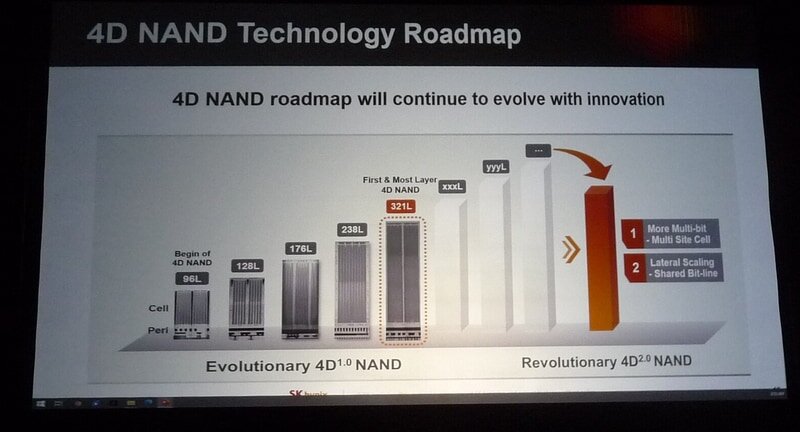

Als erster Hersteller präsentiert SK Hynix auf dem Flash Memory Summit 2023 eine neue Generation 3D-NAND mit mehr als 300 Zellebenen (Layer). Konkret sollen 321 Layer vorliegen. Pro Zelle werden 3 Bit (TLC) gespeichert und ein ganzer Chip speichert 1 Tbit Daten. Die Serienfertigung steht aber noch lange nicht an.

Erneut spricht SK Hynix von „4D NAND“, eine Idee der Marketing-Abteilung, die sonst kein anderer Hersteller für 3D-NAND nutzt. Zunächst präsentiert SK Hynix lediglich frühe Musterchips des 321-Layer-NAND, der für die spätere Massenproduktion erst noch fertig entwickelt werden muss. Mit dem Start der Serienfertigung rechnet der Hersteller im ersten Halbjahr 2025, sodass also noch viel Zeit für den Feinschliff ist.

The company plans to raise the level of completion of the 321-layer product and start mass production from the first half of 2025.

SK hynix

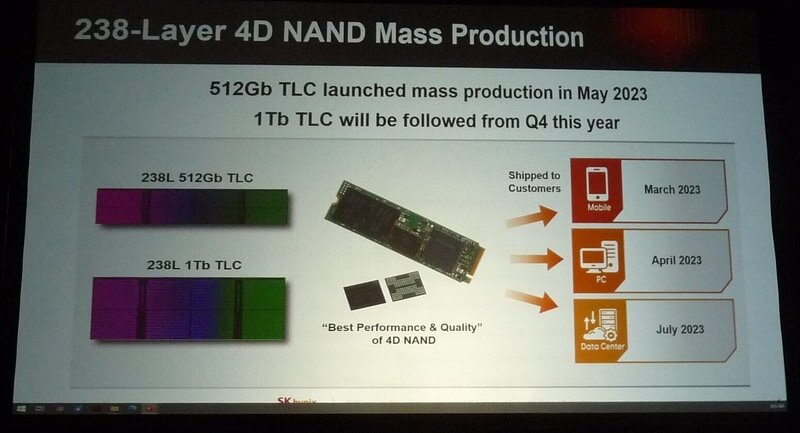

Ein früherer Start wäre auch sehr überraschend, denn die aktuelle V8-Generation mit 238 Layern ging erst im Juni 2023 in die Massenproduktion. Beim Nachfolger handelt es sich folglich um die V9-Generation, auf die es bereits im März im Rahmen der ISSCC einen Ausblick gab.

Mit technischen Eckdaten hält sich SK Hynix heute aber bedeckt, sodass abzuwarten bleibt, wie viele der zum ISSCC genannten Spezifikationen beim fertigen Produkt tatsächlich eintreffen werden. Änderungen am Design gibt es immer wieder, was den Vergleich und die Berichterstattung erschwert.

Im März hatte SK Hynix einen TLC-Chip mit „300+“ Layern und einer für diesen Typ extrem hohen Flächendichte von über 20 Gbit/mm² vorgestellt. Jetzt spricht SK Hynix von einer Verbesserung der „Produktivität“ um 59 Prozent. Damit ist in der Regel die Speichermenge (Bit pro Wafer) gemeint.

The 321-layer 1Tb TLC NAND comes with a 59% improvement in productivity, compared with the earlier generation of 238-layer 512Gb, thanks to the technology development that enabled stacking of more cells and larger storage capacity on a single chip, meaning the total capacity that can be produced on a single wafer increased.

SK Hynix

| Micron B58R | Kioxia/WD BiCS6 | Samsung V8 | Samsung V7 | SK Hynix V9 | SK Hynix V8 | SK Hynix V7 | YMTC | |

|---|---|---|---|---|---|---|---|---|

| Typ (Bit/Zelle) | TLC (3 Bit) | |||||||

| Kapazität | 1 Tbit | 1 Tbit | 512 Gbit | 1 Tbit | 512 Gbit | 1 Tbit | ||

| Planes | 6 | 4 | 6 | |||||

| Layer (WL) | 232 (2×116) | 162 (2×81) | 238 | 176 (2×88) | 321 (3×107) | 238 (2×119?) | 176 (2×88) | 232 |

| Die-Fläche | ~70 mm² | 98 mm² | 89 mm² | ~60 mm² | ? | 89 mm² | ~47 mm² | 68 mm² |

| Dichte | 14,6 Gb/mm² | 10,4 Gb/mm² | 11,5 Gb/mm² | 8,5 Gb/mm² | >20 Gb/mm² | 11,5 Gb/mm² | 10,8 Gb/mm² | 15 Gb/mm² |

| Read (tR) | ? | 50 µs | 45 µs | 40 µs | 34 µs | 45 µs | 50 µs | ? |

| Program | ? | 160 MB/s | 164 MB/s | 184 MB/s | 194 MB/s | 164 MB/s | 168 MB/s | ? |

| I/O | 2,4 Gb/s | 2,0 Gb/s | 2,4 Gb/s | 2,0 Gb/s | 2,4 Gb/s | 1,6 Gb/s | 2,4 Gb/s | |

Auch Leistungsprognosen macht SK Hynix heute keine. Doch sollte die neue Generation auch beim Lesezugriff und den Schreibraten deutliche Verbesserungen gegenüber dem 238-Layer-NAND mitbringen. Das NAND-Interface überträgt bis zu 2,4 Gbit/s.

Das nachfolgende Diagramm veranschaulicht, wo SK Hynix mit der grob prognostizierten Flächendichte im aktuellen Wettbewerb liegen würde. Zu Intels (jetzt Solidigm) 192-Layer-QLC-NAND fehlt aber noch ein Wert.

UFS 5.0 wird entwickelt

Auf dem Flash Memory Summit zeigt SK Hynix außerdem Enterprise-SSDs mit PCIe 5.0 und die neue Generation Embedded-NAND UFS 4.0. Der Start der Entwicklung der jeweiligen Nachfolger (PCIe 6.0 und UFS 5.0) wurde ebenfalls angekündigt.

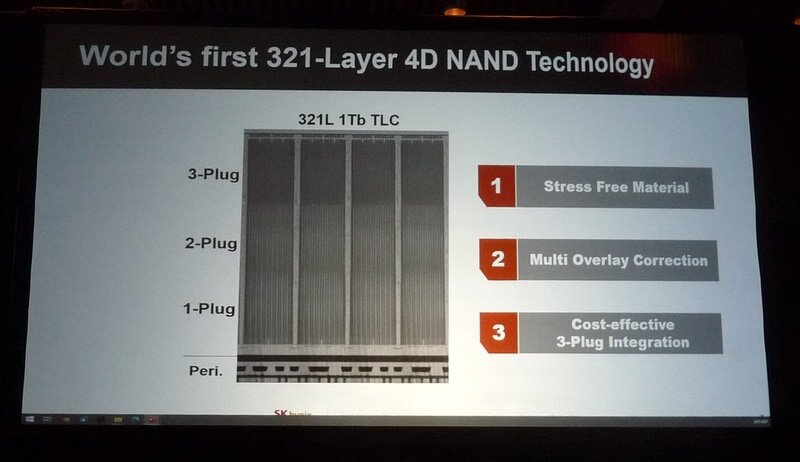

Die Website PC Watch liefert noch weitere Details zum 321-Layer-NAND, die SK Hynix auf dem Flash Memory Summit preisgegeben hat. So sollen pro Wafer 41 Prozent mehr Bit als beim Vorgänger herauskommen. Eine entsprechende Kostenreduzierung bedeutet dies aber nicht, denn da nun drei statt zuvor zwei Layer-Türme zusammengesetzt werden, sind zusätzliche Herstellungsschritte nötig.

Die Latenz beim Lesen soll gegenüber der V8-Generation um 13 Prozent niedriger ausfallen. Zudem werde 10 Prozent weniger Energie beim Lesen benötigt. Der Durchsatz beim Schreiben steige wiederum um 12 Prozent. Bestätigt werden in dem Bericht die Eckdaten der obigen Tabelle, die nun weiter ergänzt wurde.

Außerdem hat SK Hynix angekündigt, erst im vierten Quartal den 238-Layer-NAND in der Version mit 1 Terabit anzubieten. Bisher kommen 512-Gbit-Chips zum Einsatz. Wie Solidigm und Kioxia/WD forscht SK Hynix zudem an Penta-Level-Cell (PLC) NAND mit 5 Bit pro Speicherzelle. Derzeit weist vieles darauf hin, dass Solidigm der Markteinführung am nächsten ist. Denn die aus der ehemaligen Intel-Sparte entstandene Firma hat bereits vor einem Jahr eine erste SSD mit PLC als Prototyp gezeigt.

- 2 × 2,5 Bit = 5 Bit: SK Hynix will PLC-NAND so schnell wie TLC machen

- Flash Memory Summit: SK Hynix entwickelt 321-Layer-TLC-NAND

- Seagate Nytro 5060: Neue SSD-Generation mit bis zu 13 GB/s und 30 TB für Server

- +6 weitere News