Intel Core 2 Extreme QX9650 im Test: Mit Penryn auf und davon

Vorwort

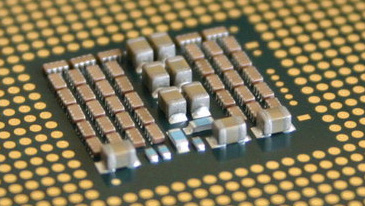

Mit dem heutigen Tag lässt Intel den ersten Prozessor der neuen Generation vom Stapel laufen, die bislang unter dem Codenamen „Penryn“ firmierte. Die größte Neuerung des Flaggschiffs Core 2 Extreme QX9650 mit „Yorkfield“-Kern, das sich zum Test in der Redaktion eingefunden hat, ist der Herstellungsprozess in der 45-nm-Technologie. Diese verspricht nicht nur eine geringere Leistungsaufnahme, sondern soll auch die Effizienz des gesamten Prozessors erhöhen. Parallel dazu bekommt der Neuling zusätzliche Instruktionen und einen auf 12 MB vergrößerten L2-Cache spendiert. Das Zusammenspiel soll die derzeitig (noch) unangefochtene Spitzenposition von Intel in quasi allen Bereichen der Desktop-Prozessoren sichern.

Im folgenden Abschnitt stellen wir den Core 2 Extreme QX9650 vor. Den Anfang macht der Überblick, anschließend analysieren wir die Architektur-Mikroarchitektur und stellen die 45-nm-Fertigung im Detail vor. Nach der Besprechung des Chipsatz-Supports lassen wir auf den folgenden 20 Seiten Zahlen für den neuen Prozessor sprechen.