„Ivy Bridge“: Mehr Details zu PCIe 3.0 und USB 3.0

Im Rahmen des IDF vor knapp zwei Wochen hatte Intel bereits diverse Dinge für „Ivy Bridge“ als Nachfolger der aktuellen „Sandy Bridge“ bestätigt. Jetzt gibt es nach den ersten Chipsatzplänen genauere Details zur Aufteilung der Ports hinsichtlich USB 3.0 sowie der Lanes bei PCI Express 3.0

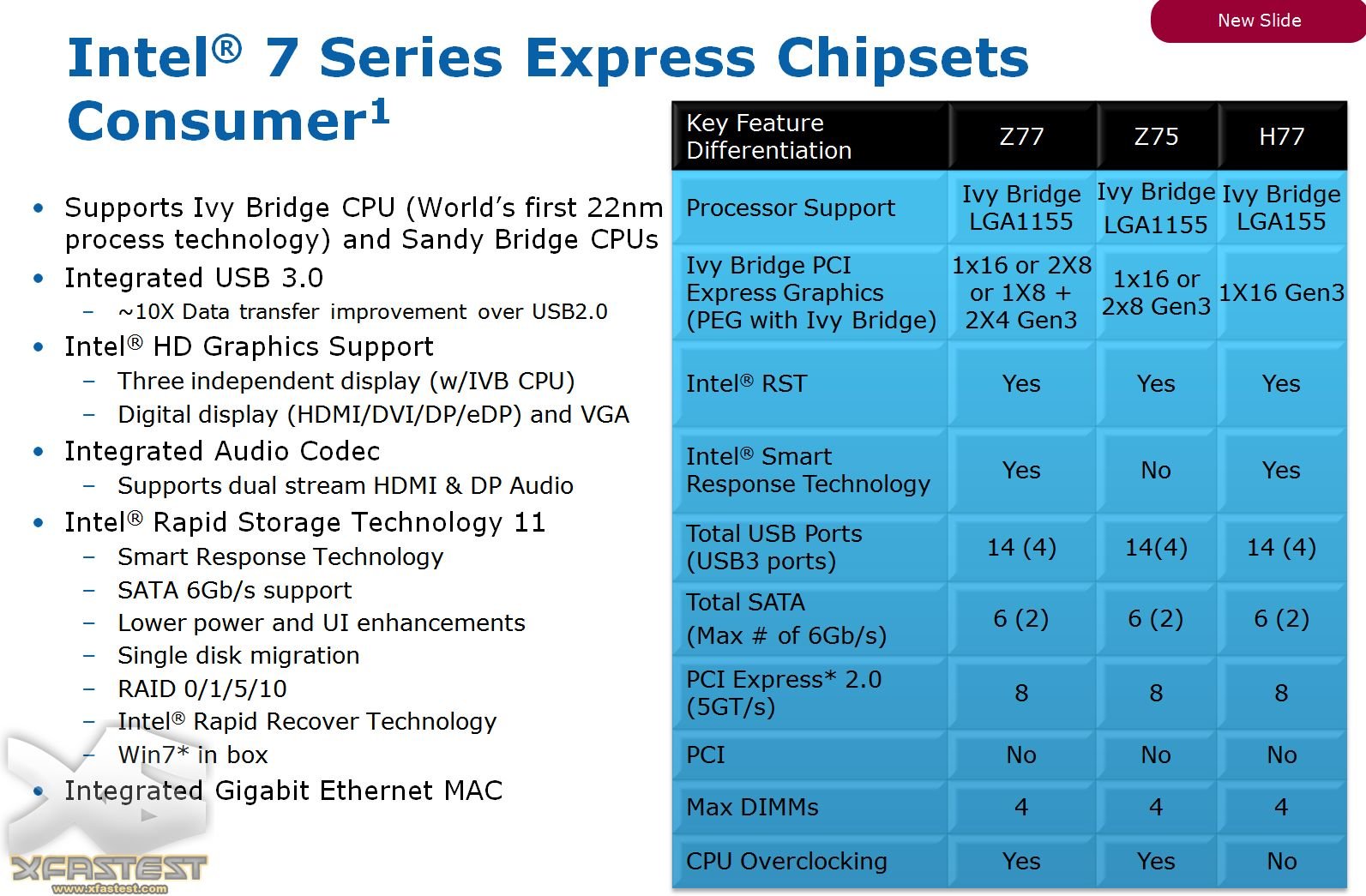

PCI Express 3.0 wird eine der wichtigsten Neuerungen für die Plattform. Während der bisher genutzte 8b10b-Code einen Overhead von 20 Prozent erzeugt, kommt bei PCI Express 3.0 ein 128b/130b-Code zum Einsatz, der dank einer knapp 25 Prozent höheren Effizienz die effektive Bandbreite im Vergleich zu PCI Express 2.0 verdoppeln soll. Die Verteilung der Lanes bleibt wie bei bisherigen Chipsätzen, Intel gibt dank der gesteigerten Bandbreite gegenüber PCI Express 2.0 aber auch mehr Spielraum. Die 16 Lanes, die der Prozessor im PCIe-3.0-Standard bereitstellt, werden wie üblich als vollwertiger einzelner Slot angeboten. Alternativ werden auch zwei Ports mit je acht Lanes versorgt. Die dritte Möglichkeit bietet drei Slots, von denen einer acht und zwei weitere jeweils vier Lanes bieten. Rein rechnerisch gesehen entsprechen die drei Slots einer heutigen Konfiguration von PCIe 2.0 mit x16, x8 und x8 – genau so arbeiten aktuelle Mainboards mit Triple-SLI oder CrossFireX. Der Z77-Chipsatz soll nach aktuellem Stand derjenige sein, der genau diese Möglichkeiten bieten wird. Der Z75-Chip hingegen bietet die klassische x16 beziehungsweise x8/x8-Aufteilung, während der H77 nur noch einen Slot ansprechen kann.

In Sachen USB 3.0 hatte sich Intel ebenfalls bereits zuletzt offiziell dazu geäußert, dies nativ zu unterstützen. Vier der maximal 14 Ports werden mit der neuen Plattform zum schnelleren Standard gehören. Ernüchternd ist bei der Betrachtung der Folien jedoch, dass weiterhin maximal zwei der sechs SATA-Ports mit 6 GBit/s angesprochen werden – bei den Business-Plattformen auf Basis des Q75 und B75 ist es gar nur ein Port.