TSMC Symposium 2022: Technologien für die Zukunft

2/2Marktführer und viele Patente

Die Marktführerschaft von TSMC in vielen Bereichen der Fertigung ist auch beim Ausbau des Personals sowie der finanziellen Mittel im Bereich Forschung und Entwicklung zu sehen. Hier hat sich vor allem zuletzt noch einmal deutlich etwas getan: Fast 8.000 Angestellte mit einem Budget von rund 4,5 Milliarden US-Dollar arbeiten bei TSMC in dem Bereich. Hervor brachte das bis einschließlich Mai 2022 mehr als 75.000 Patentverfahren und über 52.000 zugestandene Patente für das Unternehmen.

Die aktuell meistgenutzte Cashcow: N7 plus Abwandlungen

Die 7-nm-Familie N7 inklusive N6 und weiteren mehr von TSMC ist eine Erfolgsgeschichte sondergleichen. Bis zum Ende des Jahres soll die Marke von 400 Produkt-Tape-outs in einer dieser Nodes erreicht werden. N6 ist aktuell extrem gefragt, aber auch N7HPC für mehr Leistung steht noch ganz oben. Mit N6RF wird dieser Bereich ebenfalls weiterentwickelt, denn zukünftige Chips für die Kommunikation sind ebenso leistungsfähig, sollen jedoch dabei entsprechend wenig Strom verbrauchen.

N5/N4 folgt in großem Schritt hinterher

Die aktuelle Fertigungsstufe N5 mit den diversen Abwandlungen wie N5P, N5HPC, N4, N4P und N4X werden die Geschichte von N7 beinahe nahtlos fortsetzen können. Bisher hat TSMC in diesen Technologien über zwei Millionen Wafer belichtet und ausgeliefert. Bis zum Jahresende sollen es aufsummiert 150 Produkte sein, die ihr Tape-out in einem dieser Prozesse feiern.

Mit N3/N3E ab diesem Jahr mit Problemen in die Zukunft

Über den N3-Prozess von TSMC wurde auf ComputerBase bereits viel geschrieben. Denn hier hatte der Hersteller erstmals doch deutliche Probleme nicht nur mit dem Zeitplan, sondern auch mit dem Ergebnis. Heraus kommt nun quasi eine Übergangslösung alias N3, die ab Ende dieses Jahres gefertigt, dann jedoch binnen eines guten halben Jahres von N3E ersetzt werden soll.

N3E ist letztlich eine Korrektur für N3. Sie enthält laut TSMC „signifikante Änderungen“ in den Designrichtlinien und soll sowohl Ausbeute als auch Leistung verbessern. N3E soll letztlich dann auch die Grundlage für jeden folgenden Prozess werden. Das erklärt auch, warum TSMC auf allen Folien mit Zukunftsbezug stets nur noch von N3E spricht. N3 ist ein Problemkind, das man jedoch nicht komplett beiseiteschieben kann, es aber möglichst schnell tun wollen würde.

Über Anpassungen bei N3E wie FinFlex hatte ComputerBase bereits vor wenigen Tagen separat berichtet.

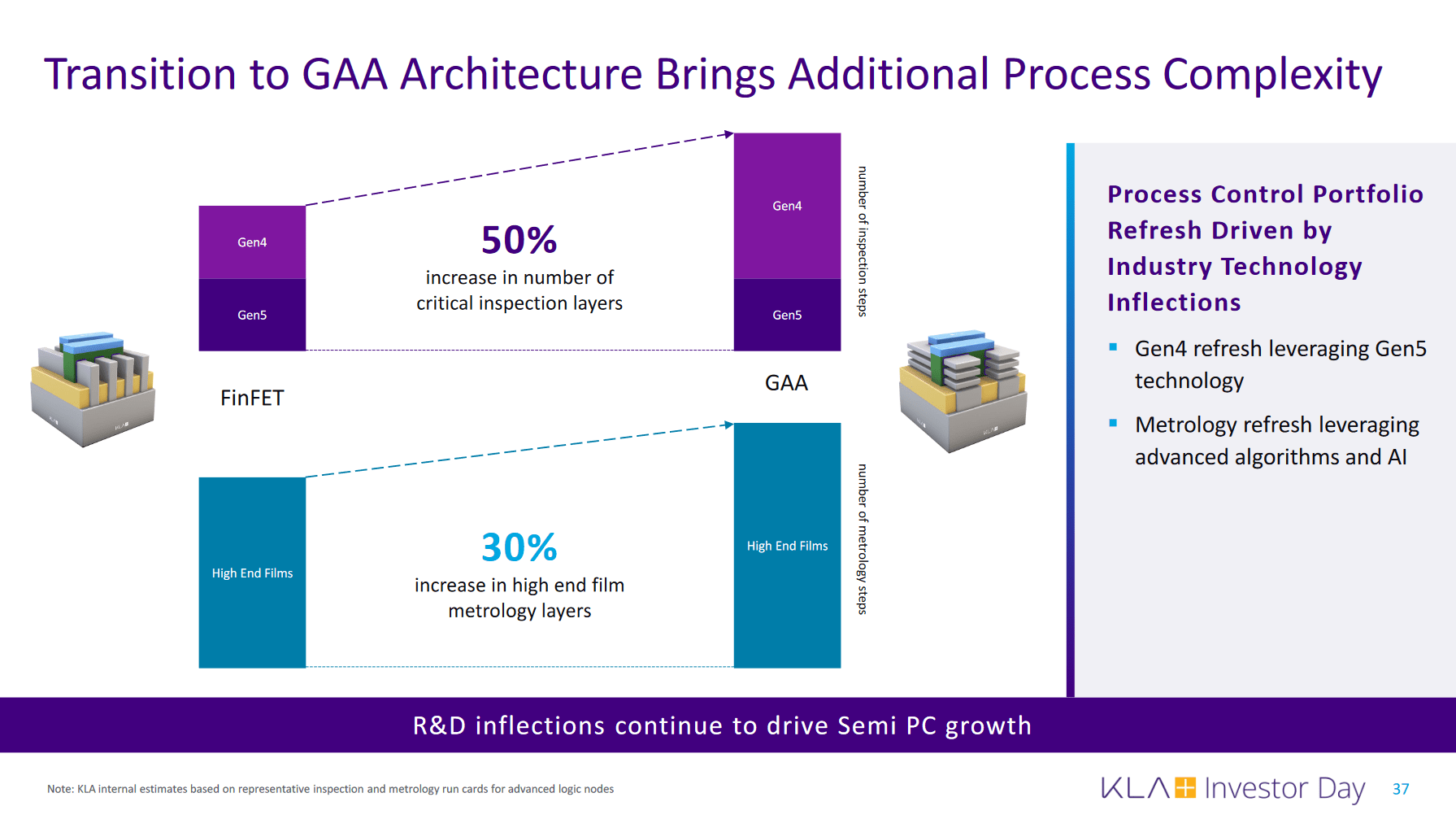

N2 mit Gate-All-Around und später auch „Backside Power Delivery“

Das richtig „große nächste Ding“ wird aber erst mit der Technologiestufe N2 kommen: Nanosheets, oft auch einfach Gate-All-Around (GAA) genannt, werden TSMCs Antwort ab dem Jahr 2025 auf die Frage sein, wie Chips weiterhin immer und immer leistungsfähiger werden können. Auch für diese Generation wird natürlich nichts Geringeres angestrebt als die beste Fertigung der Welt. Allerdings könnte es dann erstmals seit Jahren/Jahrzehnten wieder zu einem echten Showdown kommen: Samsungs 2-nm-GAA-Fertigung soll 2025 fertig sein, auch Intel will 20A und 18A, wie der Hersteller die Lösungen in dem Bereich nennt, schon ab Ende 2024 anbieten. So eine Konstellation im Markt gab es ewig nicht – wenn denn alle halbwegs zeitgleich auch wirklich die Serienreife erreichen.

Auf dem Papier sind die Zugewinne von N2 gegenüber N3E markant. Mehr Leistung, viel weniger Stromverbrauch (wenn gewünscht) und natürlich eine gestiegene Packdichte sprechen wie die vergangenen Fertigungsschritte für die Neuentwicklung. Doch es gibt auch Haken an der Sache: Es wird teuer. Und zwar in allen Bereichen – obwohl TSMC bei N2 noch auf klassisches EUV setzen wird. Aber für Nanosheets werden definitiv mehr Produktionsschritte benötigt als bei klassischen FinFETs, völlig neue Designrichtlinien sind vorab die Grundlage, erklärte Zhang und wird dabei von Aussagen anderer Firmen unterstützt.

Diese sollen jedoch alsbald in ersten Zügen bereitstehen. Die nun neue Kadenz von drei Jahren für einen vollen Node-Wechsel gibt TSMC hier zeitlichen Spielraum, den aber auch die Partner benötigen werden. Denn N2 ist ja nur der Anfang dieser neuen Ära, geplant sind später diverse darauf basierende Prozesse, wie es zuletzt eben gängig war. Im originalen N2 heißt es jedoch erst einmal: Gate-All-Around muss funktionieren. Darauf folgend in den Jahren kommen dann „Backside Power Delivery“ und „High-NA EUV“.

Nur die übernächsten Schritte sind gesetzt

„High-NA EUV“ ist eines dieser Stichworte, mit dem Intel, aber natürlich vor allem auch ASML als Fertiger der Systemtools für die Zukunft wirbt. Dass TSMC diese Technologie ebenfalls auf dem Schirm hat, war logisch, die Bestätigung folgte aber erst vor einigen Tagen ganz offiziell. Ab 2024 wird TSMC Tools für „High-NA EUV“ erhalten.

High-NA wirklich erst mal nur zur Forschung

Im Gespräch mit Kevin Zhang in Amsterdam macht er jedoch deutlich, dass dies definitiv erst einmal noch für die Forschung und Entwicklung gedacht ist. Es gibt bei TSMC noch keinen Starttermin für „High-NA EUV“. Die Kosten seien „enorm“, der Bonus insgesamt bisher aber noch nicht so ausgeprägt, weil die Tools selbst noch in der Entwicklung sind und sich erst beweisen müssen. Deshalb sagt TSMC zu der Thematik diplomatisch „N2 beyond“, also irgendwann nach N2 – und N2 setzt noch auf die bekannten Verfahren inklusive EUV.

Diese Einstellung wäre damit eine andere als zuletzt bei der Einführung von EUV in die Industrie. Hier war TSMC der Vorreiter, während Intel so lange wie möglich an klassischer Immersionslithografie festhalten wollte/musste – und bis heute nichts anderes nutzen kann. Dadurch ist Intel wiederum deutlich in den Fertigungsrückstand geraten und will nun bei „High-NA EUV“ den Spieß umkehren. Intel plant nämlich explizit schon mit dem Serieneinsatz von „High-NA EUV“ ab 2025, nur die Backup-Pläne sehen die Nutzung klassischer EUV-Technologie vor.

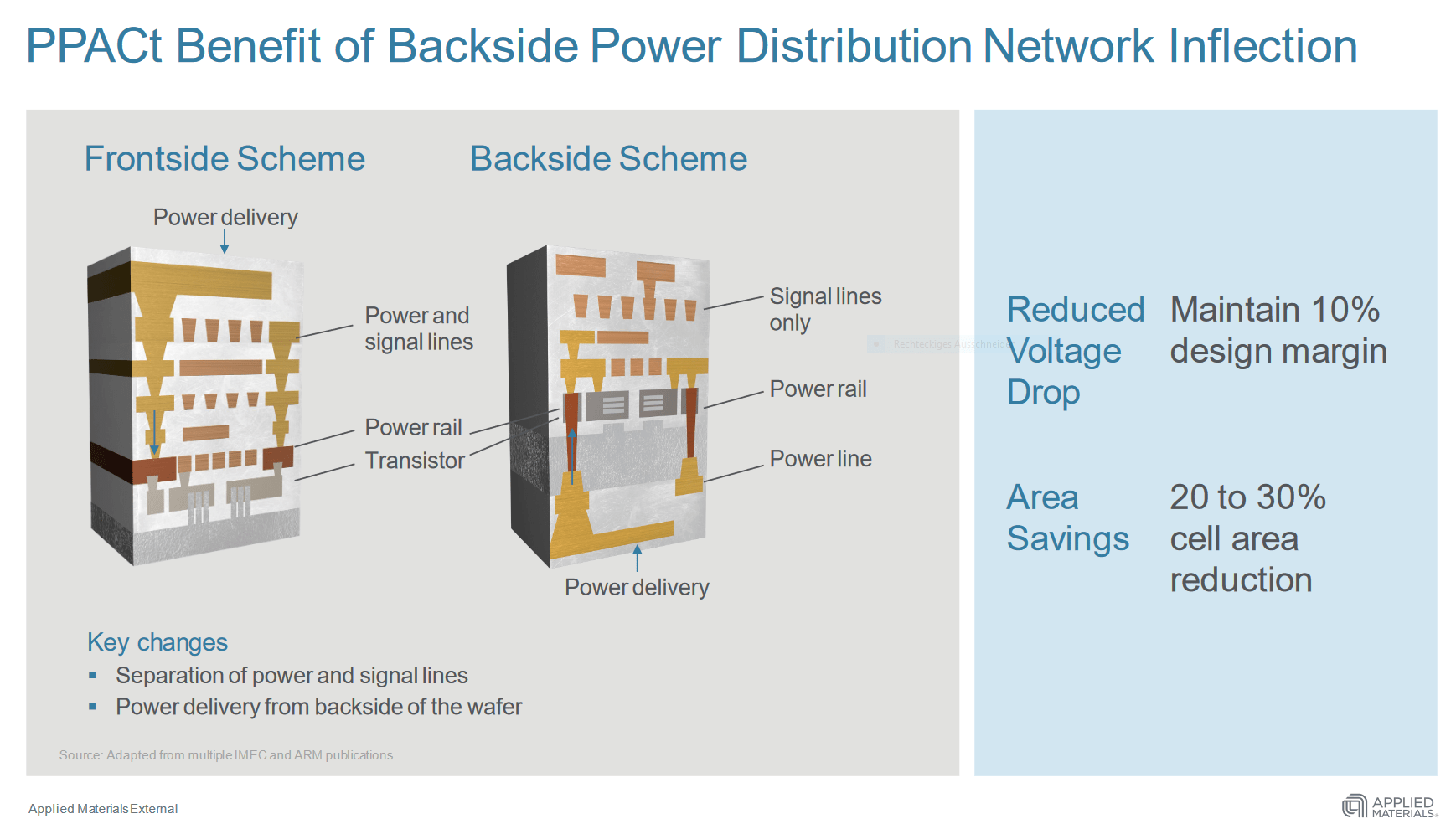

„Backside Power Delivery“ auch bei TSMC auf der Roadmap

Beim Thema „Backside Power Delivery“ oder PowerVIA, wie Intel die angepasste Technologie nennt, macht auch TSMC erste Schritte. Doch auch diese Thematik geht der Platzhirsch aus Taiwan verhaltener als Intel an. Diese Technologie wird später jedoch vermutlich im Rahmen eines verbesserten N2-Prozesses eingeführt, stellte TSMC in Amsterdam bereits klar. Als Vorteil einer solchen Lösung steht die klar verbesserte Effizienz. Mehr Leistung bei optimierter Leistungsaufnahme versprechen hier alle Forscher.

Das „Backside Power Delivery“ wird aber definitiv eine exklusive Sache für Nanosheets und die Zukunft sein, eine Rückportierung für FinFETs ist nicht geplant – Intel erprobt die Technik zumindest bei FinFETs. Denn auch hier stehen Kosten vor allem in der Anzahl der Arbeitsschritte im Fokus, sie sollen mit „Backside Power Delivery“ zusätzlich zu den ohnehin schon gestiegenen Schritten mit Nanosheets noch einmal deutlich zunehmen. Diese Komplexität sieht TSMC aktuell extrem kritisch, weshalb sie die Einführung nicht überstürzen wollen.

Die zum großen Teil noch auf dem Papier existenten Technologien wie GAA und „Backside Power Delivery“ gehen damit tendenziell zu Gunsten von Samsung und Intel statt TSMC aus. Doch heißt das noch lange nicht, dass TSMC technologisch ins Hintertreffen geraten wird. Die Umsetzung für den echten harten Industriealltag mit sehr guten Yields bei riesiger Menge war bei TSMC zuletzt deutlich realistischer als bei den anderen beiden Herstellern. Auf dem Papier gewinnen ist letztlich nur das eine, Produkte zu bauen und zu liefern eine andere Geschichte.

Und dann wäre da auch noch die Frage der Patente in dieser Richtung. Laut aktuellen Informationen sieht es hierbei für TSMC sogar deutlich besser aus als für die Mitbewerber. Am Ende ist also noch nicht sicher, wer das Rennen macht.

Und was kommt danach? Forschung, viel Forschung

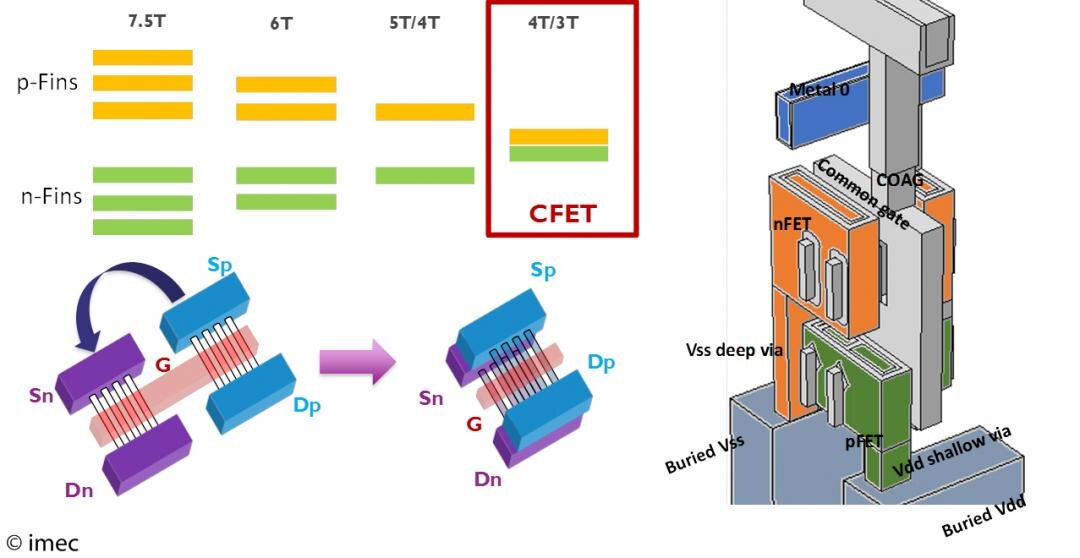

Complementary FETs (CFETs) sind eine der nun bereits oft genannten Möglichkeiten für die nahe Zukunft, aber TSMC betonte, dass sie noch nicht so weit seien. Auch an neuen 2D-Materialien wird wie immer geforscht und letztlich werden die ebenfalls schon lange in der Theorie bekannten „Carbon Nanotubes“ (CNT) weiter verfolgt. Für all diese Pläne gehen allerdings schnell fünf bis zehn oder noch mehr Jahre ins Land. TSMC verfolgt sie deshalb nicht allein, alle Branchengrößen sind mit renommierten Instituten hier in unterschiedlicher Weise involviert.

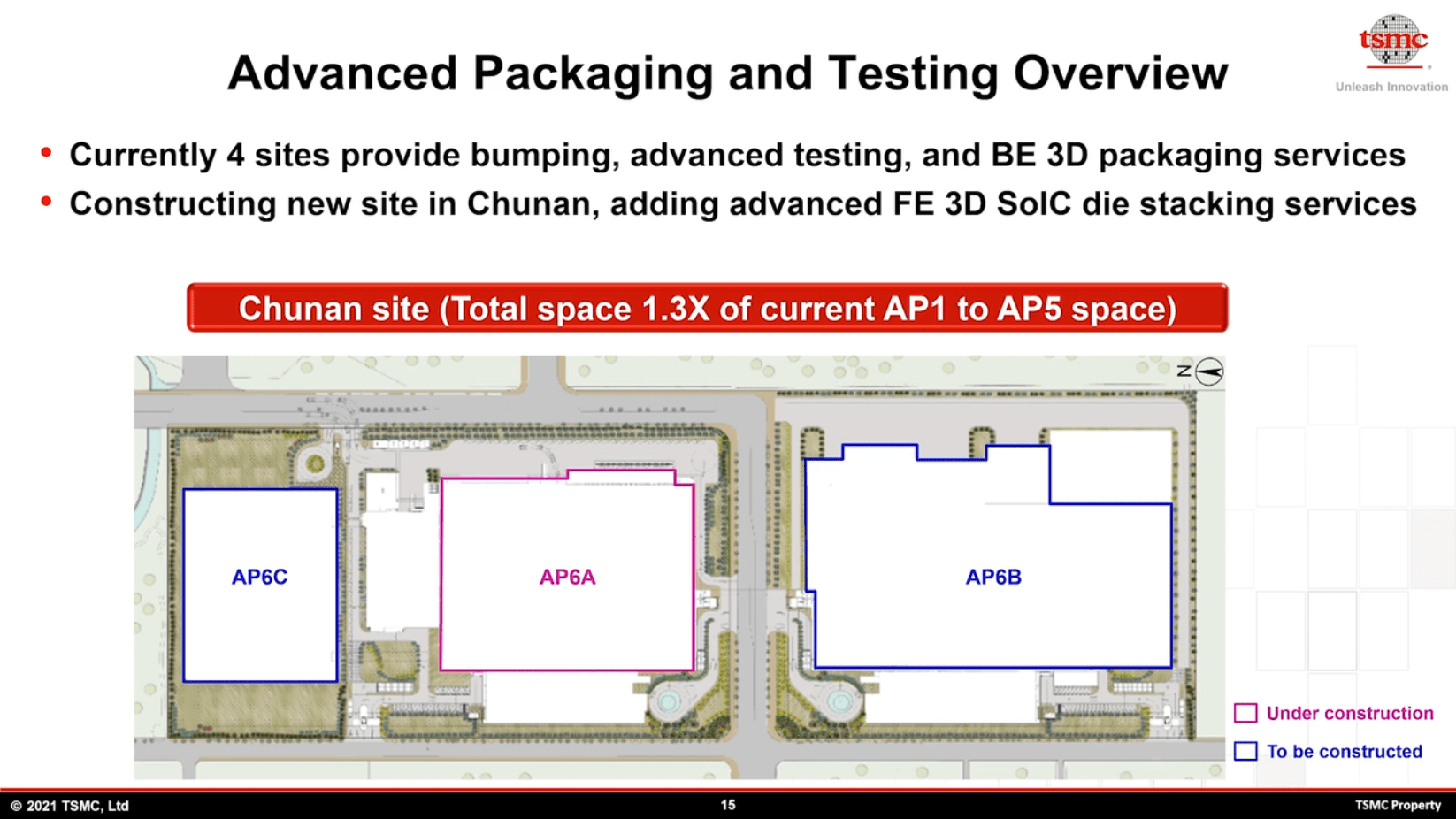

Stacking zur Rettung: Bis 2026 extremer Ausbau

Bereits vor einem Jahr berichtete ComputerBase vom damals virtuellen TSMC Symposium ausführlich über die Thematik Stacking bei TSMC. Das neue 3D-Fabric ist spätestens seit AMDs Nutzung als 3D-V-Cache sichtbar für alle – und das war nur der Anfang. Die Kapazität für „Advanced Packaging“ soll in diesem Jahr ungefähr das Dreifache von dem erreichen, was noch vor drei Jahren zur Verfügung stand. Richtig los geht es trotzdem jetzt erst: Bis 2026 soll die Kapazität auf über das 20-Fache ausgebaut werden.

Allein das zeigt, wie wichtig das Packaging in Zukunft noch werden wird und auch, wie viele unterschiedliche Produkte in Zukunft auf solch ein Verfahren zurückgreifen werden. Die Wachstumsraten für das 3D-Stacking liegen laut TSMC bei über 20 Prozent pro Jahr. Aktuell wird die neue Packaging-Fabrik in Zhunan hochgefahren. Die erste Phase des Baus wird in diesem Jahr die Produktion beginnen und 2023 dann voll zur Verfügung stehen. Ist der Komplex einmal fertiggestellt, wird er mal als doppelt so viel Kapazität bieten wie alle anderen Packaging-Zentren zusammen.

Als nächster Schritt wird beim 3D-Stacking die Node-Variante N5 auf N5 gestapelt, N7 auf N7 war der erste erfolgreiche Versuch. Auch hier wird AMDs nächster Zen-4-Prozessor als erster Kandidat heiß gehandelt, wurde er doch schon von AMD selbst bestätigt und auch CDNA 3 wird Chips in N5 stapeln. Die Basistechnologie bleibt dabei identisch, doch die zweite Generation bringt schon einige Optimierungen mit, beispielsweise ein von 9 auf 6 Micron verringerter Abstand der Kontaktpunkte.

Bereits ab 2024 soll die N3-Technologie auf Basiswafer in N5- oder auch N7-Technologie gesetzt werden können. Auf Nachfrage bei TSMC, welche Beschränkungen es denn gibt, hieß es, „eigentlich keine“. So wird beispielsweise N5 auf N7 genauso funktionieren wie andere Zwischenschritte. Es dürfte einfach auf das Produkt ankommen.

Umweltschutz: Vor allem aufs Wasser kommt es an

Die grüne Halbleiterherstellung schreibt sich TSMC auf die Fahne, zuletzt war das aber auch nur bedingt gelungen. Denn die neuen Megafabriken schlucken extrem viel Energie und haben einen riesigen Wasserbedarf. Die fortschrittlicheren Nodes und Maschinen sind zwar effizienter, verbrauchen aber dennoch erst einmal noch mehr als vorangegangene Systeme. Das sorgte auch im Heimatland zuletzt für Diskussionen, denn bei der Wasserkrise vor einem Jahr waren teilweise Anwohner ohne Wasser, während die Fabriken kaum oder keine Probleme hatten.

Um dies etwas zu beruhigen hat TSMC eine erste Wasseraufbereitungsanlage außerhalb seines eigenen Geländes gebaut. Sie soll dieses Jahr in Betrieb genommen werden und schafft zu Beginn über 400.000 Liter pro Stunde. Drei weitere Werke sollen folgen. Im Jahr 2030 will TSMC seinen Frischwasserbedarf pro Produktionseinheit auf 60 Prozent des Levels von 2020 bringen. Über 60 Prozent aufbereitetes Wasser sind auch das Ziel der geplanten Anlagen. 80.000 Gallonen pro Minute, umgerechnet mehr als 18 Millionen Liter die Stunde, sollen die Aufbereitungsanlagen dann bringen und TSMCs Werke zu einem großen Teil versorgen.

Auch die Emissionen will TMSC eindämmen, hier wird es aber ebenfalls ein sehr langer Weg. Ab 2025 will das Unternehmen erst mal keine Steigerung mehr bei neuen Emissionen angehen, ab 2030 dann langsam auf das Niveau von 2020 zurückfallen. Das große Ziel „Zero Emissions“ ist erst für 2050 angesetzt.

Rosiger Ausblick voraus

Und so schloss TSMC seine Ausführungen in Amsterdam mit einem Spruch, den viele Unternehmen aktuell gern bringen: „Die beste Zeit liegt noch vor uns“. Daran bei TSMC nicht zu glauben, ist aktuell eigentlich auch nicht möglich.

Der Auftragsfertiger aus Taipeh, Taiwan, ist definitiv etwas vorsichtiger geworden, was er sich angesichts der Position an der Spitze auch leisten kann. Das heißt aber nicht, dass TSMC die nächsten Tendenzen verschläft. Selbst wenn der aktuelle Platzhirsch gegenüber den einzigen beiden Mitbewerbern an der Spitze, Intel und Samsung, mal irgendwo in Rückstand geraten würden, kann ihnen hinsichtlich der Kapazität derzeit und auch in naher Zukunft keiner auch nur ansatzweise das Wasser reichen. Und so erklärte selbst Intel-CEO Pat Gelsinger: Taiwan (TSMC) kann keiner ersetzen. Intels Anstrengungen zielen eher auf mehr Balance im System, um die Abhängigkeit von einem großen Anbieter zu verringern. Ehe Intel jedoch dort halbwegs mitmischt, dürfte es das Ende dieser Dekade sein.

ComputerBase hat die Informationen beim TSMC Symposium 2022 in Amsterdam erhalten. Die Kosten für die Reise wurden mehrheitlich von ComputerBase übernommen.

Dieser Artikel war interessant, hilfreich oder beides? Die Redaktion freut sich über jede Unterstützung durch ComputerBase Pro und deaktivierte Werbeblocker. Mehr zum Thema Anzeigen auf ComputerBase.