Heyho meine lieben,

hevorgerufen durch eine aktuelle Situation eines Arbeitskollegen bin ich mir bei der Ausstattung des genannten Mainboards nicht zu 100% sicher, wie genau sich die Lane-Verteilung verhält.

Folgender Sachverhalt ist gegeben:

Wir wissen, dass Ryzen 7000-Prozessoren derzeit 28 PCIe 5.0-Lanes zur Verfügung stellen, von denen vier Lanes für die Kommunikation mit dem Chipsatz abgestellt sind. Es bleiben netto also 24 PCIe 5.0-Lanes zur Verfügung.

Der X670E-Chipsatz stellt seinerseits wiederum bis zu 44 Lanes zur Verfügung, darunter bis zu 24 Lanes für PCIe 5.0, 12 Lanes für PCIe 4.0 und 8 Lanes für PCIe 3.0. Diese Angaben sind "Maximalangaben" und obliegen dem Willen des Mainboard-Herstellers, das ist mir bekannt.

Beides gibt es u.A. auch hier auf ComputerBase im Auftakt-Artikel zu den Chipsätzen nachzulesen:

https://www.computerbase.de/artikel...00-amd-x670e-x670-b650e-b650-vergleich.82014/

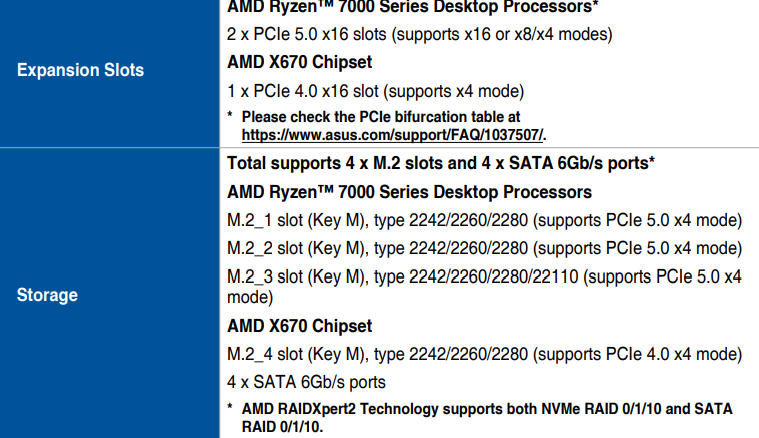

Mein Arbeitskollege hat sich ein ASUS ROG Strix X670E-E Gaming WiFi ausgeschaut - mal vom Preis abgesehen ist das ein hübsches Stück Technik, an dem es nur wenig auszusetzen gibt. Das Board besitzt neben dem obligatorischen PCIe 5.0 x16-Slot für Grafikkarten insgesamt vier weitere M.2-NVME-Slots, von denen drei mit PCIe 5.0 x4 betankt werden können, einer mit PCIe 4.0 x4.

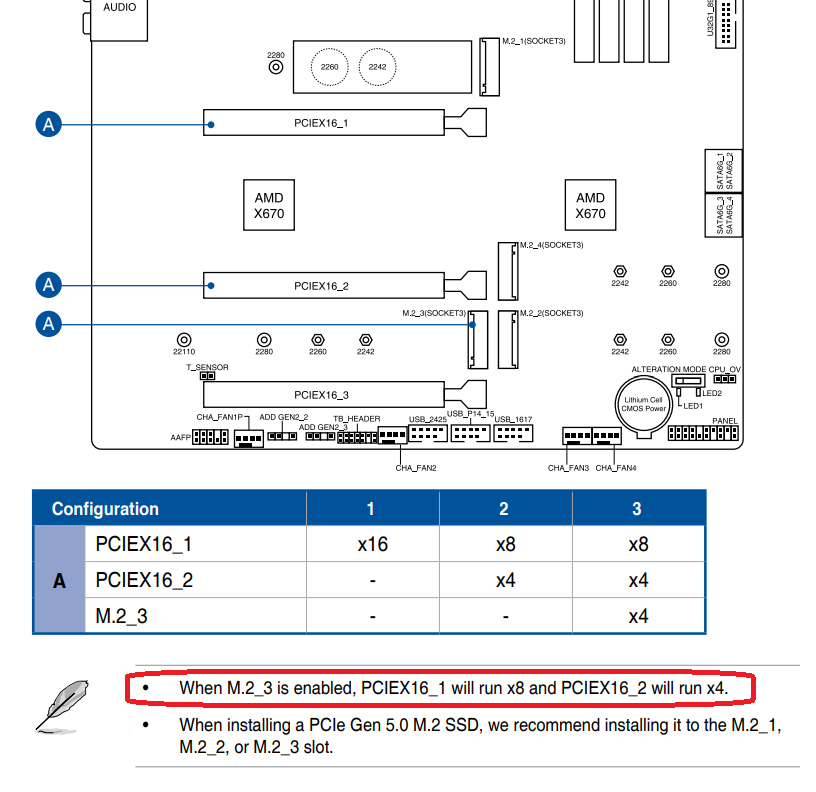

Laut Seite 7 im Handbuch sind neben dem PCIe x16-Slot für die Grafikkarte drei der vier M.2-Slots ebenfalls an die CPU und NICHT an den Chipsatz angebunden.

Jetzt rechnen wir mal zusammen: Die Grafikkarte belegt 8 Lanes, drei M.2-SSDs belegen 12 Lanes, somit wären insgesamt 20 der "bis zu 24 nutzbaren" Lanes belegt.

ASUS geht hier jedoch einen anderen Weg. Laut Seite 12 im Handbuch sieht die Sachlage nämlich so aus, dass:

... selbst, wenn also nur der M.2_3, also lediglich dieser eine spezielle Slot belegt ist, können für die Grafikkarte schon nur noch 8 Lanes zur Verfügung gestellt werden.

An dieser Stelle frage ich mich:

Was genau hat ASUS sich hierbei gedacht? Wieso kann man selbst bei einem 500 Euro-Mainboard nicht die Lanes so sinnvoll verteilen, dass die M.2 über den Chipsatz laufen, der in X670E-Ausführung doch mehr als genug Lanes zur Verfügung stellt? Sowohl Prozessor (wie gesagt, 24+4) als auch X670E-Chipsatz bieten doch Lanes im Überfluss, was ist denn hier schiefgelaufen?

Mein Arbeitskollege hat nun jedenfalls seine M.2-Vollbestückung des Mainboards geändert und wird das "Datengrab" als SATA-SSD ausführen, eben aufgrund dieser Thematik.

Von der Sinnhaftigkeit, sich ein Board für 500 Euro zu kaufen und das Board mit M.2-SSDs zuzukleistern oder nicht, das ist an dieser Stelle vollkommen irrelevant. Es geht einfach nur darum, dass man tatsächlich schon sehr viel Geld in die Hand nimmt und dann offensichtlich aufgrund von absichtlich gefällten Entscheidungen in der Nutzung und Bandbreite eingeschränkt wird.

Es soll hier nicht darüber diskutiert werden, ob (Stand Jetzt) 8 Lanes an PCIe 5.0 ebenfalls für Grafikkarten ausreichen, das interessiert nicht. Es geht mir rein um die offensichtlich künstliche Beschneidung der Lanes bzw. deren Verteilung und das will mir an dieser Stelle nicht in den Kopf.

Vielleicht übersehe ich hier ja auch irgend etwas und ihr könnt mir auf die Sprünge helfen.

Vielen Dank im Voraus.

hevorgerufen durch eine aktuelle Situation eines Arbeitskollegen bin ich mir bei der Ausstattung des genannten Mainboards nicht zu 100% sicher, wie genau sich die Lane-Verteilung verhält.

Folgender Sachverhalt ist gegeben:

Wir wissen, dass Ryzen 7000-Prozessoren derzeit 28 PCIe 5.0-Lanes zur Verfügung stellen, von denen vier Lanes für die Kommunikation mit dem Chipsatz abgestellt sind. Es bleiben netto also 24 PCIe 5.0-Lanes zur Verfügung.

Der X670E-Chipsatz stellt seinerseits wiederum bis zu 44 Lanes zur Verfügung, darunter bis zu 24 Lanes für PCIe 5.0, 12 Lanes für PCIe 4.0 und 8 Lanes für PCIe 3.0. Diese Angaben sind "Maximalangaben" und obliegen dem Willen des Mainboard-Herstellers, das ist mir bekannt.

Beides gibt es u.A. auch hier auf ComputerBase im Auftakt-Artikel zu den Chipsätzen nachzulesen:

https://www.computerbase.de/artikel...00-amd-x670e-x670-b650e-b650-vergleich.82014/

Mein Arbeitskollege hat sich ein ASUS ROG Strix X670E-E Gaming WiFi ausgeschaut - mal vom Preis abgesehen ist das ein hübsches Stück Technik, an dem es nur wenig auszusetzen gibt. Das Board besitzt neben dem obligatorischen PCIe 5.0 x16-Slot für Grafikkarten insgesamt vier weitere M.2-NVME-Slots, von denen drei mit PCIe 5.0 x4 betankt werden können, einer mit PCIe 4.0 x4.

Laut Seite 7 im Handbuch sind neben dem PCIe x16-Slot für die Grafikkarte drei der vier M.2-Slots ebenfalls an die CPU und NICHT an den Chipsatz angebunden.

Jetzt rechnen wir mal zusammen: Die Grafikkarte belegt 8 Lanes, drei M.2-SSDs belegen 12 Lanes, somit wären insgesamt 20 der "bis zu 24 nutzbaren" Lanes belegt.

ASUS geht hier jedoch einen anderen Weg. Laut Seite 12 im Handbuch sieht die Sachlage nämlich so aus, dass:

... selbst, wenn also nur der M.2_3, also lediglich dieser eine spezielle Slot belegt ist, können für die Grafikkarte schon nur noch 8 Lanes zur Verfügung gestellt werden.

An dieser Stelle frage ich mich:

Was genau hat ASUS sich hierbei gedacht? Wieso kann man selbst bei einem 500 Euro-Mainboard nicht die Lanes so sinnvoll verteilen, dass die M.2 über den Chipsatz laufen, der in X670E-Ausführung doch mehr als genug Lanes zur Verfügung stellt? Sowohl Prozessor (wie gesagt, 24+4) als auch X670E-Chipsatz bieten doch Lanes im Überfluss, was ist denn hier schiefgelaufen?

Mein Arbeitskollege hat nun jedenfalls seine M.2-Vollbestückung des Mainboards geändert und wird das "Datengrab" als SATA-SSD ausführen, eben aufgrund dieser Thematik.

Von der Sinnhaftigkeit, sich ein Board für 500 Euro zu kaufen und das Board mit M.2-SSDs zuzukleistern oder nicht, das ist an dieser Stelle vollkommen irrelevant. Es geht einfach nur darum, dass man tatsächlich schon sehr viel Geld in die Hand nimmt und dann offensichtlich aufgrund von absichtlich gefällten Entscheidungen in der Nutzung und Bandbreite eingeschränkt wird.

Es soll hier nicht darüber diskutiert werden, ob (Stand Jetzt) 8 Lanes an PCIe 5.0 ebenfalls für Grafikkarten ausreichen, das interessiert nicht. Es geht mir rein um die offensichtlich künstliche Beschneidung der Lanes bzw. deren Verteilung und das will mir an dieser Stelle nicht in den Kopf.

Vielleicht übersehe ich hier ja auch irgend etwas und ihr könnt mir auf die Sprünge helfen.

Vielen Dank im Voraus.