FreakInCage

Ensign

- Registriert

- März 2008

- Beiträge

- 171

Danke!

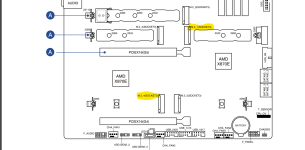

Ach mist! Ich habe nicht richtig hingeschaut! Ich habe ein ROG STRIX X870E-E

Anleitung hier

Da auch für eine Lexar NM790 PCIe 4.0 unten die Slots verwenden?

Ergänzung ()

Ach mist! Ich habe nicht richtig hingeschaut! Ich habe ein ROG STRIX X870E-E

Anleitung hier

Da auch für eine Lexar NM790 PCIe 4.0 unten die Slots verwenden?

Zuletzt bearbeitet: