bensen schrieb:

Es will halt keiner mehr die FinFET Prozesse unter 8LPP nutzen.

Das ist Unsinn.

In Q1 2023 hat TSMC 49 % des Umsatzes mit Prozessen ab 16 nm und größer gemacht. Bei 10 nm macht TSMC Umsätze in homöopathischen Dosen.

Und die Umsätze mit den klassischen Prozessen gingen in Q1 2023 erheblich weniger zurück als die Umsätze mit 7 und 5 nm.

Auch Samsung wird noch ordentlich Umsatz mit den alten Prozessen machen. Natürlich hätte Samsung Foundry gerne Kunden für ihre modernen Nodes. Aber gegen die Auslastung ihrer altem Nodes haben sie sicher nichts.

bensen schrieb:

Naja alles bis 4LPP ist ja mehr oder weniger 7nm. Ist alles nur kreative Namensgebung.

Bei Samsung Foundry ist fast alles kreativ. Namen, der Starttermin der HVM, die Daten der Zellen ...

Nur beim Lösen ihrer Prozessprobleme sind sie nicht kreativ.

bensen schrieb:

Naja es kann nicht mit N5 konkurrieren.

Performance und Effizienz:

https://twitter.com/Golden_Reviewer/status/1547944270992027648

Qualcomm hat den SD8 Gen1 (Samsung Foundry) ohne Änderung als SD8+ Gen1 bei TSMC fertigen lassen. Also zeigt das Verhältnis von SD8 Gen1 zu SD8+ Gen1 ungeschminkt die Leistungsfähigkeit der Prozesse.

IC Knowledge (Scotten Jones) schreibt in seinem

Blogbeitrag über die TSMC Vorträge auf der IEDM 2022 im letzen Absatz:

Eine Frage, die Sie sich als Leser vielleicht stellen, ist, wie dieser Prozess im Vergleich zu Samsungs 3nm-Prozess abschneidet. TSMC verwendet immer noch FinFETs, während Samsung zu GAA - HNS, genannt Multibridge - übergegangen ist.

Nach unseren Berechnungen sind die dichtesten Logikzellen von TSMC bei 5 nm 1,30 Mal so dicht wie die dichtesten Logikzellen von Samsung. Betrachtet man die TSMC-Dichtewerte in Abbildung 6, so sind die 2-2-Fin-Zellen 1,39x dichter als 2-2-Zellen in 5nm, und die 2-1-Zellen bieten eine 1,56x höhere Dichte. Samsung hat zwei Versionen von 3nm, wobei die SF3E (3GAE)-Version 1,19x dichter als 5nm und die SF3 (3GAP)-Version 1,35x dichter als 5nm ist und damit weiter hinter die branchenführende Dichte von TSMC zurückfällt. Ich glaube auch, dass TSMC bei 3nm eine bessere Leistung und einen etwas besseren Stromverbrauch hat, obwohl Samsung die Leistungslücke wahrscheinlich aufgrund des HNS-Prozesses geschlossen hat.

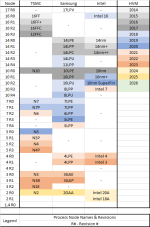

In einem älteren Blogbeitrag von 2019 hat er folgende Tabellen über die HD-Zellen der 7 und 5 nm Prozesse veröffentlicht. Leider habe ich keinen Link zum Blogbeitrag:

M2P x Tracks ergibt die Cell High

Cell High x CPP ergibt die Fläche der Zelle

Die Transistordichte ist etwas komplexer, hier wird eine Metrik von Intel verwendet die verschiedene Zellen umfasst. Nämlich zu 40 % NAND Gatter und zu 60 % Scanned Flip Flops.

Bei 7 nm war Samsung so ziemlich gleich auf, bei 5 nm sind die zurückgefallen.

Aktuellere Daten die ich gesehen haben sind nicht vollständig, d. h. sie gehen oft nur auf den CPP ein.

Die Blogbeiträge von Scotten Jones waren IMO auch eine Werbung für seine Firma. Die hat er inzwischen an

TechInsights verkauft. Sein

Produkt (Preismodelle aller Fabs) wird dort weitergeführt.