Smagjus schrieb:

Ich bin derweil durch Zufall an ein DDR4 Kit mit passendem Unterbau gelangt. Eventuell ist der Vergleich zwischen meinem früheren Kit interessant. Ich finde allerdings meinen Aida64 Post von vorher nicht mehr. Ich weiß noch, dass der alte RAM brachte es auf 58000MB/s im lesen brachte.

Vorher:

2400MHz mit CL10. 58000MB/s lesend.

Nachher:

2400MHz mit CL15. 52000MB/s lesend.

Zunächst einmal ist es nicht unproblematisch, DDR3 mit DDR4 zu vergleichen, denn:

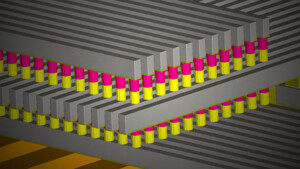

Die Länge der Wordlines ist bei DDR4 um ein Viertel reduziert. Die Anzahl jedoch nur verdoppelt.

Die kleineren Wordlines können mit 20ns schon doppelt so schnell entleert und befüllt werden wie DDR3 mit 40ns.

Eine "Bank" speichert also halb so viele Daten wie DDR3, demgegenüber hat DDR4 doppelt so viele Bänke die in Gruppen zusammengefasst sind.

Über die Organisation von Bankgroups wird eine schnellere Weitergabe der Daten von einer Bank über den Prefetcher zum Datenbus garantiert.

Eine DDR3 Bank muss pro Wordline 2048 bitlines öffnen, lesen, schreiben. Eine DDR4 Bank nur 512 bitlines. Das geht wesentlich schneller und es werden nicht mehr so große Datenpakete gesendet.

Die Prefetcher wurden nicht vervielfacht, um dem Problem der großen Datenmenge entgegenzuwirken und so die Zeiten (waitstates) nicht zu erhöhen. Dafür hat DDR4 Bankgroups, wodurch man die Taktraten deutlich erhöhen kann. Die Breite des Datenbusses bleibt aber gleich. Die CPU muss nicht mehr so lange warten bis Daten bereitgestellt werden. Sie sind bereits vom BUS vorgespeichert. Schon darin liegt ein erheblicher Geschwindigkeitsvorteil.

Nun zum Datendurchsatz.

Die Speichertransferrate berechnet sich bei DDR3 und DDR4 wie folgt:

Speicherzellentakt * 64 (Bit pro Übertragung * prefetch) * 8 / 8 Bit = Speichertransferrate in MByte/s

Mit DDR3 2400 MHz bzw. DDR4 2400 MHz wären das: 300*64*8/8= 19,20 GB/s pro Modul

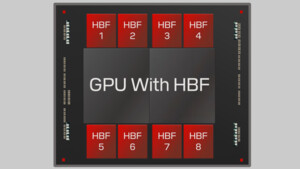

Mein System hat einen 3000 MHz Speicher. Das sind in diesem Fall 375 MHz*64*8/8= 24,00 GB/s pro Modul. Aus diesem Grund zeigt AIDA64 eine Speicherbandbreite des gesamten Systems (4 Module * 24 GB/s) mit 96.000 MB/s an:

Davon zu unterscheiden ist die Zugriffszeit.

tCL+tRCD/Taktfrequenz= 2(tCL*tRCD)/effektive Taktfrequenz.

Im ersten Beispiel (CL10 [der tRCD-Wert wird von mir mit 12 unterstellt]) sind das:

10+12/1200 MHz= 2(10+12)/2400 MHz= 0,018333

Im zweiten Beispiel (CL 15 [der tRCD-Wert wurde mit 15 unterstellt]) sind das:

15+15/1200 MHz=2(15+15)/2400 MHz= 0,025

Wie man sieht, ist die Zugriffszeit länger. Daher ist auch der Durchsatz insgesamt etwas niedriger.