Intel Alder Lake: 19 % höhere IPC, Hardware-Scheduler, DDR5 und mehr

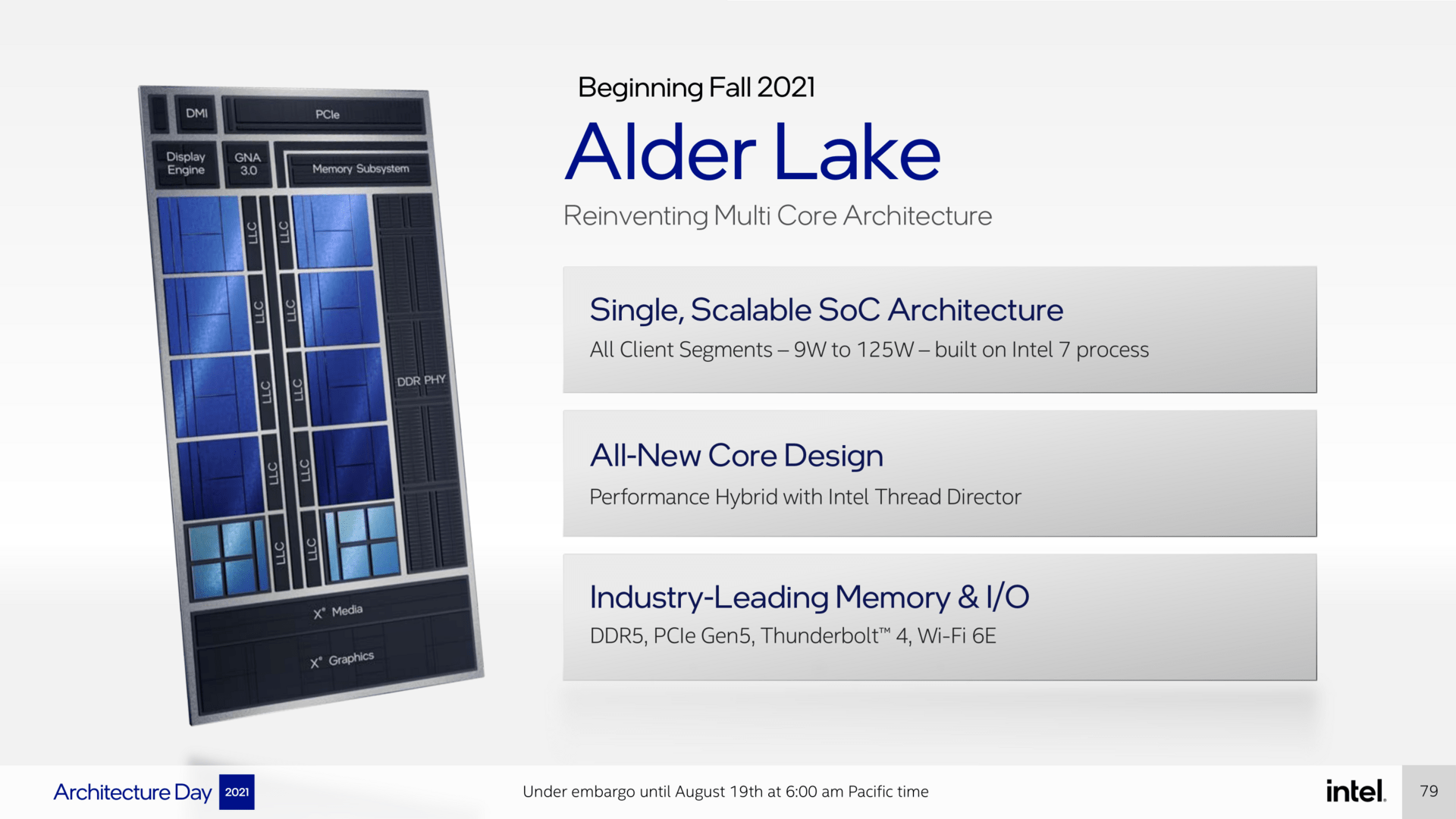

Zum Architecture Day 2021 hat Intel umfangreiche Details zur größten CPU-Neuvorstellung des Jahres geteilt: Alder Lake, Intels erste große Hybrid-CPU. Kleine und große Kerne werden hier inklusive iGPU, DDR5 und PCIe 5 in neuer Fertigung „Intel 7“ in einem Package vereint. Damit das aufgeht, hat Intel viel am Scheduling getan.

Hybrid: Vom gefloppten Experiment zum Zugpferd

Auf das fehlgeschlagene erste Hybrid-CPU-Experiment Lakefield folgt in diesem Jahr der von Intel angestrebte Durchbruch. Der Hybrid-Ansatz wird bei Intel im Desktop und Notebook vorerst zum Standard.

Dafür ging Intel quasi zurück ans Reißbrett und entwarf fast alles neu, angefangen bei den Prozessorkernen über die I/O-Einheiten, den Speicher und das Power-Management. Einige Neuigkeiten sind auf dem Papier echte Raffinessen, die es bisher so nicht gab und die den Erfolg von Alder Lake herbeiführen sollen, man könnte sogar sagen das Zünglein an der Waage sind.

Im Rahmen eines aufgrund der Corona-Situation noch einmal abgespeckten Architecture Day hat Intel am Mittwoch in Berlin erste Einblicke gewährt, die ComputerBase nachfolgend zusammenfasst.

Das ist das neue hybride CPU-Design

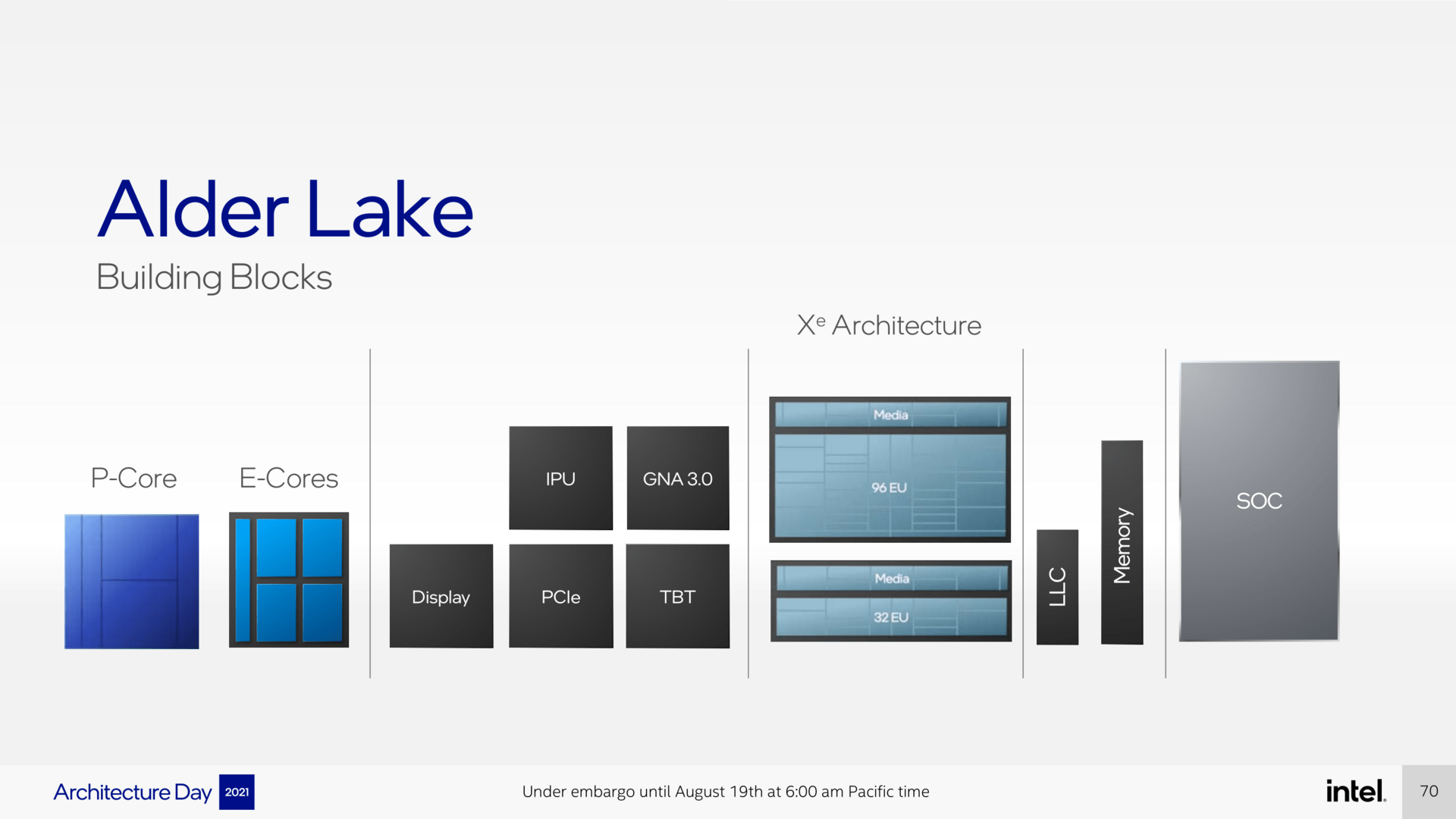

Alder Lake wird vollständig auf das neue hybride Design setzen. Kleine, hocheffiziente Prozessorkerne, wie man sie bisher eher von Atom kannte, werden je nach Marktumfeld von einer variierenden Anzahl großer Performance-Kerne, bekannt von den Core-CPUs, begleitet. Eine iGPU auf Xe-Basis ist immer mit von der Partie. Der Baukasten soll passende Prozessoren für nahezu jeden Marktbereich möglich machen. Und was steckt hinter den einzelnen Bestandteilen?

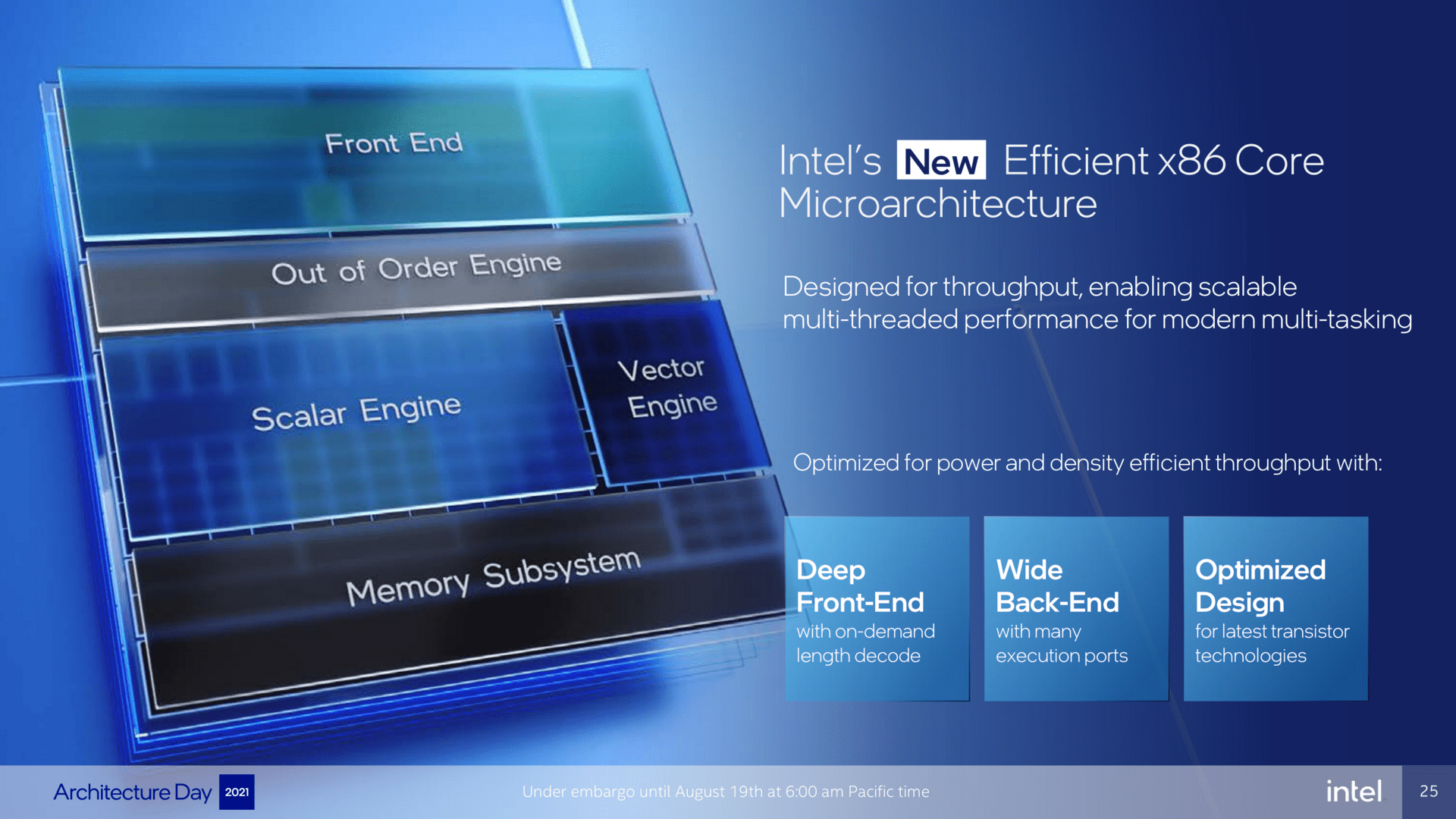

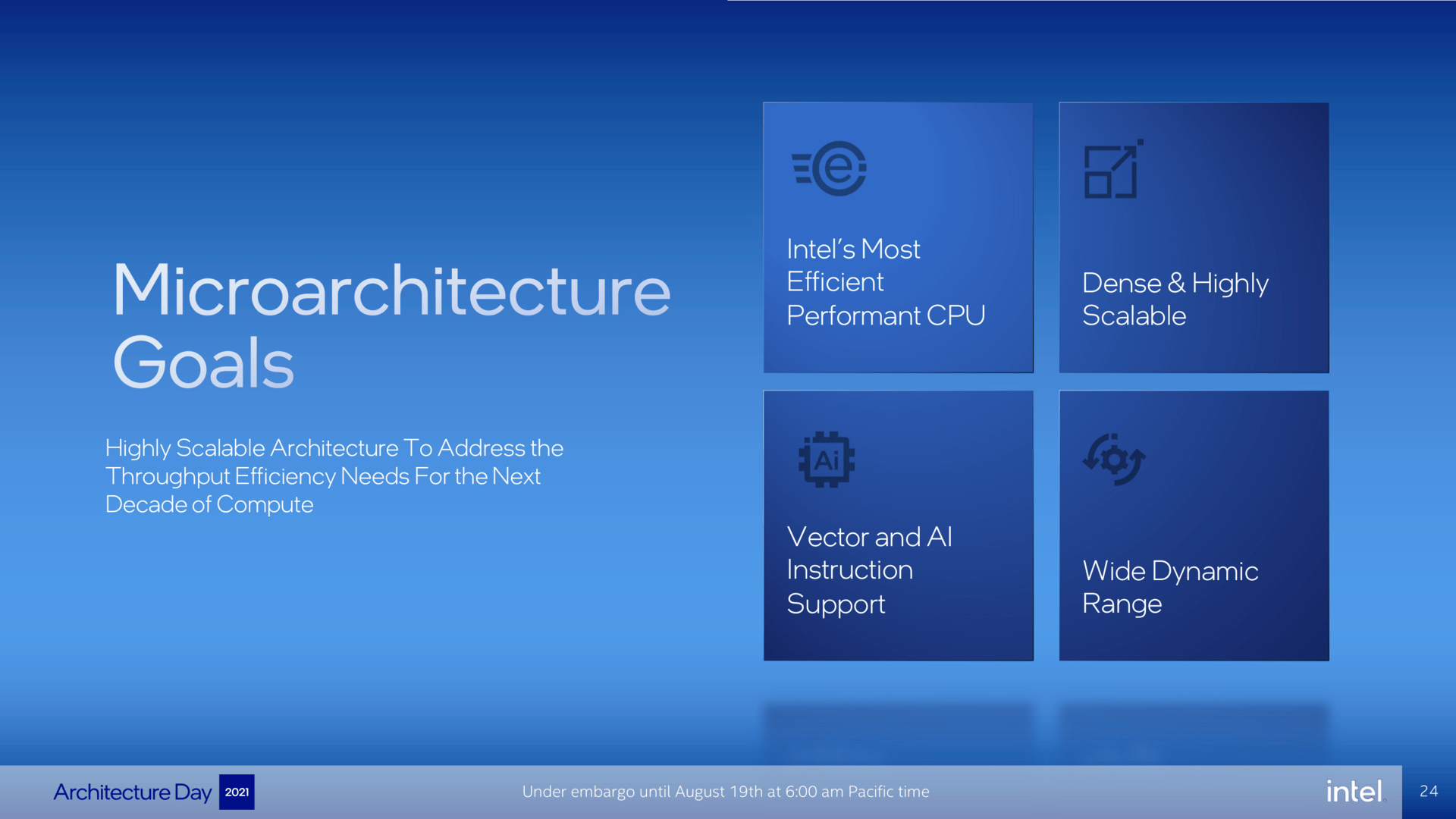

Efficient x86 Core: Grace Mont

Grace Mont (Gracemont) folgt in der Entwicklung auf Tre Mont (Tremont). Einige der Grundzüge sind dabei wiederzuerkennen, aber das haben x86-CPU-Architekturen ohnehin so an sich. Intels Ziel bei Gracemont war es, den effizientesten x86-Kern zu bauen, den es bisher in diesem Marktumfeld gab und dabei mehr IPC zu liefern als die bekannteste, wenn auch zuletzt abgelöste CPU-Architektur von Intel: Skylake. Gleichzeitig sollte der Neuling skalierbar sein, um so viele Kerne, wie eben benötigt werden, mit Taktraten von sehr gering bis sehr hoch kombinieren zu können.

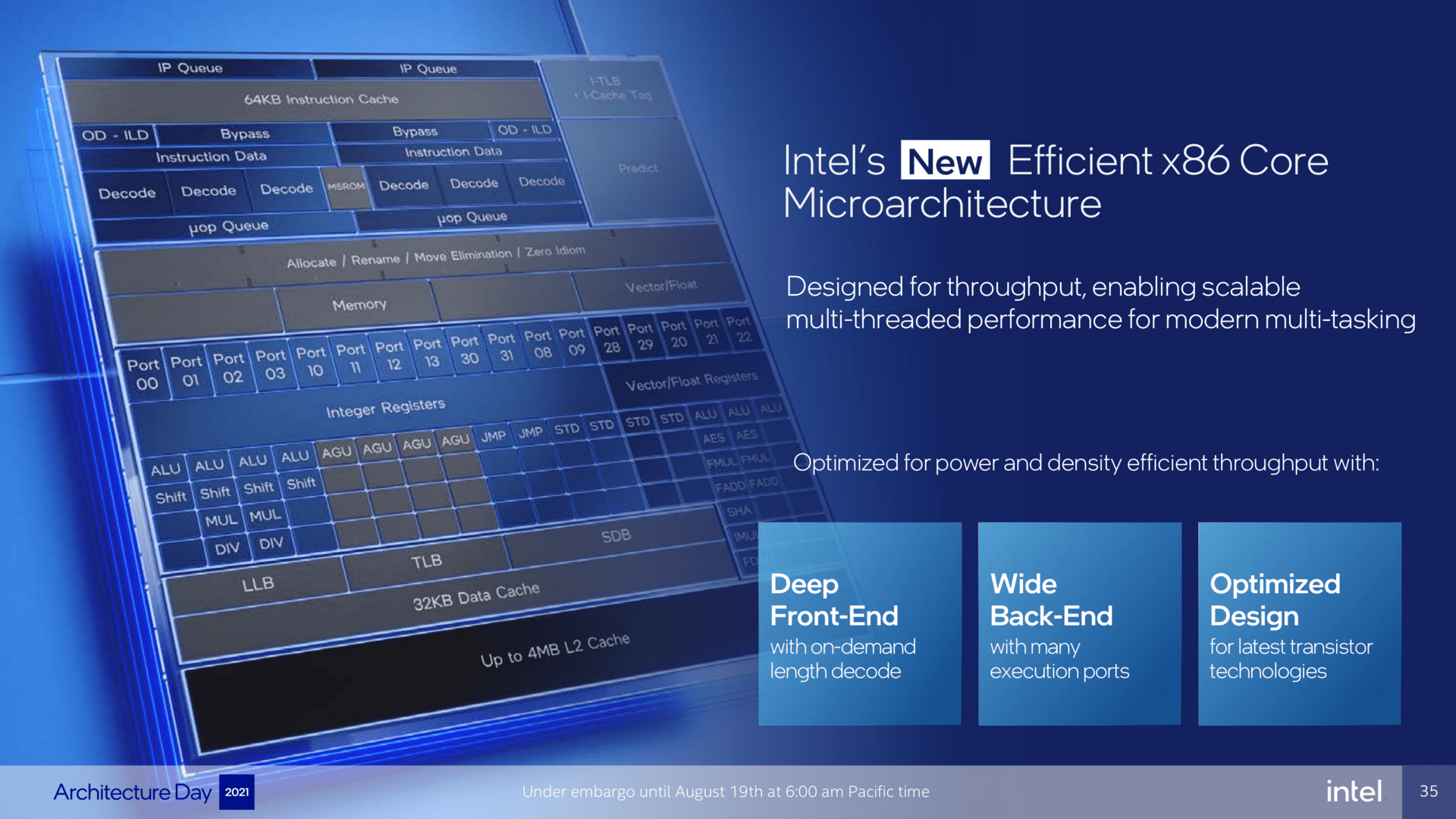

Die Überarbeitung startet wie bei jeder CPU-Architektur im Front End und dort bei der Sprungvorhersage. Je besser diese arbeitet, desto effizienter arbeitet die CPU, denn fehlerhafte Vorhersagen kosten Energie und Zeit ohne ein Ergebnis zu liefern. Über 5.000 Einträge kann der Cache fassen, eine lange History-Table sorgt dafür, dass bekannte Informationen schneller zur Verfügung stehen. Der auf 64 KByte aufgewertete L1-Instruction-Cache hält weitere Informationen in der Nähe der Kerne, ohne dabei auf stromhungrige Elemente der CPU oder des Systems wie den Arbeitsspeicher zurückgreifen zu müssen.

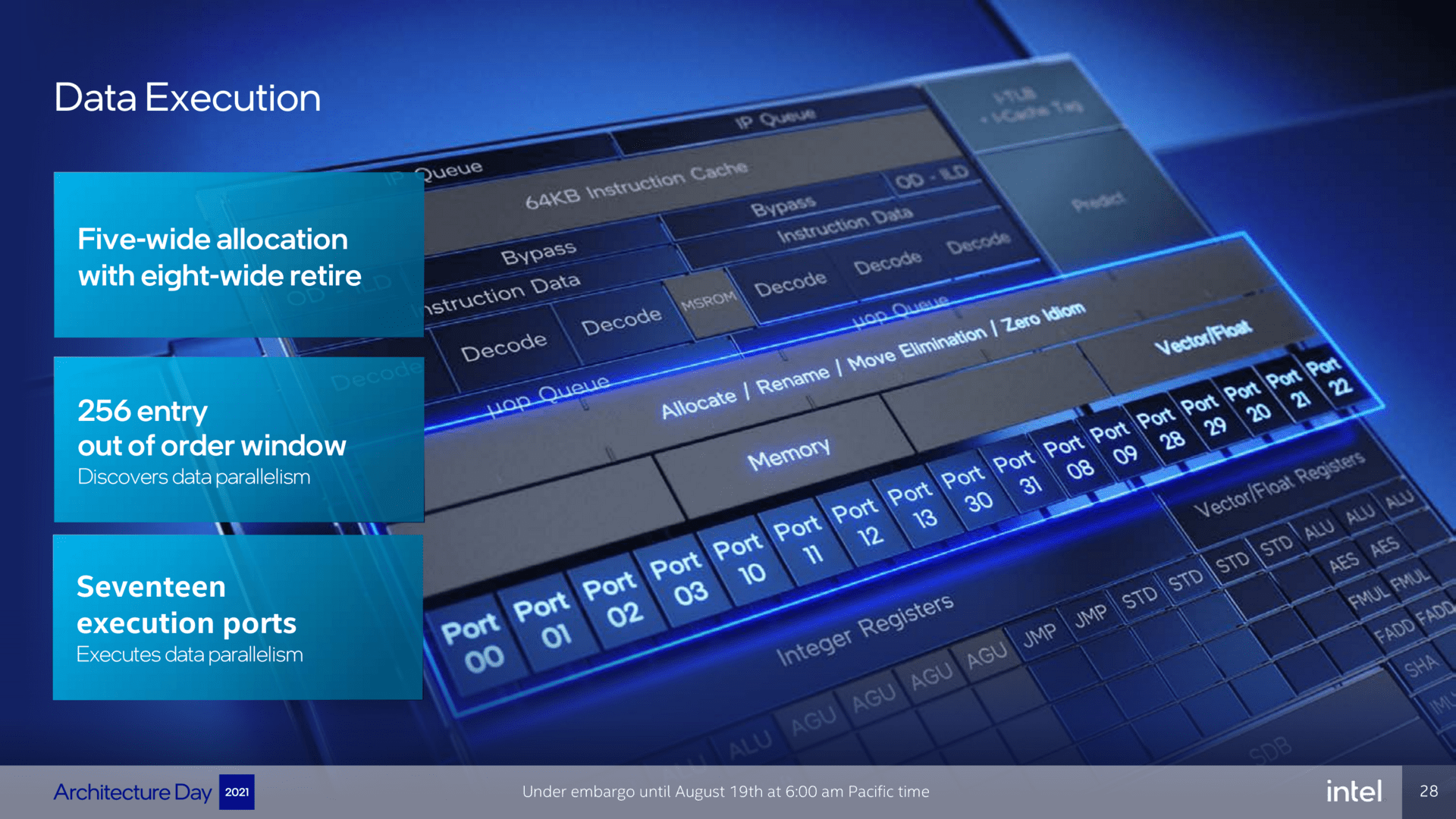

Wie bei Tremont übernimmt die Ausführung dann ein Out-of-Order-Decoder (2 × 3), der nun jedoch noch breitere Informationen bereitstellen kann als zuvor. Extrem wird es dann bei der Anzahl der Execution Ports. Waren zuvor bereits zehn an der Zahl nicht wenig, wächst deren Anzahl nun auf rekordverdächtige 17 Einheiten an. In jedem Bereich gibt es so mindestens 50 Prozent mehr Ausführungseinheiten, in einigen sogar eine Verdoppelung gegenüber dem Vorgänger. Hinzu kommen moderne ISA-Features von AES bis SHA und FMA. AVX bleibt bei den kleinen Kernen wiederum beim Standard AVX2.

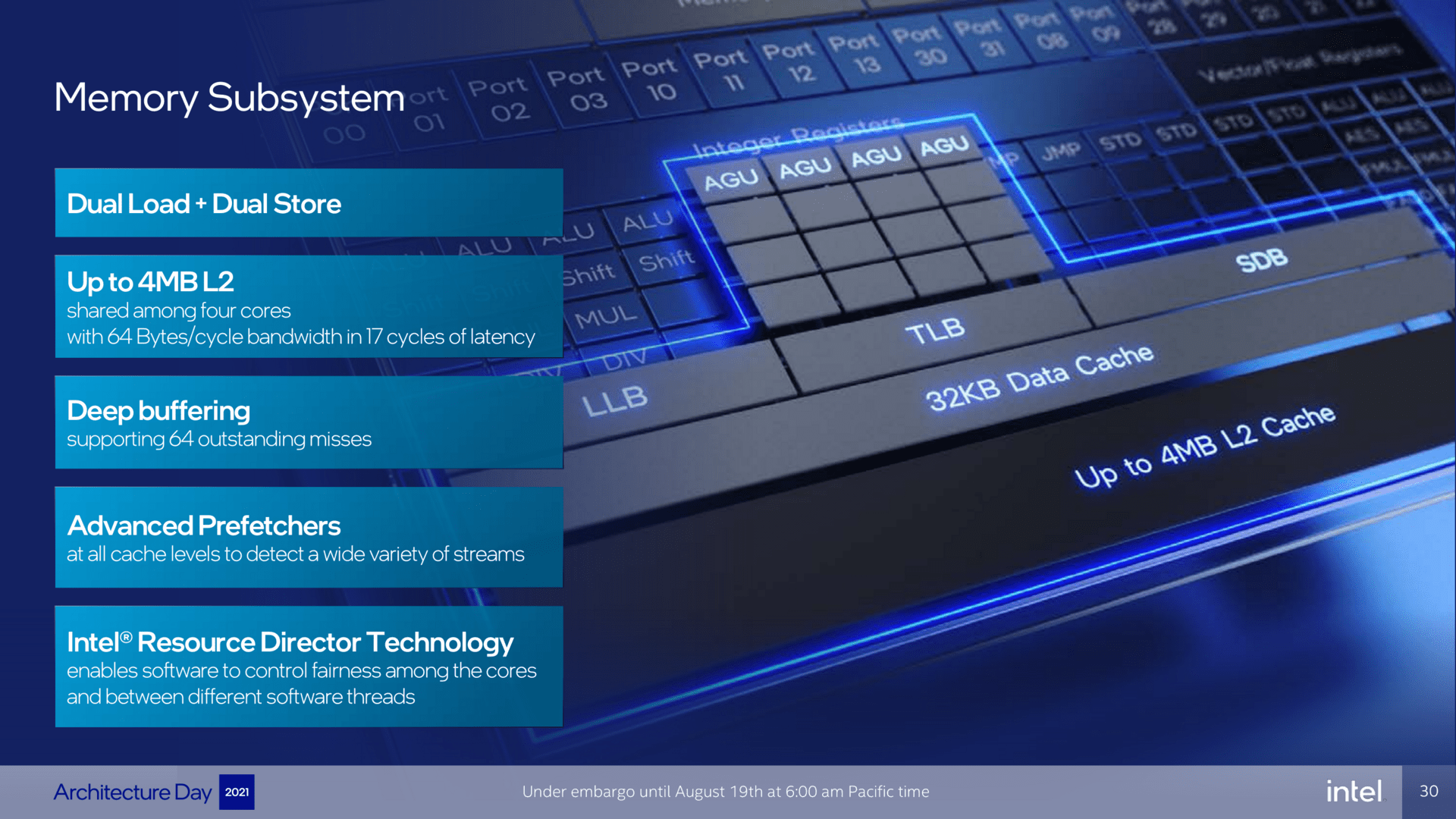

Ein schnelles Speicher-Subsystem schließt sich an. Eine doppelte Load- und doppelte Storage-Pipeline entsprechen der Ausbaustufe eines großen Prozessorkerns, 4 MByte L2-Cache unterstützen dabei jeweils vier Kerne, 32 KByte L1-Datencache stehen jedem Kern zur Verfügung.

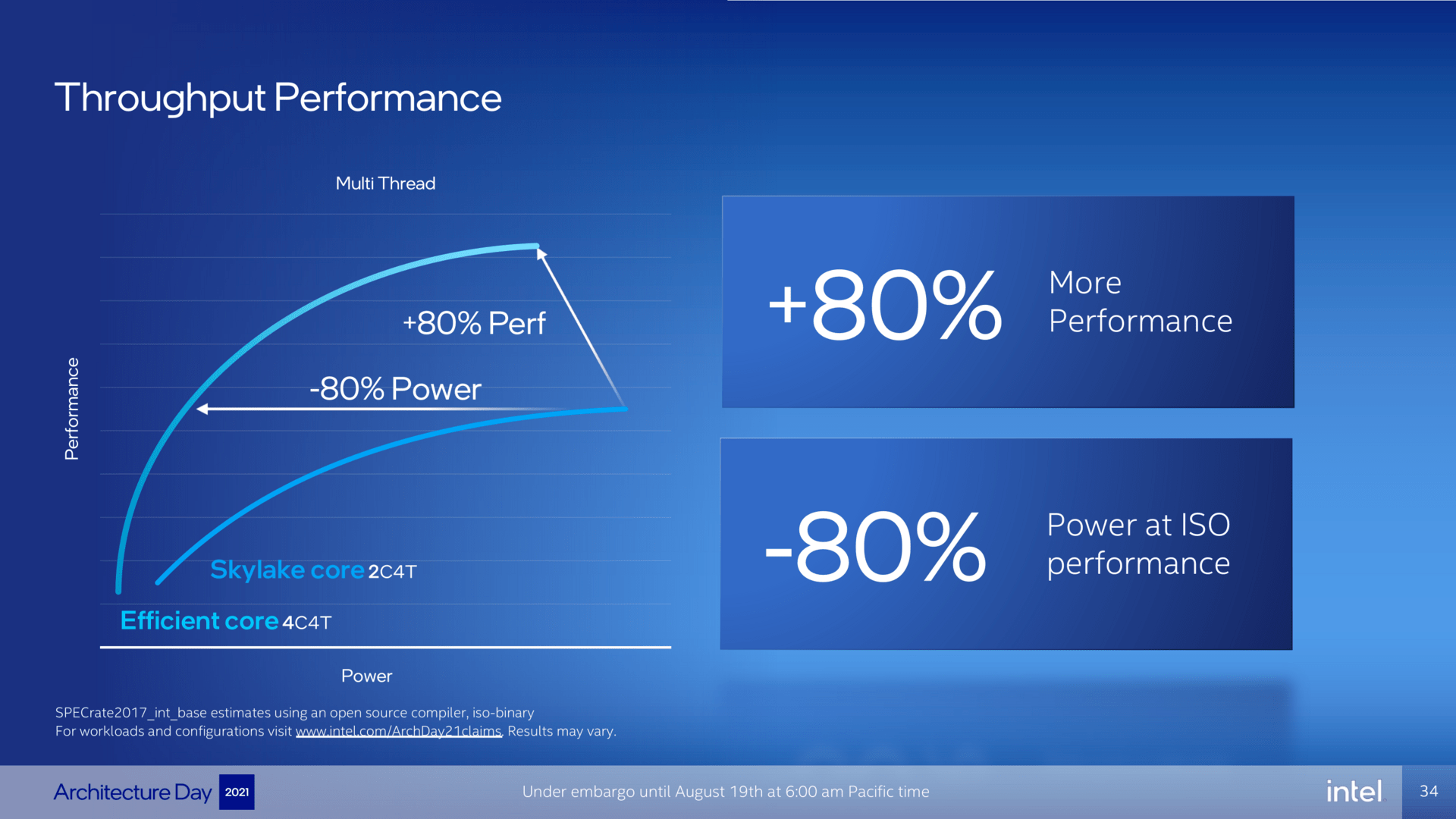

Das Gesamtpaket ist laut Intel am Ende nicht nur stromsparend, sondern auch schnell: Gegenüber Skylake sei ein Gracemont-Kern bei gleichem Energiebedarf 40 Prozent schneller. Oder anders ausgedrückt: Ein Skylake-Kern benötigt 2,5 Mal soviel Energie, um die Leistung eines neuen Gracemont-Kerns bereitzustellen.

Das Spiel lässt sich bei Mehr-Kern-Analysen noch weiter treiben. Gracemont mit vier Kernen liefert über 80 Prozent mehr Leistung als ein Skylake mit 2 Kernen und vier Threads (ein klassischer U-Prozessor für Notebooks über Jahre) bei noch geringerer Leistungsaufnahme. Auch hier öffnet erst die umgekehrte Betrachtung die Augen bezüglich der Effizienz: Skylake müsste in der Form fünf Mal mehr Energie aufnehmen, um die gleiche Leistung bereitzustellen.

Eine weitere erwähnenswerte Neuerung ist, dass vier der neuen Gracemont-Kerne ungefähr genau so groß sind wie ein Skylake-Kern. Hier spielt natürlich auch die neue Fertigungsstufe „Intel 7“ vs. 14 nm mit hinein.

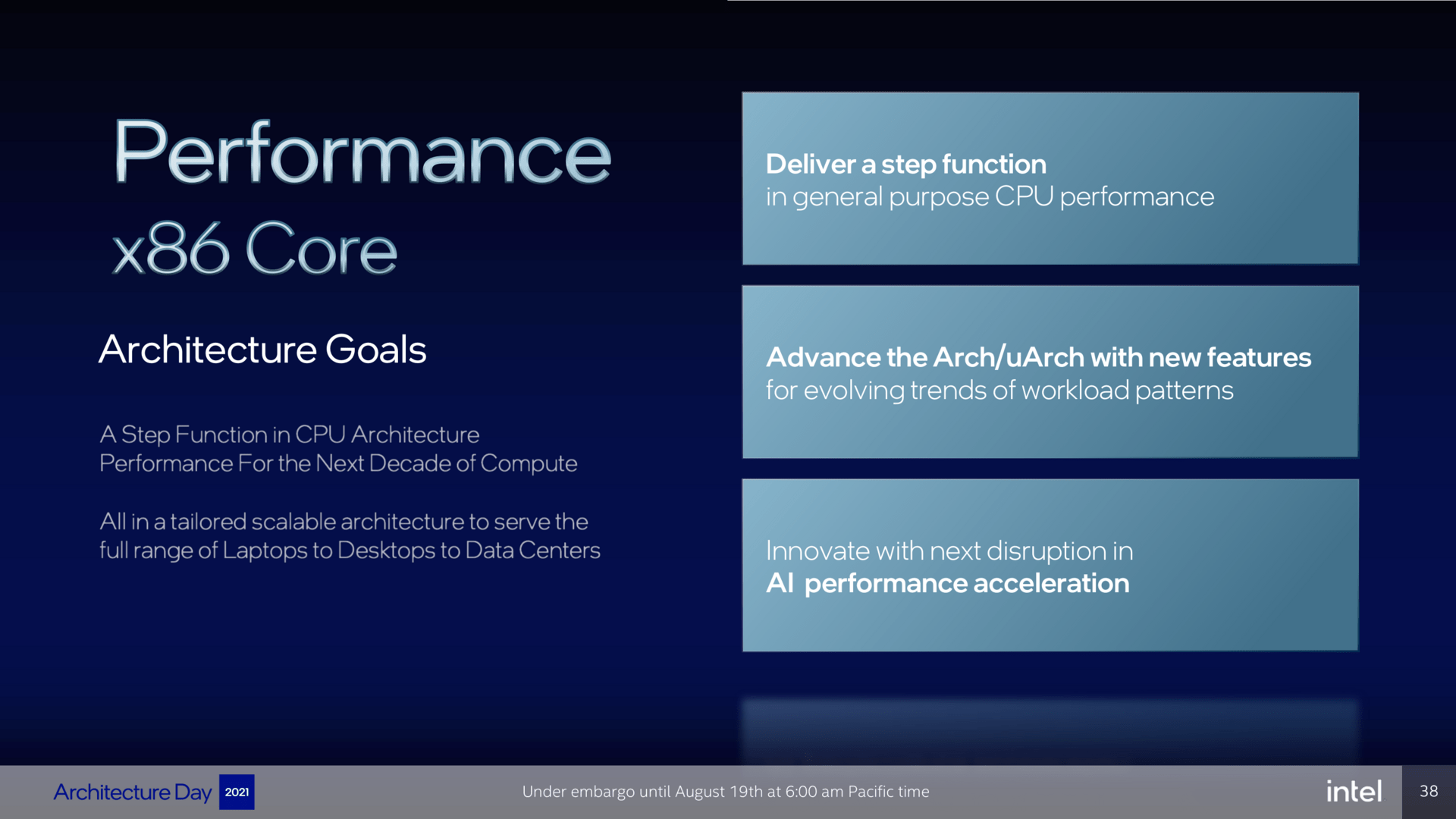

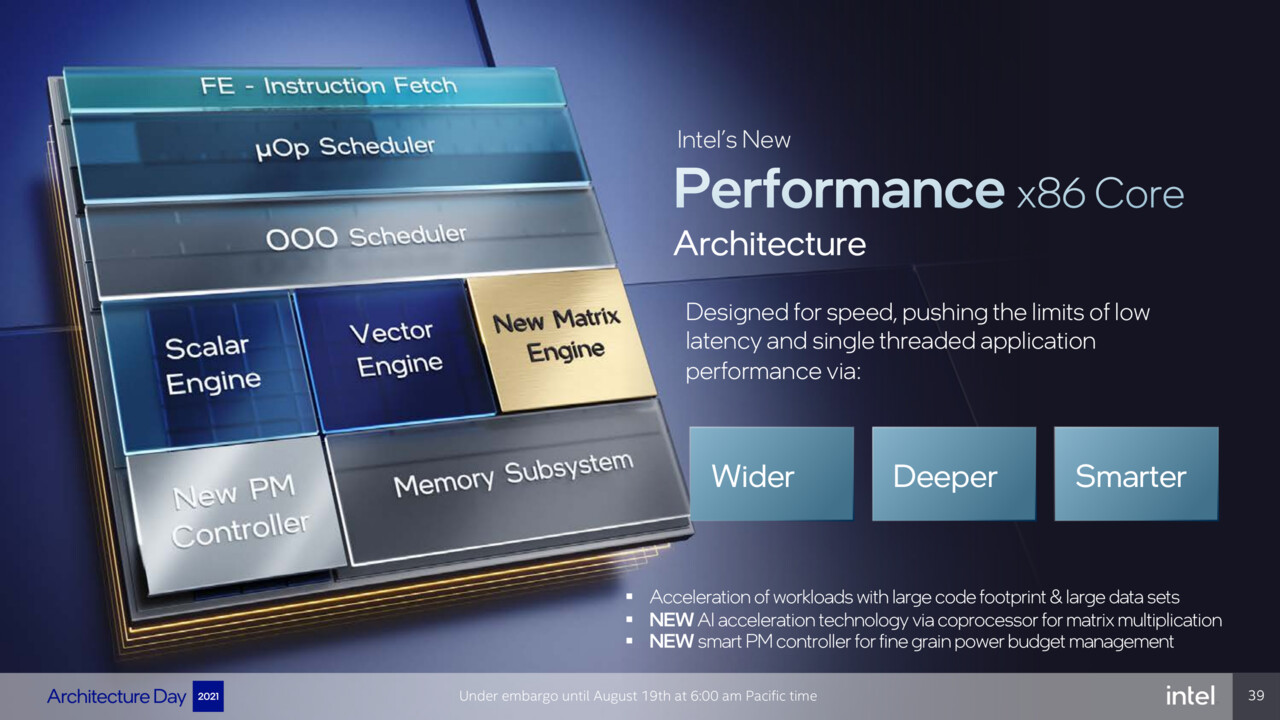

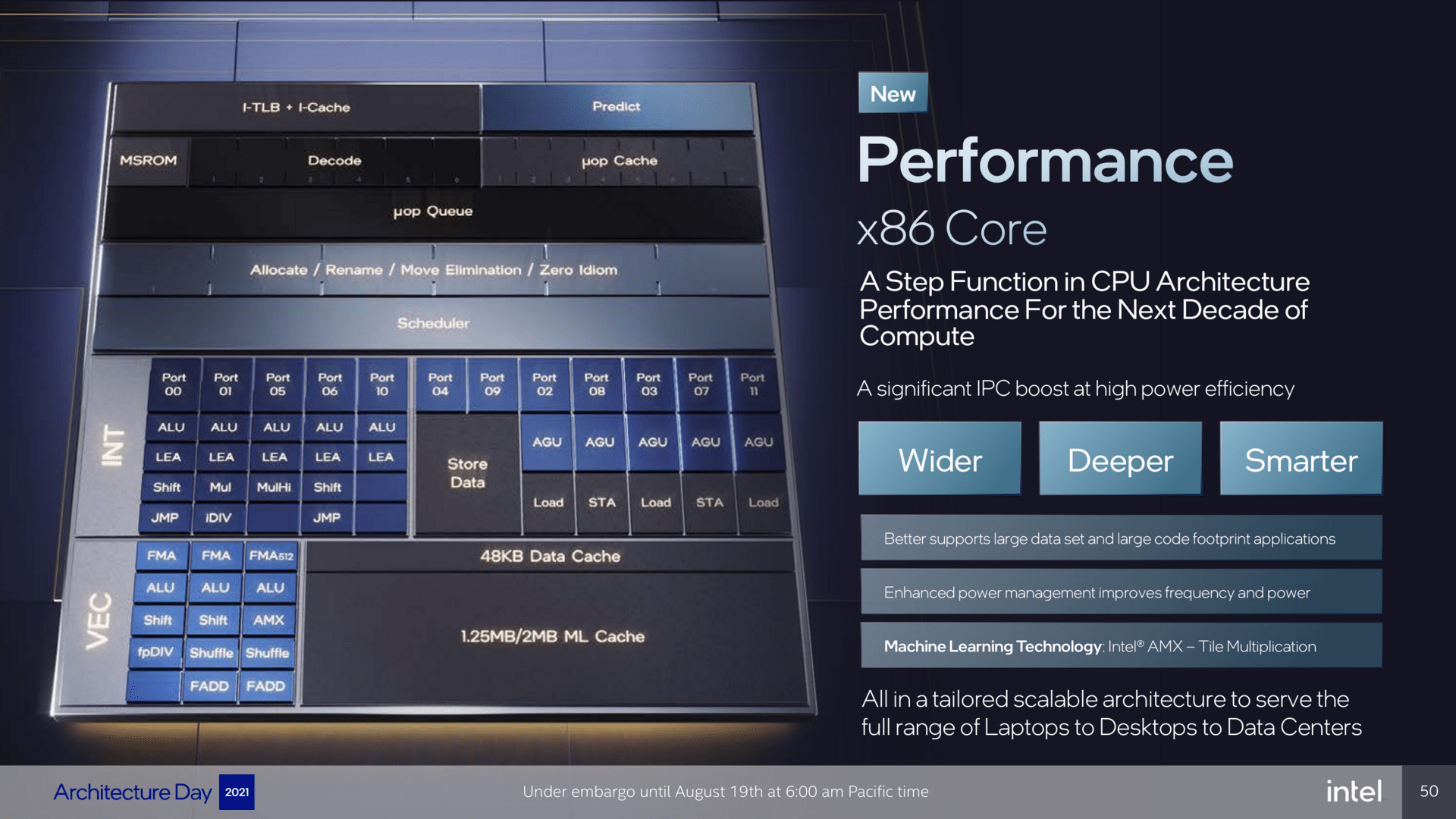

Performance x86 Core: Golden Cove

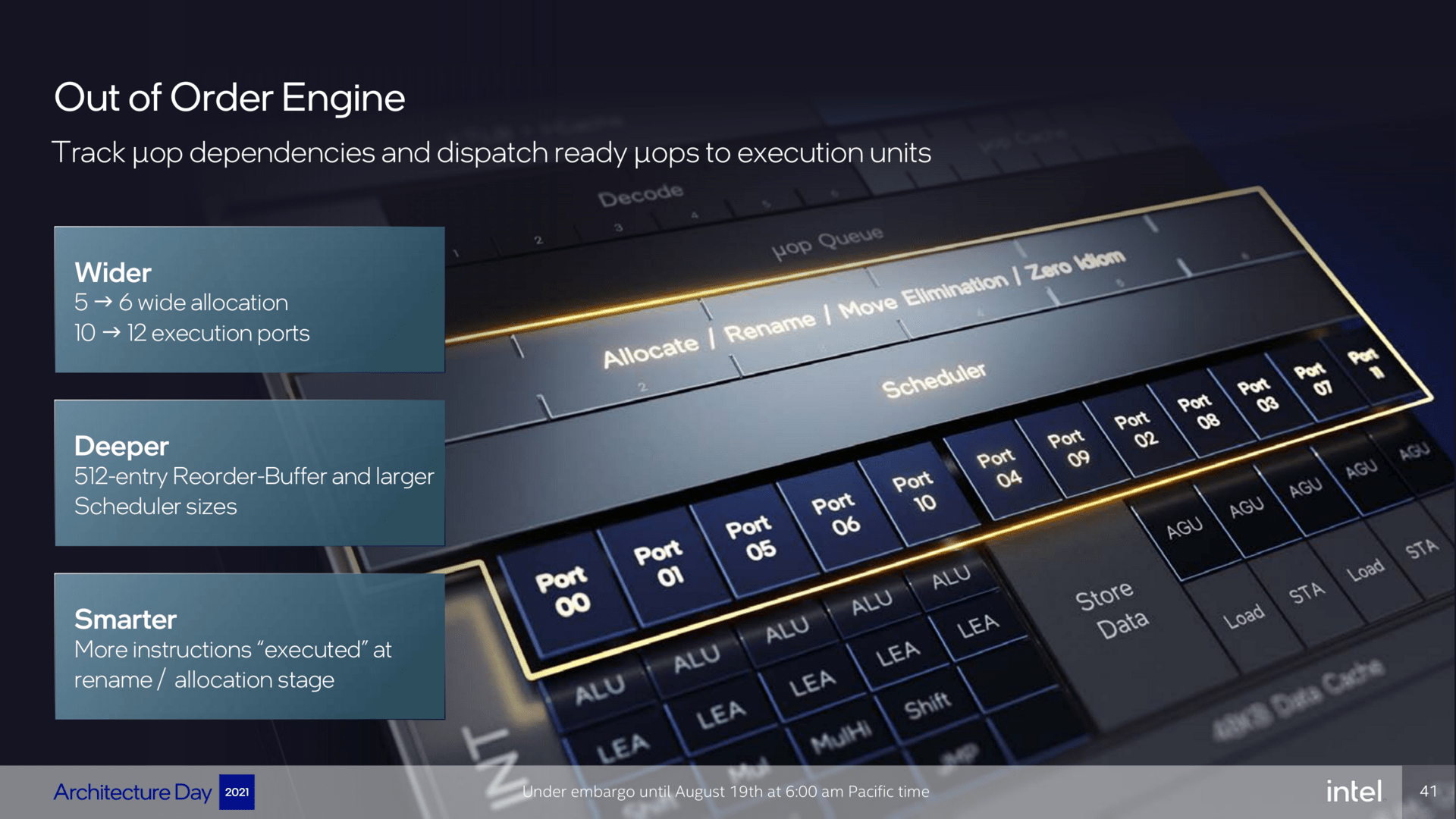

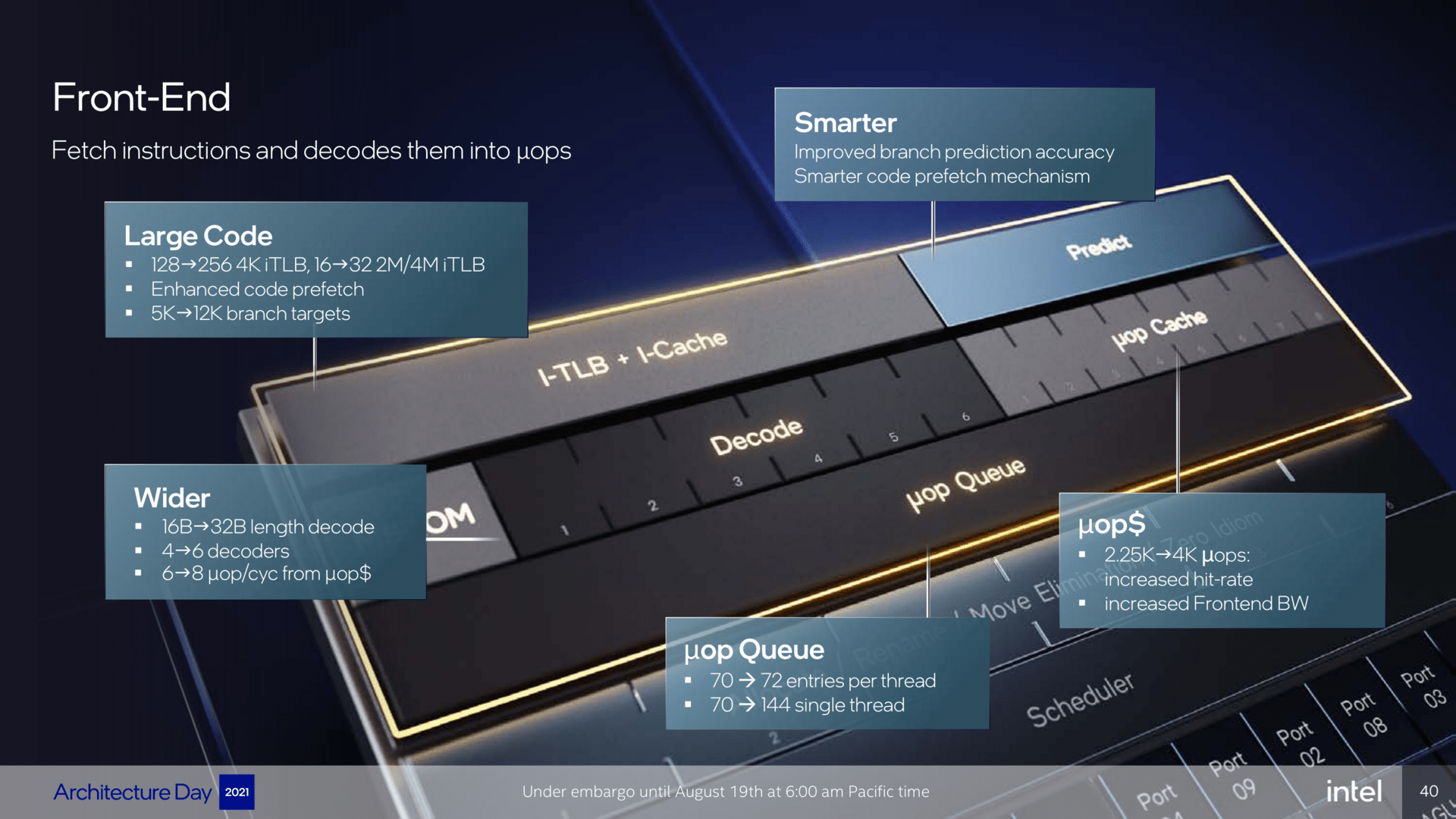

Golden Cove markieren die klassischen big cores von Intel, die vom Notebook über den Desktop bis in den Server wandern. Auch hier ist das Motto wider, deeper, smarter und es gibt bereits im Front End den Ton an.

Dort gibt es bei den großen Kernen wieder den seit Sandy Bridge bekannte Micro-op-Cache, der deutlich mehr Einträge fasst und diese schneller und in größerer Zahl gleichzeitig abarbeiten kann. Nahezu jeder andere Bereich im Front End ist ebenfalls viel breiter aufgestellt und kann mehr Einträge fassen respektive diese schneller weitergeben.

Über eine 6-wide-allocation werden fortan zwölf Execution Ports gefüttert. Hier sticht ein zusätzlicher fünfter Integer-Port heraus, der sich um normale Standardaufgaben kümmern soll, während die weiteren Integer-Einheiten auch Spezialaufgaben übernehmen können. In den Vektor-Einheiten kann die AVX-512-Implementierung fortan auch FP16-Operationen ausführen. Erstmals kümmert sich das neue AMX um Matrizen-Rechnungen und verspricht deutliche Leistungsgewinne, sofern die Software diese Features unterstützt. Intel nennt für den Idealfall einen Leistungszuwachs um den Faktor 8.

AVX-512 wird in Alder Lake aber nicht zum Zuge kommen, denn die ISA orientiert sich wie bei Lakefield am kleinsten gemeinsamen Nenner, der mit den kleinen Kernen vorgegeben ist: AVX2. Da beispielsweise VNNI aber ausgelagert wird, werden früher in AVX-512 integrierte Features nun als AVX2 + Zusatz angeboten. Dennoch macht Alder Lake hier gegenüber den Vorgängern defacto einen Rückschritt, AVX-512 darf nur die Server-CPU Sapphire Rapids voll ausleben.

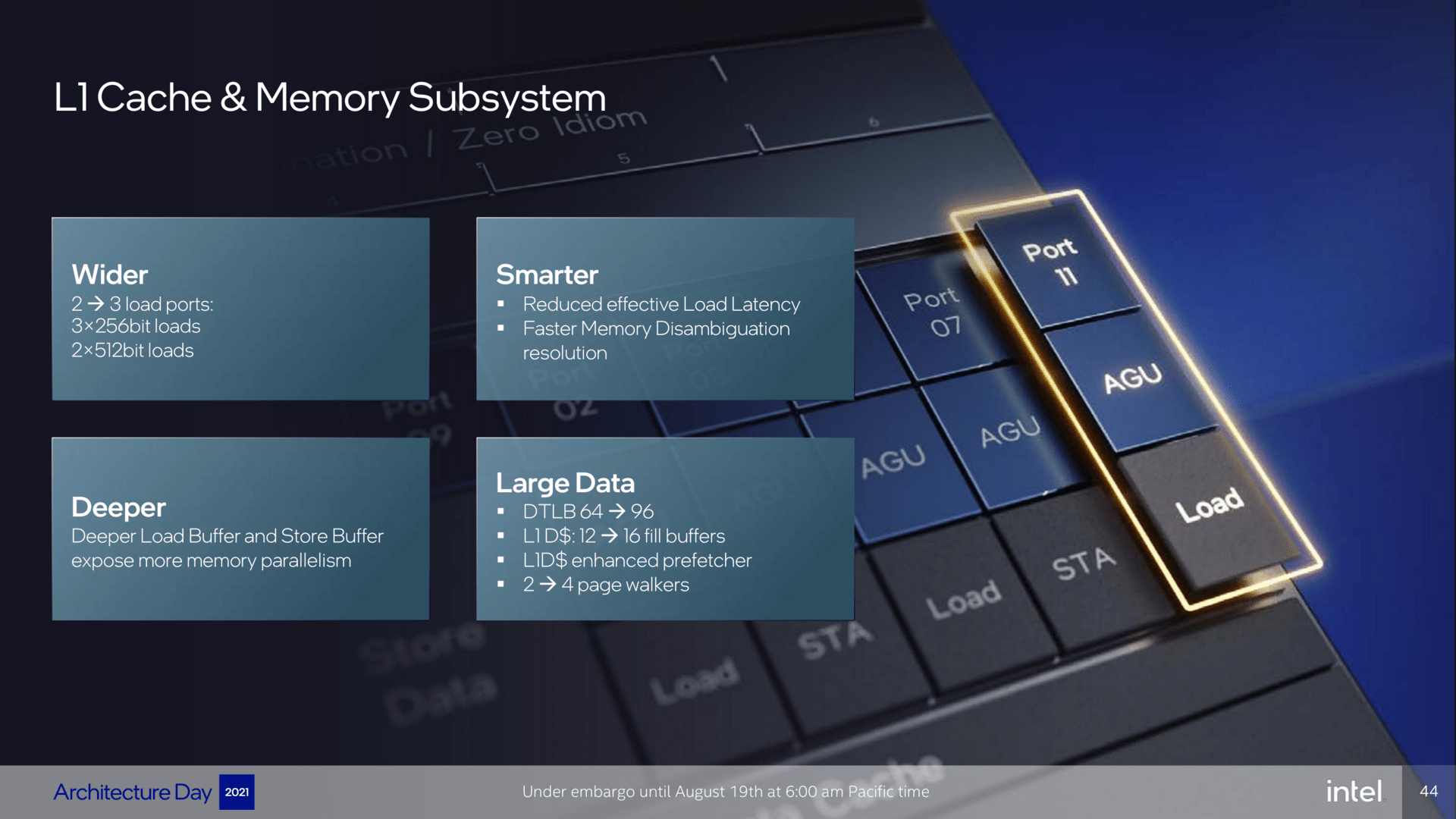

Auch bei den großen Kernen kommt L1- und L2-Cache sowie dem Speicher-Subsystem eine gewichtige Aufgabe zu. Dabei macht Intel bei Alder Lake erneut einen Unterschied, wie viel in welcher CPU für welchen Zielmarkt pro Kern steckt: Beim L2-Cache wird das Client-Segment (Alder Lake) 1,25 MByte mit sehr geringen Latenzen erhalten, während die Kerne für das Datacenter (Sapphire Rapids) 2,00 MByte privater Natur bekommen. Neue Prefetcher, ein verbesserter Umgang mit Fehlschlägen, aber auch hier erweiterte Ports und Datensätze sollen mehr Leistung bereitstellen.

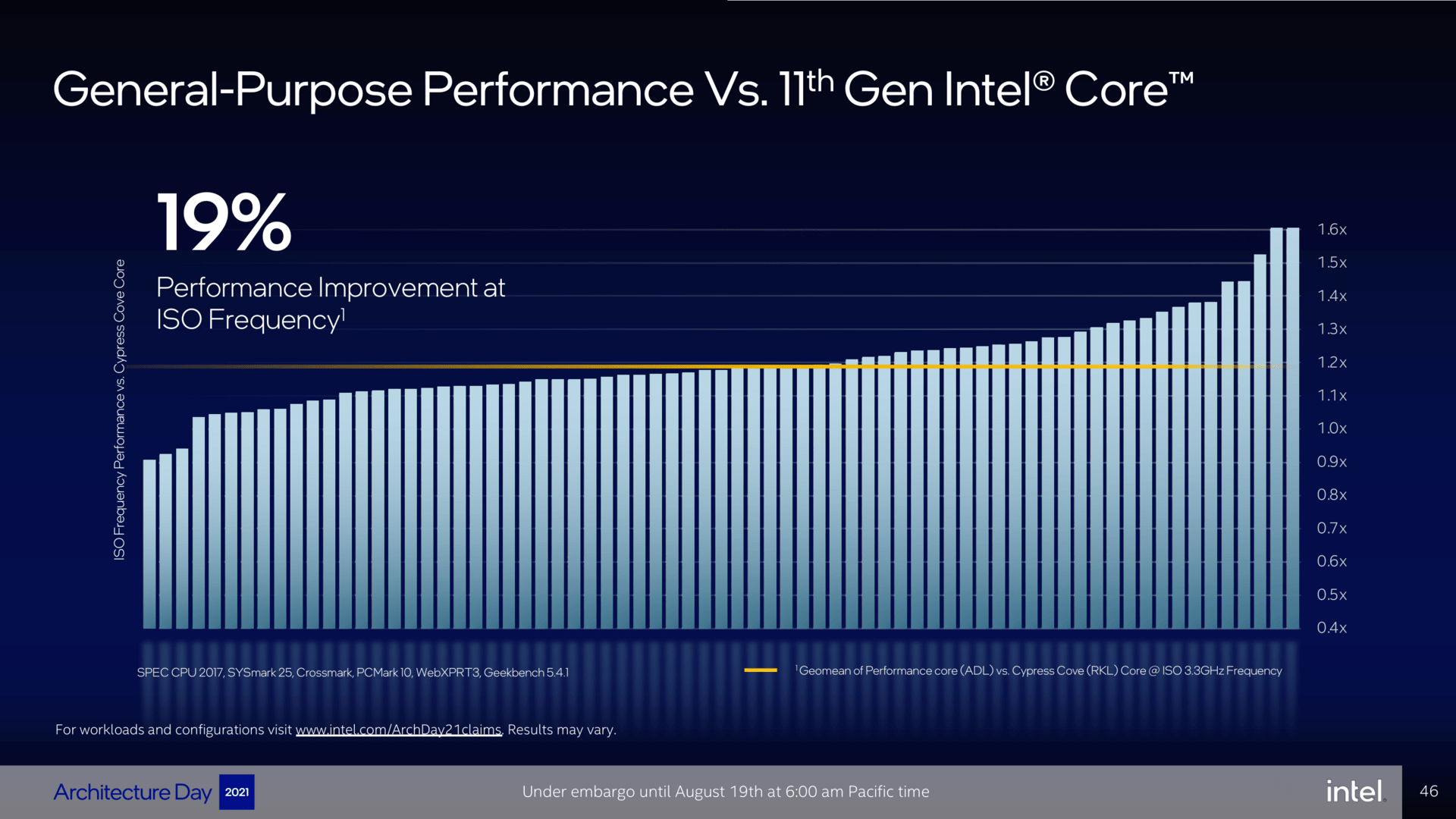

Unterm Strich werden die neuen Kerne laut Intel in einem breiten Testparcours im Durchschnitt erneut 19 Prozent mehr IPC bei einem Takt von 3,3 GHz bereitstellen als die Kerne in der elften Generation Core. Intel bezieht sich hierbei auf Cypress Cove, also jene in Rocket Lake, die dem Stand von Ice Lake entsprechen. Tiger Lake wurde nicht berücksichtigt. Auch die IPC von Tiger Lake stieg im Vergleich zu Ice Lake in gewissen Anwendungen zwar an, vor allem wenn das neue Cache-System zum Zuge kam, war unterm Strich bei gleichem Takt aber ähnlich schnell. Tiger Lake kam letztlich primär über den Takt zum Erfolg.

Nichtsdestoweniger ist die von Intel genannte IPC-Steigerung in Höhe von 19 Prozent erst einmal nur für das Desktop-Umfeld gesetzt, in dem Tiger Lake quasi nicht existiert. Wie die Unterschiede im Notebook sind, werden Tests offenbaren. Traditionell sind Herstellerangaben korrekt, sowohl von Intel aber auch AMD natürlich sehr positiv ausgelegt und liegen im realen Alltag leicht darunter.

Um auch die „Big Cores“ so effizient wie möglich zu gestalten, hat Intel den großen Kernen auch einen neuen Powermanagement-Microcontroller spendiert. Diese reagiert fortan in Microsekunden statt bisher Millisekunden und soll so noch schneller Spannungen und daraus resultierend Taktraten anpassen. Weitere Details dazu gab Intel noch nicht preis, auch wie beispielsweise die komplette Stromversorgung um vermutlich eine neue Generation FIVR genutzt wird ist noch offen.

Intel betont, dass Golden Cove letztlich die größte Neuerung seit über einer Dekade bei den CPU-Kernen im Konzern sei. Ihre komplette Stärke werden sie aber erst im Datacenter ausspielen, wo sie in CPUs vom Typ Sapphire Rapids nicht mit kleinen Kernen kombiniert werden. Details hat ComputerBase in einer separaten Meldung zusammengetragen.

Intel Thread Director als Hardware-Scheduler

Die Herausforderung im Desktop und Notebook ist, die kleinen und großen Kerne in Alder Lake zusammenarbeiten zu lassen. Und das bedeutet, dass das Scheduling, also die Arbeitsverteilung der Lasten, auf Alder Lake angepasst werden musste. Der traditionelle Weg, nur die großen oder nur die kleinen Kerne arbeiten zu lassen, würde stets Rohleistung oder Effizienz auf der Strecke lassen und allein dem Betriebssystem die Verantwortung zu übergeben, erschien Intel ebenfalls als nicht optimal – kein Wunder, haben die 1. und 2. Generation Threadripper oder auch Lakefield doch zuletzt gezeigt, wie gravierend die Probleme ausfallen können, wenn die Software die Hardware nicht im Detail kennt respektive beherrscht.

Die Lösung: Intel Thread Director Technology, eine der größten Neuheiten in der Sparte, die Intel laut eigenen Aussagen je hervorgebracht hat. Dahinter steckt eine hardwarebasierte Lösung, die Windows bei der Thread-Zuweisung als alleinige und oft bekannte Problemstelle aus der Gleichung nehmen soll. Thread Director übernimmt als Zwischenschritt bereits eine grobe Zuweisung der Aufgaben an die Kerne, die Windows dann umsetzt. Die beinhaltet unzählige Szenarien, beispielsweise den Wechsel von großen zu kleinen Kernen, wenn große für wichtigeres benötigt werden – und zurück.

Intel demonstrierte das an einem Alder-Lake-System mit acht großen und acht kleinen Kernen, also der erwarteten Standard-Desktop-Lösung. Windows 11 ist laut Intel das erste System, welches darauf ausgelegt ist, andere werden folgen. Das System sieht wie folgt aus.

Primäre Tasks werden zu Beginn den Performance-Kernen zugewiesen, Hintergrund-Anwendungen laufen auf den E-Kernen. Kommt nun eine weitere Anwendung hinzu, die beispielsweise AI-Features benötigt, die nur große Kerne nativ unterstützen, gibt der Thread Director von Intel dem Windows-Scheduler den Hinweis, dafür doch einen P-Kern freizumachen. Windows verlagert also die Lasten von den P-Kernen folglich auf die E-Kerne, sodass die neue AI-Anwendungen mit vollem Support durch die P-Kerne dort möglichst schnell abgearbeitet werden.

Das wird zu Beginn alles nur mit Windows 11 problemlos funktionieren, weshalb der Zeitraum für den Produktstart sehr ähnlich gelagert ist. Ende Oktober wird Windows 11 erwartet, Alder Lake soll darauf passend abgestimmt sein und vermutlich Anfang November folgen – bei Intel heißt es offiziell „Herbst 2021“.

Die Prozessorfamilie Alder Lake

Alder Lake wird auf „Intel 7“ basieren. Dahinter steckt die vor wenigen Wochen umbenannte Fertigung 10 nm Enhanced SuperFin, welcher laut Intel mehr als ebenbürtig zu TSMCs Fertigungsprozess N7 sein soll, mit dem beispielsweise AMDs Prozessoren gefertigt werden. Tiger Lake wird aktuell noch in 10 nm SuperFin gefertigt.

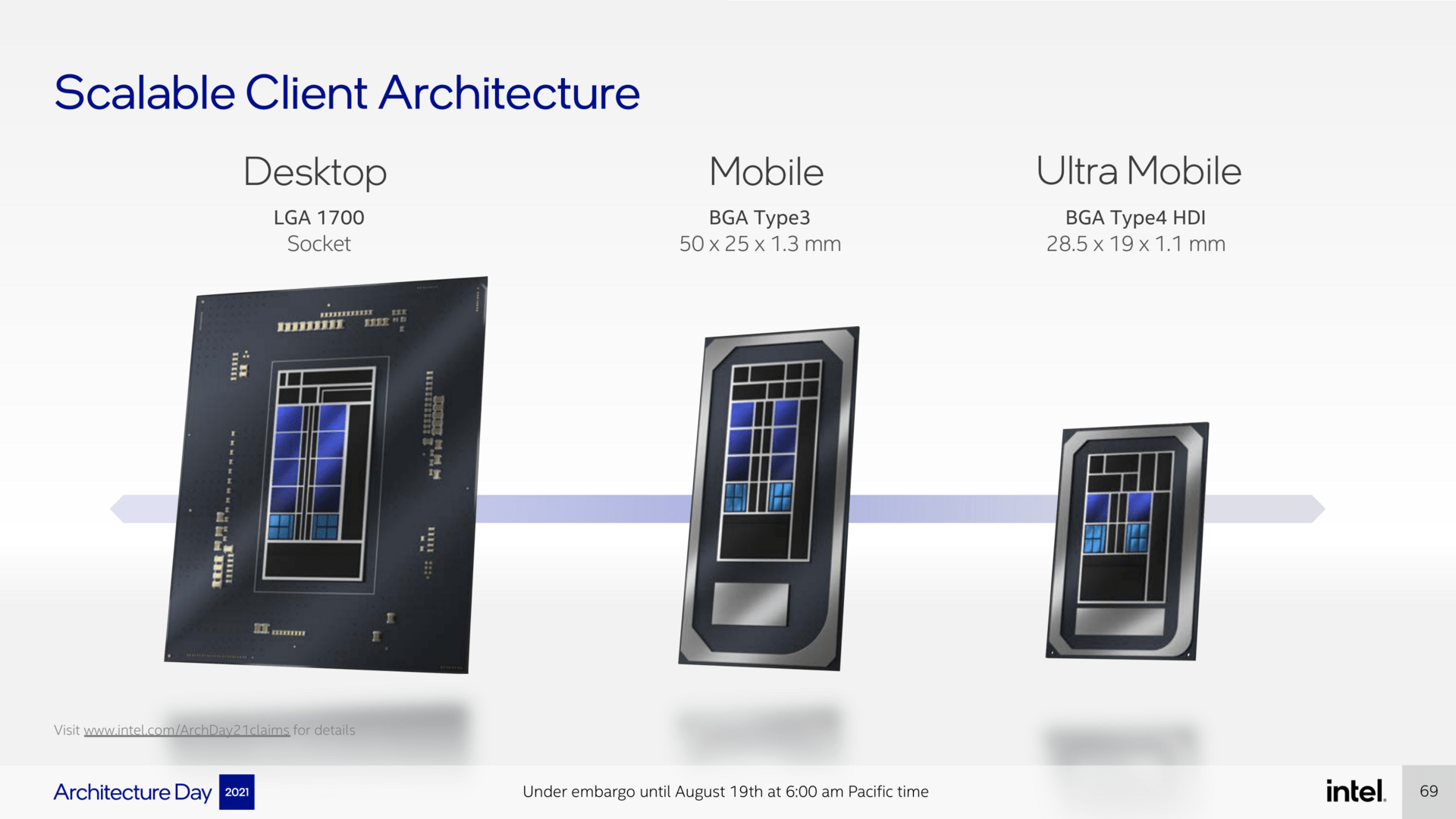

Für die unterschiedlichen Märkte legt Intel dabei erneut mehrere Lösungen auf, was sich insbesondere im Package zeigt: Die Desktop-Lösungen setzen auf das neue LGA-1700-Format, für das Notebook gibt es den Nachfolger der U-Serie als BGA-Chip sowie noch kleinere Varianten, die früher als Y-Modelle verkauft wurden. Entsprechend erstreckt sich das Portfolio der Chips von bis zu 125 Watt in der Oberklasse hinab bis auf 9 Watt.

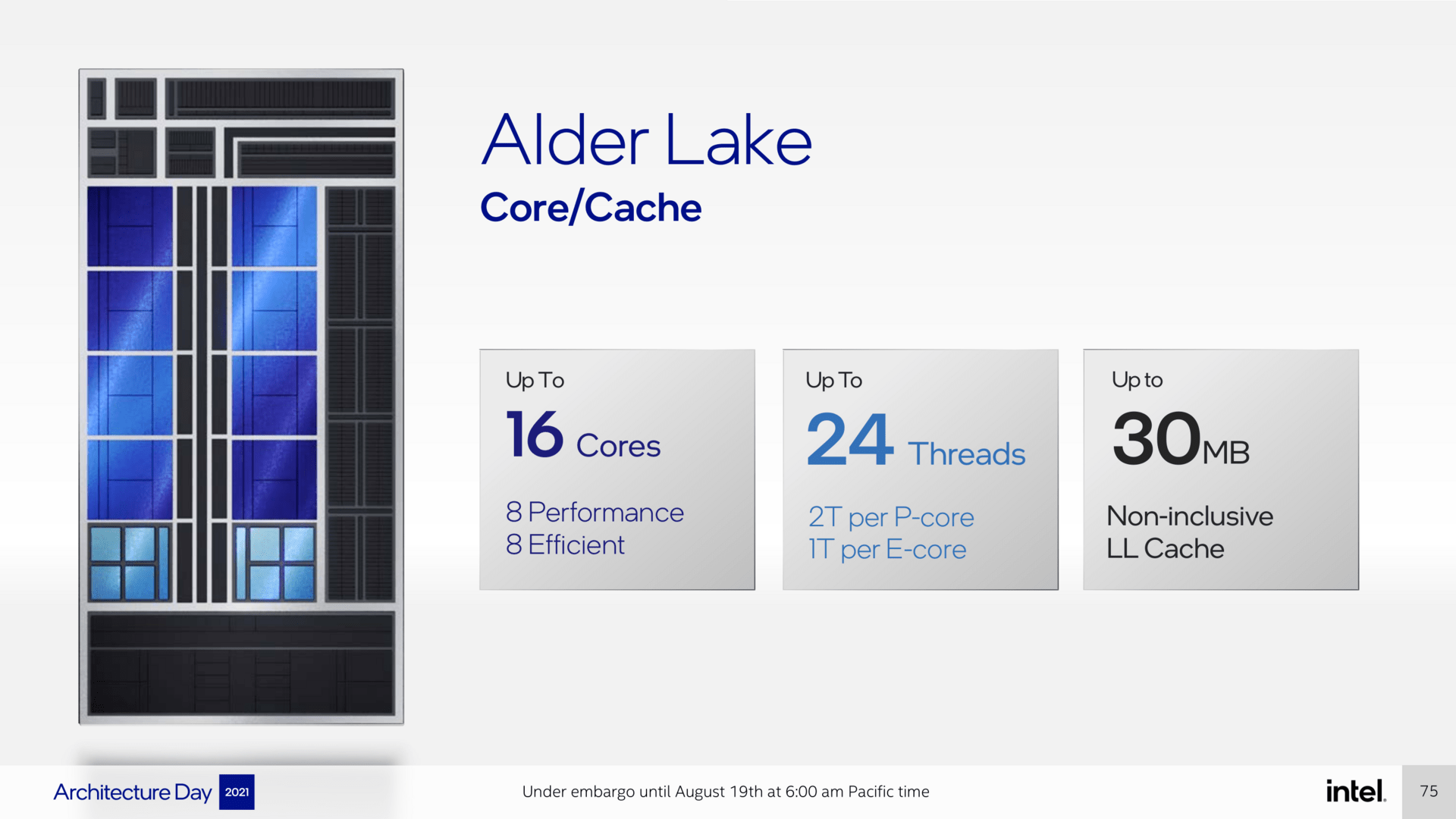

Vorerst sind drei grundlegende Chips gesetzt, wobei Intel betont, dass in Zukunft weitere folgen werden. Denn das Baukastenprinzip ermöglicht das Zusammenfügen diverser Teile, was vor allem für die großen Kerne aber auch die unterschiedlich konfigurierte Grafik gilt. Fest steht aktuell bei Alder Lake, dass die kleinen E-Kerne immer im Vollausbau mit ihren beiden Quad-Core-Clustern zum Einsatz kommen werden, den Unterschied machen die P-Kerne, die iGPU und Taktraten.

Den beiden Quad-Core-Clustern werden je nach Markt die P-Kerne zur Seite gestellt. Der Desktop wird bis zu acht P-Cores erhalten, größere Notebooks bis zu sechs, ganz kleine hingegen nur zwei. Diverse weitere Abstufungen werden folgen, das hatten bereits Listen mit unterschiedlichsten Konfigurationen offenbart.

Das Volumen des L3-Caches richtet sich primär nach den P-Cores. Im Maximum ist dieser 30 MByte groß, skaliert entsprechend dann in den weiteren Varianten nach unten. Der L3-Cache war zuletzt auch bei Intel bereits deutlich angewachsen, Tiger Lake-H45 bot 24 MByte im Maximum. Das hat neben der CPU noch einen weiteren Grund: Auch die angeschlossene Xe-Grafikeinheit darf den L3 nutzen.

Die Xe-iGPU wurde vornehmlich auf Intel 7 angepasst

Die Grafikeinheit hat Intel nur ein wenig optimiert, im Kern ging es um die Anpassung auf die neue Fertigung. Welche Auswirkungen das genau hat, erklärte Intel auch auf Nachfrage noch nicht. Nach wie vor wird der kleinste Xe-Block 32 EUs beinhalten und so etwa im Desktop eingesetzt – hier kommt in der Regel ja eine diskrete Grafikkarte zum Einsatz. Im Notebook hingegen gibt es wieder bis zu 96 EUs. Und für das Jahr 2022 ist dort dann auch mit dedizierten Intel-GPUs auf Basis der Alchemist-Architektur mit Xe-Cores zu rechnen.

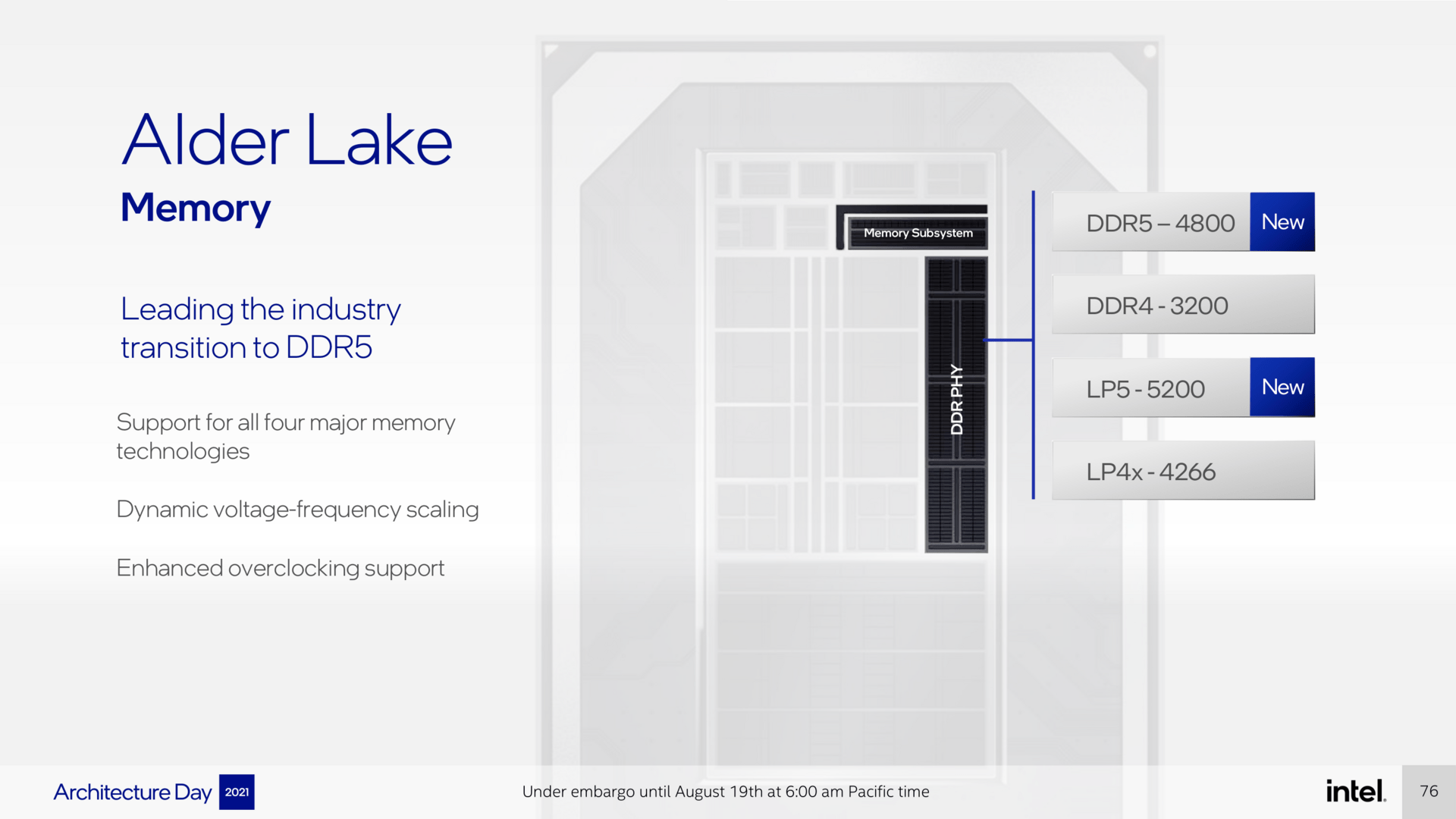

DDR5 und PCI Express 5.0 erstmals mit dabei

Alder Lake wird vier Speichertypen ansprechen können: DDR4 und DDR5, aber auch LPDDR4 und LPDDR5, welche im mobilen Markt immer öfter zum Einsatz kommen. DDR5 sticht als große Neuerung hervor, offiziell liegt der Support maximal bei DDR5-4800, doch Intel erwähnt bereits umfangreiche Übertaktungsmöglichkeiten für den Speicher. Intel XMP 3.0 wird von Herstellern der DDR5-Speichermodule bereits angekündigt, Intel selbst sagt dazu noch nichts.

Ebenfalls den Standard in der fünften Generation gibt es beim PCI-Express-Interface. 16 Lanes nach neuestem PCIe 5.0 werden hier von der CPU aus in erster Linie für Grafikkarten geboten, hinzu kommen weitere vier PCIe-Gen4-Lanes, die vermutlich für eine SSD gedacht sind, die nativ von der CPU gespeist wird – das haben aktuelle Lösungen bereits im Angebot. Die kleineren CPUs werden in diesem Punkt Abstufungen nach unten erfahren um Strom zu sparen.

Das Komplettpaket wird vor allem im mobilen Markt auch weiterhin Thunderbolt 4 und Wi-Fi 6E unterstützen. Über die exakten Ausstattungsdetails der einzelnen CPUs wird Intel zum Marktstart näher eingehen.

Alder Lake als 12. Generation Core?

Was Intel noch nicht genannt hat, sind handfeste Produkte auf Basis von Alder Lake. Und nicht nur die CPUs mit ihren Eckdaten stehen noch aus, auch dass die Serie als 12. Generation Core (Core 12000) an den Start gehen wird, hat Intel noch nicht bestätigt.

Ersteindruck und Einschätzung

Alder Lake wird ein extrem interessantes Produkt, Intel hat mit den Vorschusslorbeeren über die größten Änderungen und Anpassungen seit einer Dekade nicht übertrieben. Allein wie sich das in der Theorie imposante Konzept in der Praxis schlagen wird, steht noch in den Sternen.

Aus der von Intel präsentierten Theorie stechen zweifelsohne die kleinen Efficient Cores (E-Cores) hervor, die fortan mehr Leistung pro Kern bieten als Skylake-Kerne, die vier Jahre der Stand der Dinge waren. Aber auch die großen Kerne (P-Cores), die erneut 19 Prozent mehr IPC versprechen, als es die aktuelle Generation im Desktop bietet, lassen nach Jahren des Stillstandes mit einem großen IPC-Sprung bei Tiger Lake erneut aufhorchen. Sie werden auch im Serverprozessor Sapphire Rapids genutzt.

Vor allem für das Notebook dürfte Alder Lake eine extrem performante und bei Bedarf auch stromsparende Lösung sein, ein Fragezeichen bleibt heute jedoch im Desktopumfeld und dort vor allem hinter dem Gaming. Denn der eigentliche Star von Alder Lake ist trotz erster Erklärungen noch immer ein Mysterium, das sich erst im Alltag beweisen muss: der Hardware-Scheduler Intel Thread Director. Diese neue Ebene auf Hardware-Seite zwischen den vielen verschiedenen Kernen und dem Windows-Scheduler soll dafür sorgen, dass dem Betriebssystem die perfekte Priorisierung von Aufgaben schon auf dem Silbertablett präsentiert wird und er dann nur noch die Zuweisung für den richtigen Kern übernehmen muss. Es dürfte das Feature sein, das letztlich über den Erfolg oder Misserfolg von Alder Lake entscheiden wird.

ComputerBase hat die Informationen im Rahmen des Architecture Day 2021 von Intel vorab auf einem Event in Berlin unter NDA erhalten. Eine Einflussnahme des Herstellers auf die Berichterstattung fand nicht statt, eine Verpflichtung zur Veröffentlichung bestand nicht. Einzige Vorgabe war der frühestmögliche Veröffentlichungstermin.

Dieser Artikel war interessant, hilfreich oder beides? Die Redaktion freut sich über jede Unterstützung durch ComputerBase Pro und deaktivierte Werbeblocker. Mehr zum Thema Anzeigen auf ComputerBase.