Intel Granite Rapids-SP: 80-Kern-Samples mit 336 MB L3 im A2-Stepping gesichtet

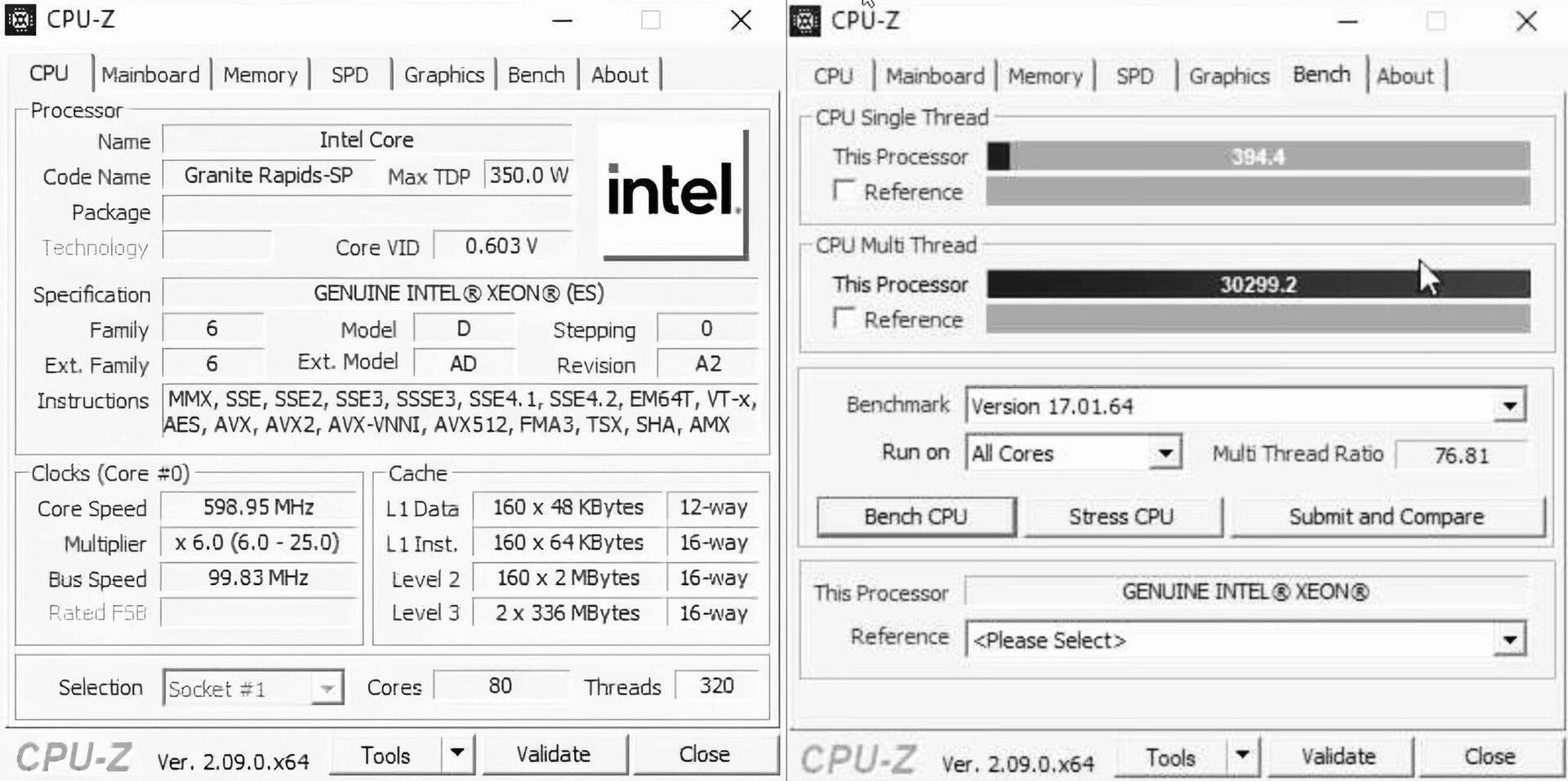

Intel Granite Rapids soll in diesem Jahr als neues Flaggschiff im Xeon-Markt erscheinen. Samples mit 80 Kernen sind bei Partnern und gewähren einen kleinen Einblick in technische Details und unterstützte Features, wenngleich die Auslesetools mit dem Neuling noch etwas überfordert sind.

Granite Rapids setzt nur auf P-Cores

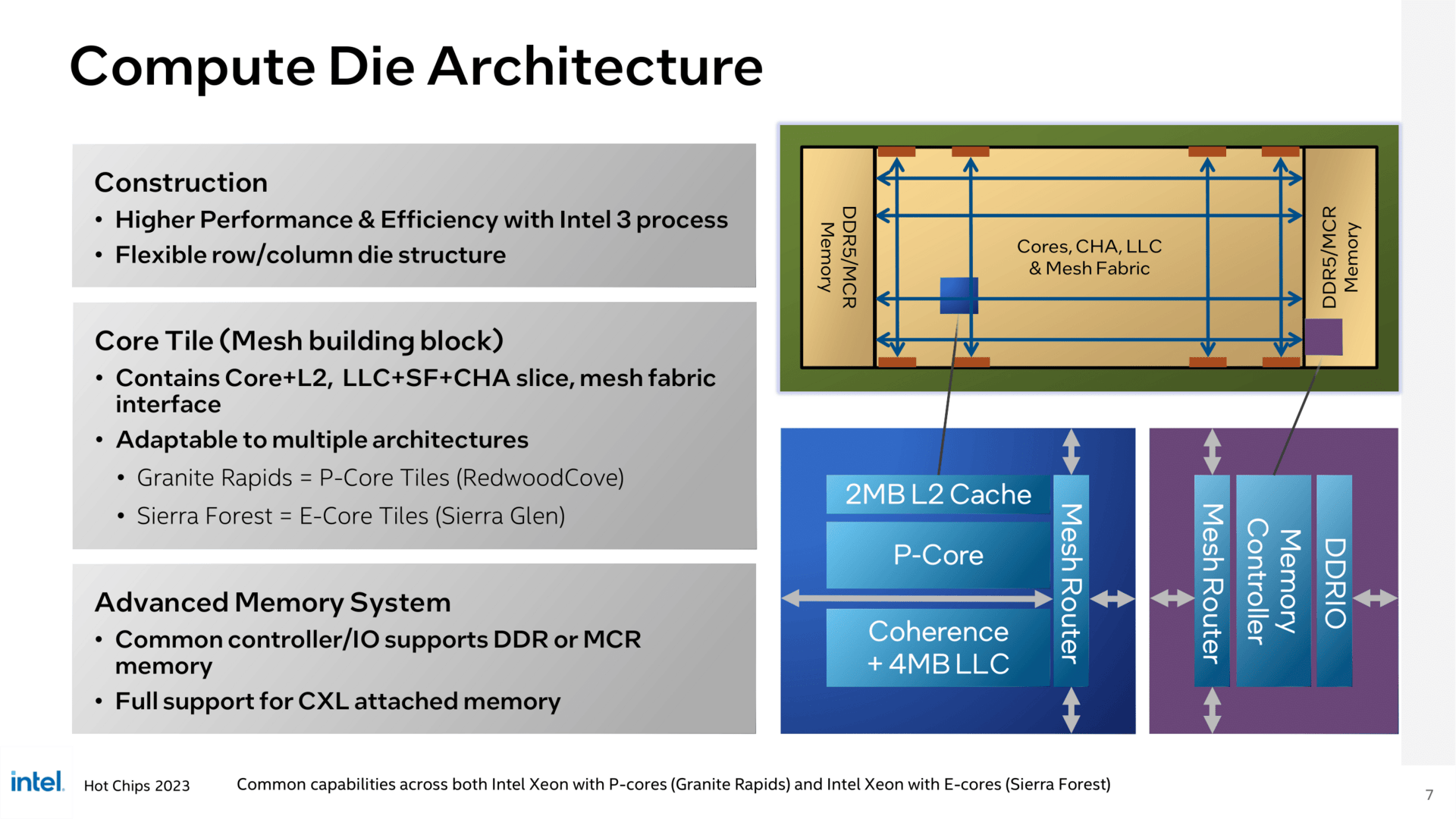

Granite Rapids ist Intels reine P-Core-Lösung, Codename Redwood Cove, für das Jahr 2024 und optimiert für Server. Sie erscheint kurz nach der reinen E-Core-Lösung Intel Sierra Forest, die erstmals diesen Ansatz verfolgen wird.

Bei den P-Core-Prozessoren verfolgt Intel erneut das Ziel, über größere Caches in einigen Bereichen mehr Leistung zu erzielen, so wie zuletzt bereits mit Intel Emerald Rapids vorgelebt. Für Instruktionen gibt es 64 KB pro Kern, für Daten 48 KByte pro Kern. Der L2-Cache soll 2 MByte pro Kern betragen, aufgefangen von einem großen L3-Cache, der sich jedoch nach Größe des Chips und auch Anzahl der Kernen richtet. Beim 80-Kern-Muster wird er mit 336 MByte Kapazität ausgelesen, beim aktuellen Emerald-Rapids-Flaggschiff darf er bei 64 Kernen bereits 320 MByte groß sein.

Einige der Daten, die nun im Screenshot gezeigt werden, hatte Intel im letzten Jahr bereits offiziell bestätigt, darunter die 64 KByte L1-Cache und 2 MByte L2-Cache. Damals hieß es auch, dass pro Kern 4 MByte L3-Cache geplant sind. Dass im konkreten Fall nun 336 MByte L3-Cache vorliegen sollen, deutet daraufhin, dass der Die mehr Kerne bietet. Die 80 Kerne sind zudem doppelt vorhanden, es ist das typische Dual-Sockel-Server-System, weshalb alle Caches und viele weitere Angaben auch mit 160 Mal verfügbar betitel werden.

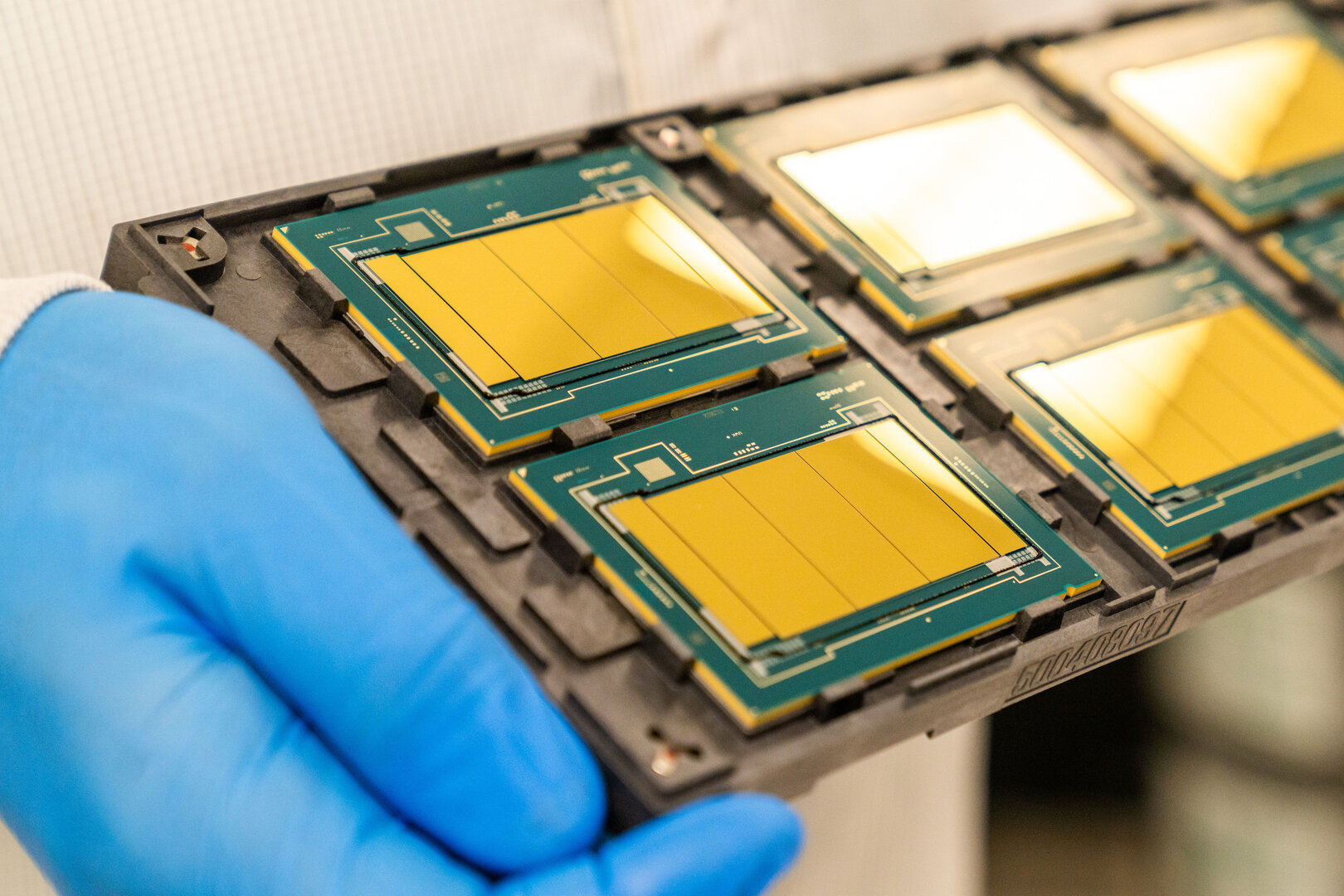

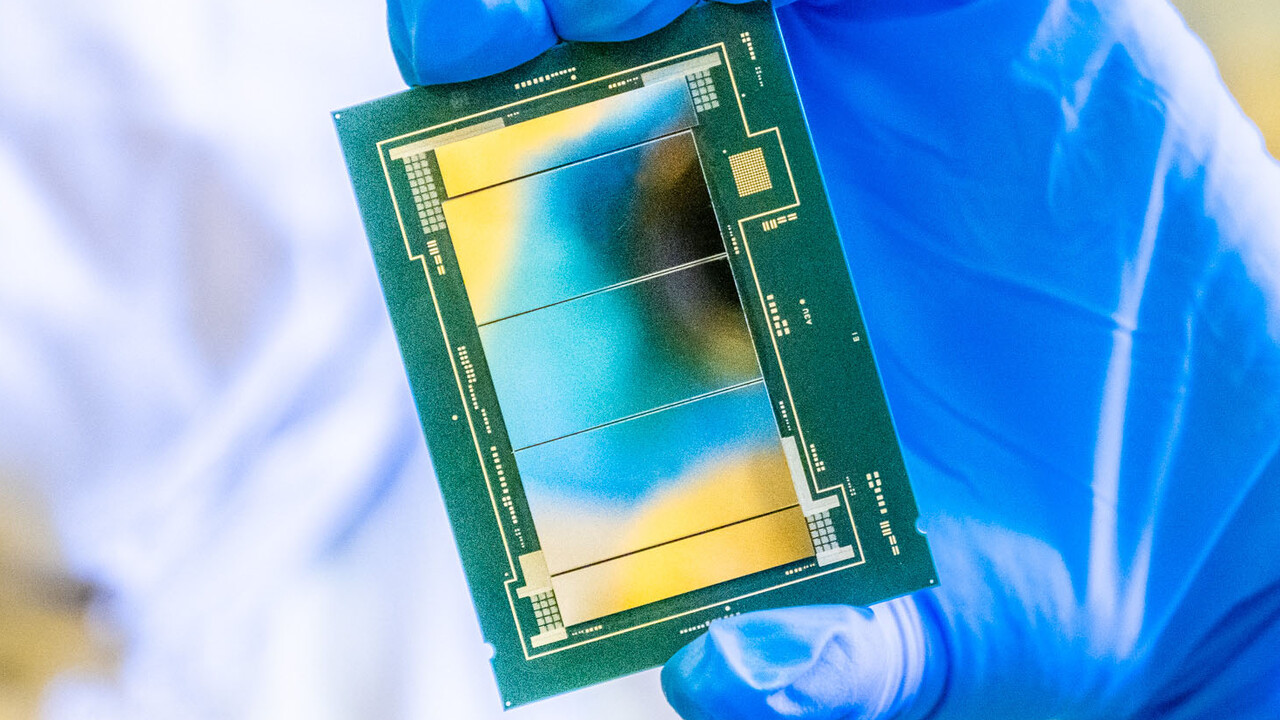

Denn im letzten September hatte Intel überraschend bereits viele Bilder von Granite Rapids veröffentlicht. Diese bestätigten den vermuteten und zuvor bereits in Präsentationen beschriebenen Aufbau mit bis zu drei großen CPU-Tiles, flankiert an beiden Enden von den I/O-Chips. Gerüchte besagten einmal 40 Kerne in der Mesh-Anordnung pro Compute-Tile, also maximal 120 mit drei Kacheln. Letzteres könnte durchaus passen, denn 4 MByte L3-Cache pro Kern würden bei 120 Kernen 480 MByte und damit das „rund halbe Gigabyte“, welches Intel bereits benannt hat, bedeuten.

Die Kerne selbst bekommen ihre typische Überarbeitung beginnend bei der Sprungvorhersage, den Prefetchern, zusätzlichen Instruktionen und mehr.