Nixdorf schrieb:

Ich frage mich, was das für AVX bei den Atom-Kernen (Gracemont?) wird. Die Atom-Kerne müssen es ja anbieten, damit die CPU den erweiterten Befehlssatz dem OS melden kann.

Auf jeden Fall dürfte es wie bei Lakefield wohl kaum möglich sein ein Feature zu melden welches nicht beide Arten von Kernen können.

Hier wird spekuliert das Alfer Lake-S kein AVX512 unterstützen wird, was aber wohl ein Rückschritt zum Vorgänger wäre und damit nicht so wahnsinnig wahrscheinlich.

Nixdorf schrieb:

Also irgendwelche elend lahmen per Microcode simulierten Einheiten, die nur lange genug arbeiten können müssen, bis die CPU die Threads auf die schnellen Kerne umgeschaufelt hat.

"

Gracemont soll zumindest neueres AVX mitbringen", man kann ja auch 512 Bit in zwei Schritten auf 256 Bit breiten Einheiten berechnen, AMD hat es bis Zen2 bei 256 Bit Befehlen auch so gemacht, die liefen auch auf 128 Bit breiten Einheiten ab. Dies bringt dann zwar gegenüber Befehlen in der Breite der Einheiten keinen Performancegewinn, aber elend lahm ist es auch nicht. Wusstest Du übrigens das die Skylake-X/-SP zwei 256 Bit AVX Einheiten haben und daher die Modelle mit einer AVX-512 Einheit gegenüber den 256 Bit AVX2 Befehlen keinen Leistungsvorteil bringen?

Nixdorf schrieb:

Das Switchen von Anwendungen zwischen den Kernen kostet ja "Schwuppdizität", und genau die mag man bei flotten Prozessoren.

Eben, genau um diese Schwuppigkeit zu steigern, hat Intel mit Skylake SpeedShift eingeführt und bei Kaby Lake dann Speedshift 2:

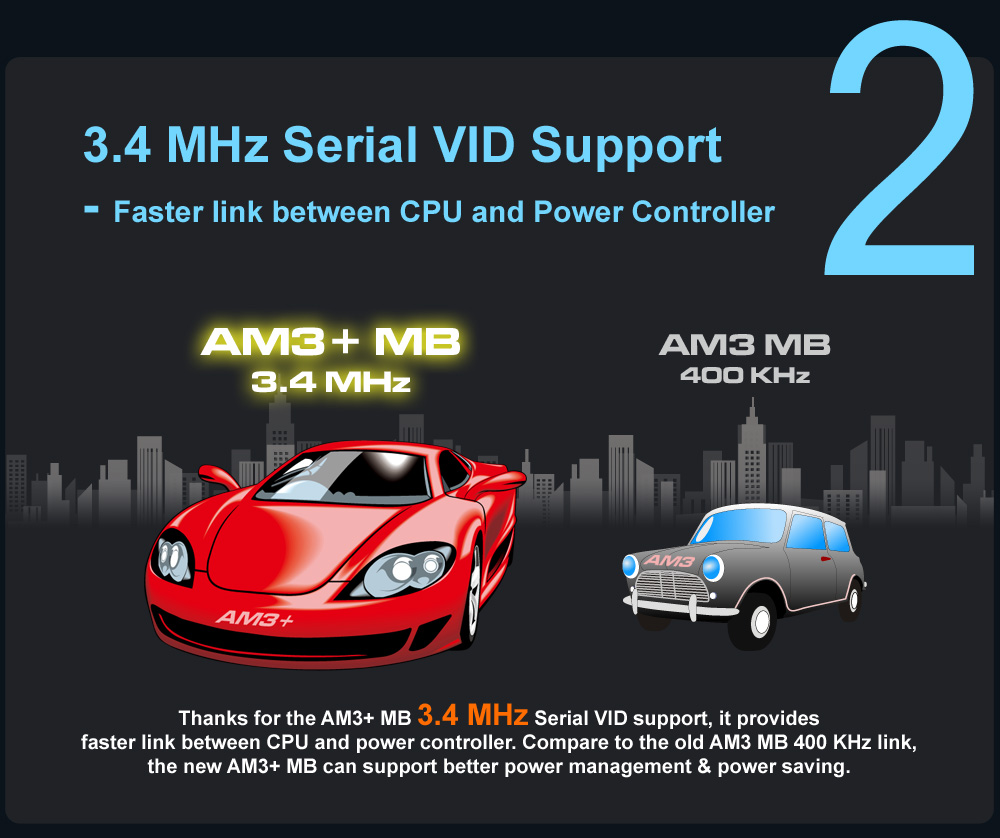

AMD war ebenfalls schon gleich nach der Einführung der Turbotakt mit dem Phenom II für AM3 dabei die Geschwindigkeit der Taktanpassung zu optimieren und hat dafür schon bei AM3+ den Takt der Verbindung zum Spannungsregler deutlich gesteigert:

Deshalb waren AM3+ CPUs im Alltag in AM3 Boards auch so viel langsamer, außer man hat deren Takt im BIOS fixiert, dann spielte es keine Rolle ob sie in einem AM3 oder AM3+ Board saßen. AMD hing dann eine ganze Weile bei dem Thema hinterher, aber bei Zen2 sollen nun die Taktraten innerhalb (weniger als) einer ms angepasst werden können, keine Ahnung in welchem Umfang, aber es zeigt wie wichtig beide Hersteller dieses Thema nehmen, denn es ist für die Schwuppigkeit wichtig: Wenn eine hohe Last anliegt, dann muss die CPU den Takt möglichst schnell anheben, damit diese Last, die Alltag oft nur kurz anliegt, eben auch schnell abgearbeitet werden kann und danach soll der Takt zum Energiesparen möglichst schnell wieder gesenkt werden. Dies bringt (fast) keine Punkte in Benchmarks die länger Dauerlast anlegen wie z.B. Cinebench, macht aber im Alltag der meisten Anwender und auch in Spielen einen durchaus spürbaren Unterschied.

Auch deshalb habe ich ein Problem den Vorteil von BIG.little im Desktop zu erkennen, denn auch ich fürchte das man da einen Rückschritt machen wird. Aber vielleicht hat Intel da ja eine Lösung gefunden, man wird sich da überraschen müssen, denn ich kann mir kaum vorstellen, dass man diesen Aspekt plötzlich aus dem Auge verloren hat. Vielleicht sind die big und little Kerne ja viel stärker integriert als wir jetzt denken oder man schafft es die big Kerne ohne Last viel schneller auf Takt zu bringen und übergibt ihnen dann die Arbeit und ist am Ende trotzdem schneller als wenn man sie unter Last hochtakten müsste. Wer weiß schon was sie sich da ausgedacht haben, aber vergessen werden sie das Problem wohl kaum haben.

Nixdorf schrieb:

Die schnellen Kerne könnte man komplett powergaten, und zum Zeitpunkt des Kontextwechsels sind die dann "kalt" und haben daher mehr thermisches Budget für etwas längeren Turbo.

Silizium leitet die Wärme ganz gut und was TDP und Kühlung angeht, ist dies eher eine Sache für die OEM Rechner, die Retail Mainboard übertakten die CPUs schon in der Default Einstellung ganz gewaltig, selbst die mit H Chipsatz betreiben am liebsten alle Kerne ständig mit dem maximalen Multi, auch wenn der eigentlich nur für Singlethreadlasten ist. Die Enthusiasten schnallen da auch entsprechende Kühler drauf, die K Modelle werden ja schon gar nicht mehr mit einem Boxed Kühler ausgeliefert und drehen gerne noch mehr an der Taktschraube, daher halte ich dies für weniger wahrscheinlich. Zumal die ganzen OEM Kisten und deren Kunden sowieso keinen besonderen Wert auf die maximale Höchstleistung legen, sonst würden sie sich ja nicht solche OEM Kisten holen.

Nixdorf schrieb:

Ach ja, und natürlich ist das dann eine "16-core CPU". Die Kerne sind natürlich auch für exzellentes Marketinggeschwurbel hilfreich.

Dies könnte natürlich sein, wobei es dann aber schnell zu einer Klage kommen könnte, wenn nicht alle 16 Kerne gleichzeitig nutzbar sind. Dies ist nämlich was ein Kunde eines 16 Kerners bisher gewohnt ist und wenn das Marketing da nicht ganz vorsichtig ist, bekommen sie genau wie AMD damals mit den Bulldozer Modulen eine Sammelklage. Damals hatte AMD die 4 Moduler als 8 Kerner, ich meine sogar als 8 native Kerne angepriesen und weil der normale Kunden unter einem Kern eben mehr verstand als eine Hälfte des Moduls geboten hat, endete es in einem Vergleich. Nur hätte AMD diesen Vergleich ja nie geschlossen, wenn sie ihrer Sache sicher gewesen wären und kein negatives Urteil gefürchtet hätten.

Aber vielleicht bringt Intel ja auch da eine Lösung um die big und die little Kerne gemeinsam betreiben zu können, mit entsprechenden Anpassungen beim Task Scheduler des OS sollte dies eigentlich machbar sein. Microsoft hat da ja schon für Zen und seine CCX Architektur und dann für TR mit seinen zwei und später 4 Dies einiges gemacht, die werden Intel da kaum im Wege stehen. Natürlich hätten dann nicht alle Kerne die gleiche Performance (wohl schon wegen der Taktraten) wie es bisher bei Multithreadinganwendungen üblich ist, aber schon bei den RYZEN 3000 12 und 16 Kernern taten nicht immer alle Kerne unter Last gleich hoch, weil nicht beide Dies die gleichen Eigenschaften haben. Klar wäre es bei BIG.little noch extremer, aber im Prinzip ist der Drops schon einmal gelutscht und wäre nur größer.

Es wäre dann auch ein echter 16 Kerner und damit würde BIG.little auch im Desktop wirklich Sinn machen, weil man eben auch die Multithreadperformance damit deutlich steigern könnte, zumindest bei denen mit genug Little Kernen, bei 8+2 wäre dies wohl weniger der Fall.

hoxi schrieb:

So lange Intel seine Herstellungsprozesse nicht in den Griff bekommt, sehe ich schwarz für die Zukunft des Unternehmens.

Das würde ich nicht sagen, die Probleme bei der Fertigung sind zwar ein Klotz am Bein, aber weder TSMC noch GF haben damals die 20nm in den Griff bekommen und somit hingen AMD und NVidia lange bei 28nm fest und waren gezwungen andere Lösungen zu finden um die Performance (vor allem) der GPUs zu steigern, was beide auch geschafft haben. Schau Dir die Leistung der ersten 28nm GPUs an und die der letzten in 28nm gefertigten GPUs, da hat sich viel getan, was man sonst einfach mit den Fortschritten bei der Fertigung hätte erschlagen können, ohne so viel Hirnschmalz reinzustecken. Aber von dem Hirnschmalz hat man dann auch profitiert als der Knoten bei der Fertigung endlich geplatzt war. Daher halte ich es für verfrüht Intel abzuschreiben, denn man sollte die Kreativität der Entwickler nicht unterschätzen, wenn ihnen Hindernisse in den Weg gelegt werden, finden sie oft die erstaunlichsten Lösungen auf die sie sonst nie gekommen wären. Die Geschichte ist voll von Beispielen dafür!

Intel abzuschreiben nur weil es bei der Fertigung klemmt, ist für die AMD Fanboys (egal wie sehr sie es hassen so geoutet zu werden) noch zu früh. Solange AMD nicht auch bei der Gamingperformance vorne liegt, denn dafür zahlen diejenigen sie sich das leisten können und wollen einiges, ist Intel im Desktop nicht geschlagen und wird Aufpreise für CPUs verlangen können, die bei Cinebench billigeren AMD Modellen unterlegen sind.