Faranor schrieb:

Und wie verhalten sich die Latenzen? Ist dort HBM auch besser als DDR?

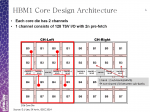

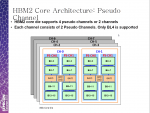

Ja, denn die Adressierung funktioniert bei dem anderes, es wird nicht wie bei DDR RAM nach row und column adressiert, wobei diese sich die Leitung teilen damit es eben nicht zu viele Pins werden und daher werden diese beiden Informationen nacheinander übertragen. HBM geht nur per Interposer oder eben Intel EMIB welches ja ein teilweise Interposer ist, aber eben nicht über andere Verbindungstechniken, weil man eben so viele Kontakte braucht. So viele Kontakte sind über Module einfach nicht realisierbar.

MilchKuh Trude schrieb:

Ich könnte mir vorstellen dass wir sowas sehen werden wie 8gb HBM "Cache" on die und Rest als DDR on board.

Dies ist denkbar, würde die CPUs aber sehr viel teurer machen und daher wird es wenn, dann wohl vor allem bei teuren CPUs wie Server CPUs realisiert werden.

amdfanuwe schrieb:

Könnte mir vorstellen, dass AMD bereits Pläne für eine APU mit 4 oder 8 GB HBM in der Schublade hat und nur noch auf die breite Verfügbarkeit von HBM wartet.

Würde für die meisten Laptops, Thin Clients und Embedded Systeme reichen.

Dafür ist es zu teuer, Interposer sind teuer weil sie auch wie Halbleiter produziert werden und klassische Interposer müssen so groß sein das alle Dies drauf passen. Intels EMIB Technologie hat den Vorteil weitaus kleinere Interposer verwenden zu können, da die eben nur unter einem Teil der Dies liegen. Bei den von Dir genannten Anwendungen ist der Leistungsbedarf zu gering als das man dafür Preise verlangen könnte um solch eine teure Technologie zu rechtfertigen.

amdfanuwe schrieb:

Also in 2 Jahren 7700k Leistung + Radeon 570 + 8GB HBM als Single Chip Lösung?

Eher nicht, denn dann müsste man auch eine Version mit 16GB und eine mit 32GB anbieten, da nicht jedem Kunden nur 8GB reichen, außer man hat eben doch noch ein DDR Interface und nutzt dann das HBM nur für die iGPU, womit man dann bei Kaby Lake-G wäre, denn der gemacht genau dies.

Ozmog schrieb:

Das sieht aber nach dem Artikel anders aus. 2 TB/s pro Sockel möglich mit HBM2.

Weil man ja eben so viele Bits parallel übertragt, also sozusagen sehr viele RAM Channels hat. Dafür braucht man sehr viele Verbindungen und entsprechend viele Verbindung kann man derzeit eben nur über Interposer realisieren.

konkretor schrieb:

ich denke hier entscheidet eher dier Kostendruck, HBM ist ja immer noch sehr aufwendig in der Fertigung besser gesagt beim Stapeln mit dem eigentlichen Prozessor, so lange dies nicht bessere wird, bleibt es in der Nische.

So ist es, EMIB wird die Kosten senken, aber sie bleiben trotzdem hoch.

Herdware schrieb:

Die einzige Möglichkeit wäre wohl, die komplette HBM-CPU/APU gegen ein Modell mit mehr HBM-Speicher auszutauschen. Und auch das nur, wenn das Bauteil nicht direkt verlötet ist.

So ist es, die Vielfalt der CPUs und deren Preise würde also massiv steigen müssen, denn nicht jeder braucht oder will gleich viel RAM, bisher kann man die Menge im einem recht weiten Bereich selbst bestimmen, derzeit dürften bei Mainstream Rechnern Werte zwischen 8 und 64GB üblich sein, mit SMB wären dann statt eines i7 8700K je einer mit 8GB HBM (auf den könnte man vielleicht noch verzichten), 16GB, 32GB und 64GB im Angebot sein um die unterschiedlichen Kundenanforderungen abdecken zu können. Bei Servern wäre es noch schlimmer, da gibt Anwendungen die zwar viel Rechenleistung aber eher wenig RAM brauchen und solche die viel RAM brauchen, wie viele Versionen der ganze sowieso schon zahlreichen Xeon CPUs würden sich daraus ergeben?

Mal davon abgesehen was die HBMs auch Platz brauchen und vor allem wenn man bedenkt das ein normaler LGA3647 Skylake-SP schon 768GB und die M Modelle sogar 1,5TB DRAM pro Sockel unterstützen. So viel braucht längst nicht jede Anwendung, aber wenn die Anwendung so viel RAM braucht, wären die 64GB oder 128GB noch schnelleres HBM die man da maximal mit unter den HS bekommen kann, wohl kein wirklicher Ersatz.

valnar77 schrieb:

Man hat ja am i7 5775c gesehen was ein extra schneller Zwischenspeicher bringen kann.

Ja dessen eDRAM hat vor allem für die iGPU viel gebracht, die GPUs profitieren ja verlangen eben viel RAM Durchsatz, man sieht ja auch beim Vergleich der GPU Performance beiden Raven Ridge APUs wie sehr die RAM Anbindung den größeren offenbar einschränkt. Dem CPU Teil, der ja auch auf das eDRAM als eine Art L4 Cache zugreifen kann, bringt dieser aber nur bei bestimmten Anwendungen wirklich etwas, bei anderen aber nicht. Da ist die Frage ob dieser beschränkte Nutzen die Kosten rechtfertigt und die Kosten waren schon bei dem kleinen und vergleichsweise billigen weil einfacher angebundenem eDRAM das größte Problem. HP denkt wohl außerdem nicht an Cache, sondern daran DDR RAM durch HBM abzulösen.

XTR³M³ schrieb:

oder es ist in zukunft ein sockel für ein HBM modul neben dem CPU sockel, klar, die latenzen dürften minimal höher ausfallen durch die lngeren leitungswege, aber das wäre zumindest extrem kundenfreundlich.

Wäre es, aber es wäre technisch wohl kaum möglich so viele Verbindungen zu realisieren, denn HBM braucht ungleich mehr Pins als DDR RAM.

Jesterfox schrieb:

Bei HBM wird es keine Module geben, der bezieht ja seine Vorteile genau daraus das er mit der CPU/GPU auf einem Interposer sitzt.

Eben, wobei aber der Interposer nötig ist, nur so lassen sich so viele Verbindungen realisieren, dann darauf bezieht HBM die hohe Bandbreite und auch die geringere Latenz. Es ist also eigentlich nicht schnell weil es auf einem Interposer sitzt, sondern weil es so viele Verbindungen, viel mehr Daten- aber auch mehr Adressleitungen hat und daher einen Interposer braucht.

yummycandy schrieb:

AFAIK sind die Latenzen von HBM und GDDR so ziemlich gleich.

Wenn es um die Zellen geht ja, aber die Adressierung verringert bei HBM die Latenz schon etwas.

yummycandy schrieb:

Wichtig sind Platzersparnis und das (mögliche) extrem breite Speicherinterface. Gerade hinsichtlich solcher Geschichten wie EMIB oder Interposer interessant.

Der Interposer ermöglich diese breiten Speicherinterfaces erst, die Platzersparnis ergibt sich daraus, dass der Interposer sehr teuer ist, umso größer der sein muss, umso teurer wird er auch. EMIB ist hier wie gesagt ein Weg die Kosten von Interposern zu senken indem man diese verkleinert und statt die ganzen Dies komplett auf den Interposer zu packen, nur noch einen Teil der Dies über dem Interproser zu haben.

XTR³M³ schrieb:

warum sollte es nicht möglich sein?

Weil man so viele Verbindungen braucht, sonst muss man eben bei der Datenbreite runter gehen, dann fällt aber auch die Bandbreite wieder.

Jesterfox schrieb:

Für ein 1024 Bit Modul kannst du bestimmt das 4-fache an Leitungen gegenüber einem DDR4 Sockel rechnen.

DDR Riegel haben 64 Bit Datenbreite (72 mit ECC), 1024 sind 16 mal so viele und dazu braucht man wie gesagt mehr Adressleitungen. DDR4 SO-DIMMs haben 260 Pins bei 69.6 mm Breite, schon mehr Pins pro mm als die DDR3 SO-DIMM mit ihren 204 Pins bei 67.6 mm Breite und stellt ungefähr das Limit dessen da, was man so an Pins pro mm für solche Verbindungen realisieren kann. Um also 1024 Bit Datenbreite zu realisieren, müsste ein Riegle über einem Meter lang sein.

yummycandy schrieb:

Für nen Stack mit 8 Dies sind wohl nur 4 Leitungen nötig. Wie gesagt, ich lese das so heraus:

Da geht es nicht um die Pins, sondern logische Verbindungen. Pro Datenleitung braucht man mindestens einen Pin, für hohe Frequenzen dann zwei (+ und -, z.B. bei SATA oder PCIe), aber DDR RAM nutzt nur einen Pin pro Bit, keine Ahnung ob HBM nicht sogar zwei verwendet um höhere Übertragungsraten zu erlauben, was dann die Anzahl der Pins nochmal verdoppel würden, mit Ausnahme der Pins für die Spannungsversorgung.

Winder schrieb:

Bei einem 1024 Bit Speicherinterface gibt es auch mindestens 1024 Datenleitungen. (+ Strom, Masse, Schirm)

Plus Adressleistungen und wenn man eine hohe Übertragungsfrequenz ereichen will, dann braucht man sogar zwei.

Winder schrieb:

Das sich manche HBM Chips dieselben Datenleitungen teilen gilt nur für die Chips in einem Stapel(Stack).

Eben und kostet dann wieder Bandbreite, da man ja sonst beide Dies gleichzeitig ansprechen und die doppelte Datenmenge übertragen könnte. Das ist wie bei mehreren DIMMs pro Channel, die bringen im Gegensatz zu mehr Channels auch keinen Performancevorteil, dafür spart man sich aber die ganzen Pins ein, bis auf einen um zu bestimmen welches der beiden DIMMs angesprochen werden soll. Daher kann ja z.B. auch nicht einfach bei einem Board statt Dual Channel mit zwei DIMMs pro Channel durch eine anderen RAM Conntroller Quad Channel ermöglich werden, da man dann doppelt so viele Pins an der CPU für die RAM Slots braucht und diese auf dem Boards anders verschaltet werden müssen. Solange AMD z.B. am AM4 Sockel festhält, kann es also kein CPU mit Quadchannel RAM für den Sockel geben.

Winder schrieb:

HBM ist einfach nicht als Modul möglich, das muss zwingend aufgelötet werden.

Eben, wobei aber die Dies bei Interposern meines Wissens nicht verlötet werden. Auch müssen dort alle Pins eine Alternative Verbindung nehmen können, da immer wieder einzelne Pins keinen Kontakt haben, was die Technik zusätzlich verteuert und wenn zu viele Pins ausfallen, dann hat man Schrott produziert. Interproser sind technisch nicht ohne und sehr anspruchsvoll zu fertigen, die Kosten sind daher entsprechend hoch, aber um so viele Verbindungen zwischen zwei Dies zu realisieren wie HBM sie benötigt, gibt es eben auch keine Alternative.

HBM ist nur entstanden weil die Interposer eben die Möglichkeit bieten die Limitierungen die durch die bisherige Verbindungstechniken gegeben waren, zu überwinden und viel mehr Verbindungen zu machen um die Latenz bei der Adressierung und vor allem die Bandbreite massiv zu verbessern. Wollte man dies als Modul umsetzen, müsste man mit sehr viel weniger Verbindungen auskommen und dann wäre es kein HBM mehr. Deshalb ist HBM als Riegel einfach nicht machbar und nur wer wirklich keine Ahnung von der Technik hat, kann auf solche Ideen kommen. Leider beteiligen sich auch an dieser Diskussion wieder viele denen das Grundverständnis für die Technik komplett fehlt.