DevPandi schrieb:

Habe ich etwas von Problemen mit dem L3/Infinity-Cache geschrieben? Nein! Es geht an dieser Stelle eher darum, wie AMD - wenn Sie es denn weiter verfolgen - bestimmte Probleme bei der Synchronistation der Daten zwischen möglichen GCDs minimiert/eleminiert.

Du hast nicht geschrieben, dass es Probleme mit dem Infinity Cache gibt. Aber wenn die Anbindung des Inifinity Cache über Fanout funktioniert, wieso sollte AMD hier etwas ändern?

AMD verwendet bei Zen 2, Zen 3 und Zen 4 organische Substrate, um die CCDs mit dem IOD zu koppeln Diese Technologie ist für die Bandbreiten-Anforderungen einer CPU gut genug. Fanout mit oder ohne Siliziumbrücken sind nicht notwendig und würden nur die Kosten erhöhen. Also hat AMD hier bisher nichts geändert.

Bei Zen 5 kommt es IMO darauf an, welche Chiplets verwendet werden. D. h. falls AMD bei den CPUs weiterhin nur CCD und IOD verwendet, wird AMD voraussichtlich beim organischen substrat bleibe.Falls AMD etwas wie das folgende verwendet, könnte AMD auch bei den CPUs Fanout benötigen.

US20220101179A1_DirectConnected_MachineLearning_Accelerator - Fig 2B

Bei RDNA3 sind die Bandbreitenanforderungen zwischen Inifinity Cache und Rest-GPU erheblich höher als bei den CPUs. Deshalb hat AMD hier ein Fanout als Lösung gewählt.

Die große Schwäche beim Advanced Packaging von Intel ist IMO, dass Intel offensichtlich nichts mit Fanout im Angebot hat. Meteor Lake liese sich IMO mit Fanout hervorragend umsetzen und wäre damit billiger. Sinnvoll finde ich das Verwenden eines Interposer bei Meteor Lake nur wenn er aktiv ist.

Bei CDNA2 sind die Bandbreitenanfordungen zwischen einem HBM-Stack und dem GCD so hoch, dass Fanout nicht mehr genügt. Deshalb werden HBMs-Stacks dutch Siliziumbrücken mit den GCDs gekoppelt. Das ganze sitzt auf einem Fanout und AMD nennt es Elevated Fanout Bridge (EFB)

DevPandi schrieb:

AMD hat verschiedene Patente gezeigt, ob AMD diese auch umsetzt, darüber kann man spekulieren. Deren aktuellen Lösung ist, dass über den L2/L3-Cache eine schnelle Verbindung gelegt wird in den Patenten.

Es muss schnell sein (Latenz & Bandbreite*), es sind sehr viele Verbindungen**) erforderlich. Wenn AMD eine GPU aus einzelnen GCDs integrieren will müssendie Scalable Data Fabrics der einzenen GPU-Chiplets miteinander gekoppelt werden. All dies ist nur mit Siliziumbrücken möglich.

US20200409859A1 Fig 3

*) Die Brücke muss es ermöglichen, dass die GCD mit derselben Bandbreite auf den Speicher der anderen GCDs wie auf den eigenen zugreifen kann. (Hotchips 34, Frage und Antwort zu CDNA2-Vortrag)

**) Forrest Norrod nannte in einem Interview 20 000 Verbindungen.

DevPandi schrieb:

Bei CDNA3 und bei der Mi300 geht AMD einen anderen Weg, den sie angekündigt haben. Der Base-Tile enthält den L3-Cache zusammen mit den Memory-Contollern und dem IO-Interface.

AMD hat Varianten mit passiver Brücke und Varianten mit aktiver Brücke gezeigt. Kern dieser Patente war immer die Verbindung zwischen den GCDs. Wo die Memorycontroller sitzen spielt für diese Patente eigentlich keine Rolle. Die IO wurde in diesen Patenten gar nicht extra gezeigt.

Da gibt es auch ein extremeres Patent, Chiplets auf Chiplets, die mit Brücken gekoppelt werden:

US 20220320042A1 Fig 7

Auch hier wollen wir eine RDNA sehen. So wie das Memory Module angekoppelt ist spricht es sogar dafür. Aber ein solcher Wurf ist IMO für RDNA auf absehbare Zeit viel zu teuer.

DevPandi schrieb:

Etwas "ähnliches" kann auch für zukünftige RDNA-Entwicklungen erwarten, ob es kommt, keine Ahnung, ein entsprechender Basetile mit dem Infinty-Cache und den RAM-Controllern würde aber einige Probleme relativ elegant und einfach lösen und hätte den primären Vorteil, dass man sich bei dem Interconnect zwischen den GCD etwas weniger Gedanken machen muss.

Sobald AMD beschließt auch bei RDNA Multi-GCD-GPUs zu machen, wird auch bei RDNA eine Siliziumbrücke notwendig. Dann wird man auch sehen, ob die Brücke aktiv oder passiv wird, ob sie oben oder unten (Sockel) angeordnet wird.

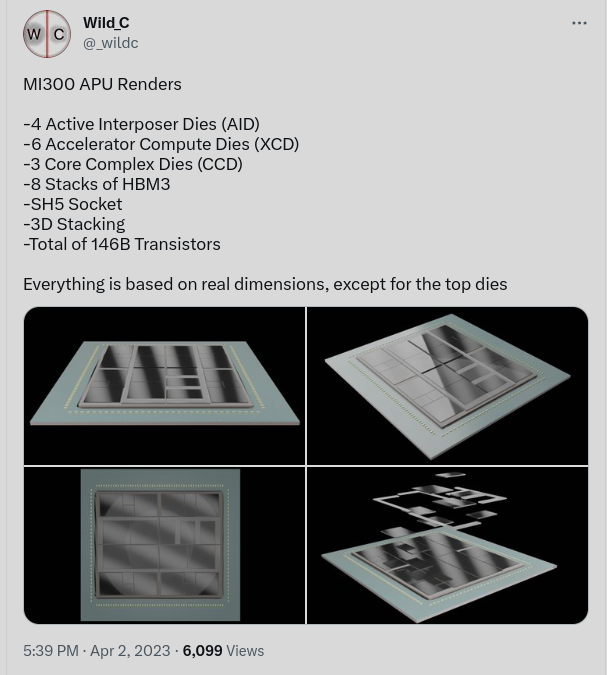

Bei CDNA3 ist Brücke zwischen 2 XCD (Accelerator Compute Die) aktiv. Sie wird Mal AID (Active Interposer Die) oder Mal Base Die genannt. Die beiden XCD sitzen auf dem AID. Die Frage ist, ob die ganze Fläche des AID tatsächlich genutzt wird. Nur wenn die ganze Fläche tatsächlich genutzt wird, ist es tatsächlich elegant. Aber die MI300 APU ist so teuer, dass es auf ein paar mm² totes Silizium nicht wirklich ankommt.

Was aber AMD bisher noch nicht verraten hat, ist wie die 4 Base Dies gekoppelt werden. Erst eine schnelle und ultra breite Kopplung macht aus der ganzen Geschichte eine APU. Da die Kopplung auf den Fotos nicht zu erkennen ist, muss sie unter den Base Dies sein. Deshalb gehe ich von einer passiven Brücke aus. Mit Hybrid Bonding und einem Pitch von 6 µm muss sie gar nicht so groß sein.

CDNA und RDNA sind verschiedene Welten.

Die RX7900XTX hat eine Speicherbandbreite von 960 GB/s

HBM3 ermöglicht je Stack eine Bandbreite von bis zu 819 GB/s, wir werden es bald wissen welches Tempo die MI300 erreicht. Die H100 gibt sich AFAIK mit läppischen 600 GB/s je Stack zufrieden.

Neben den anderen Anforderungen an die Speicherbandbreite unterscheidet sich auch der Verkaufspreis ganz erheblich. Auch die GPU-Variante (ich nehme an 1 AID + 2 XCDs) wird preislich deutlich über einer RX7900XTX liegen.

DevPandi schrieb:

Zudem - und dass ist der entscheidende Punkt - widerspricht, besser steht meine Spekulation nicht in Widerspruch dazu, "dass sie relativ preiswerte Technik (Fanout) verwendet und skaliierbar ist". AMD hat bisher 3 Chips für RDNA3 in "Planung" wovon 2 Chips auf dem Markt sind: Navi31 und Navi33. Aktuell gibt es ein relativ großen GCD und kleine MCDs und dazu eben einen Monolith. Für Navi32 ist ein "mittlere" GCD geplant, wir haben also 4 Chips. In meiner Überlegung - wenn wir jetzt darauf hinaus gehen - kann es theoretisch auch bei 4 Chips bleiben: Kleine, mittlere und große Basetiles mit 128 Bit SI, 256 Bit SI und 384 Bit SI und der entsprechende Menge an Infinity-Cache und "kleine" GCDs, die vielleicht nur noch 2 Shader Arrays beherbergen. Am Ende planzt man dann 2 GCD auf ein Basetile, 4 GCD und 6 GCD. In den alten Prozessen werden also "größere" Chips gefertigt, da die Prozesse gut erprobt sind und man auch da ggf. auslasten muss, hat man hier zwar dann "teurere" Chips, gleichzeitig hat man dann aber bei den teuren Prozessen kleinere Chips - die "etwas" günstiger werden und kann hier die "noch" schlechte Yield-Rate kompensieren.

Der GCD von Navi 31 hat ca 300 mm², der GCD von Navi 32 hat ca 200 mm². Da ist noch Luft nach oben. Und wahrscheinlich wird es N3E, was auch noch ein bisschen Skalierung bringt.

Deshalb IMO wird AMD bei RDNA4 bei einem GCD bleiben.

DevPandi schrieb:

Das die 7900 XTX entsprechend der ALUs agieren kann, sieht man gerade an

Dead Island 2, hier schafft die 7900 XTX 7 % im Mittel und 15 % bei 99,9%. Und genauso sieht man es bei Spielen wie

Call of Duty: Vanguard. Hier schiebt sich die Karte quasi die Erwartungen erfüllend bei der ALU-Anzahl zwischen 4080 und 4090. Man schafft mit 20 % mehr ALUs also ca. 15 %, während die 4090 mit 33 % ca. 25 % drauf legt. Die Karten fügen sich also gut ineinander.

Du greifst Dir 2 Spiele raus, bei denen die 7900XTX sehr gut abschneidet. Da kann sie bei der auf die Shaderanzahl normierten Performance mit Nvidia mithalten.

Wie sieht es mit der Effizenz aus? Liegt sie da auch auf dem Niveau von Nvidia?

Im Mittel liegt die 7900XTX bei der Performance ziemlich gleich auf mit der RTX4080. D. h. auf die Shader normiert liegt sie hinten. Außerdem ist Effizienz der RTX4080 besser.

Dann gibt es noch Spiele bei denen die 7900XTX von der Performance erheblich schlechter aussieht.

Soweit ich es mitbekommen habe ist es nicht so, dass die 7900XTX bei allen neuen Spielen (bei denen AMD den Treiber quasi von Hand optimieren kann) sich von der RTX4800 absetzen kann.

DevPandi schrieb:

Warum? AMD, NVIDIA, Intel und Co sind alles Firmen, die entsprechende Produkte planen und testen und im Lauf feststellen, dass es noch besser geht und haben entsprechend auch nach einer Generation auch den nächsten Schritt gemacht. AMD hat bei Zen auch nicht den Ansatz der ersten Iteration bei Epyc bei behalten und hat mit Zen 2 das Konzept quasi auf Links gedreht.

Und dieses Konzept mit Zen 3 und Zen 4 beihalten.

Sam Naffziger hat erklärt wieso AMD bei Zen 2 auf das Chiplet-Konzept umsteigen musste:

DevPandi schrieb:

Bei GPGPU und dem ML/DL-Stack ist AMD relativ gut aufgestellt, auch mit der Fusion mit Xilinx. Klar, es könnte besser sein, CUDA wird AMD aber nicht brechen und entsprechende Arbeiten an ROCm laufen weiter voran. Im HPC-Bereich kann man ROCm bereits sehr gut verwenden und auch für andere Beschleunigung, die aktuell über CUDA läuft, kann man bereits sehr gut damit arbeiten. Hier ist das Problem eher ein altbekanntes von AMD: Bis auf "Dokumentation", kommt leider nicht viel Unterstützung von Seitens AMD. Auch hier liegt die Hoffnung auf der Übernahme durch Xilinx und dass diese eine bessere Softwaresupport-Kultur bei AMD mitbringen und da meine ich nicht die Pflege der Software.

Bei GPGPU ist AMD nur im HPC-Bereich (CDNA) einigermaßen gut aufgestellt.

Aber ansonsten ist es mau.

IMO muss man 2 Ebenen unterscheiden:

- Programmieren der GPU

- Programmieren die Möglichkeit geben über das Verwenden von Bibliotheken die GPU einzubinden

Was ich damit meine ist, nicht jede Person die Software schreibt, will sich mit der GPU-Programmierung auseinander setzen.

AMD erzählt in letzter Zeit wiederholt wie toll ROCm ist. Hier hat AMD auch ordentlich Arbeit reingesteckt. Allerdings gibt es von AMD bis heute keine klare Roadmap wie ROCm und vor allem HIP außerhalb des HPC verfügbar werden soll.

Dazu gehört auch, dass AMD HIP für RDNA überhaupt erst verfügbar macht.

DevPandi schrieb:

RT wiederum ist eine sehr große Baustelle und AMD und Intel geraten hier massiv in Zugzwang, wenn beide Firmen nicht versuchen möglichst bald auch entsprechend irgendwie den Takt mit zu gestalten und auch wenn die erste RT-Implementierung von Intel nicht schlecht ist und AMD mit RDNA3 vieles besser macht, hier dominiert aktuell NVIDIA und zwar auf allen ebenen, nicht nur bei Spielen, sondern auch im professionellen Bereich.

Beim Professionellen Bereich haben wir wiederum das leidige Theme HIP. Wie soll jemand etwas ohne HIP-RT für AMD-GPUs programmieren?

Bei den Games sehe ich das ein bisschen anders. Beim Rastern bringt RDNA3 die versprochene Performance nicht auf die Straße und hat Boden auf Nvidia verloren. Beim Raytracing konnte RDNA3 den Rückstand verkürzen.

DevPandi schrieb:

NVIDIA kann sich bei CUDA relativ gemütlich zurück lehnen, den Markt haben sie weitgehend fest im Griff.

Hier finde ich den Ansatz gut, den AMD mit HIP verfolgt. HIP orientiert sich sehr stark an Cuda und kann auch sehr effizient für Nvidia Grafkkarten kompiliert werden.

Das eröffnet zumindest die Chance, dass jemand in Cuda geschriebene Software auf HIP portiert. Ob sich Leute überreden lassen HIP zu verwenden, um für Nvidia zu programmieren? Das wird hart.

DevPandi schrieb:

Das geht sogat soweit, dass Leute GPGPU als "Erfindung" von NVIDIA ansehen und ATi/AMD vorwerfen, dass sie ja hier nur NVIDIAs "Innovationskraft" ausnutzen und stören wollen und sie ja deswegen OpenCL "ünterstützt" haben und dabei vollkommen vergessen, dass ATi mit der FireStream-API über ein Jahr vor NVIDIA ihr Produkt vorgestellt hat und NVIDIA hier "ATi" quasi hinterher liefen.

Und hier haben wir wieder etwas was sich Execution nennt.

Die war damals bei AMD und ATI nie so überragend, heute ne gute Idee, morgen ne schlechte Idee. Bei Nvidia gab es eben einen Plan und der wurde konsequent entwickelt und umgesetzt. Und wenn man etwas konsequent entwickelt und umsetzt, spielt es eben keine Rolle, ob man etwas später angefangen hat.

Bei AMD kam natürlich dazu, dass die Entwicklungsbudgets nach 2010 zusammengestrichen wurde.

DevPandi schrieb:

Bei DL/ML ist NVIDIA zwar medial in "Techforen" stark vertreten und das erweckt bei manchen den Eindruck dass auch hier CUDA quasi der Goldstandard ist, zum Glück ist dem aber nicht so und die meisten Entwickler greifen auf die DL-Frameworks von Google (Tensorflow) oder Meta (PyTorch) zurück, die weitgehend darauf ausgelegt sind, dass man Hardware unabhängig.

Die nächsten zwei Jahre werden spannend. Wie viele der KI-Hardware-Startups können sich tatsächlich am Markt etablieren?

DevPandi schrieb:

Gerade Xilinx bringt hier viel Erfahrung mit und war Forschungspartner für viele Projekte. Xilinx "Übernahme" ist für AMD hier absolutes Gold, weil man hier auf die Kompetenz von Xilinx zurück greifen kann.

IMO war die AIE einer der wichtigsten Gründe warum AMD Xilinx gekauft hat und der Grund warum sich Xilinx aufkaufen lies.

AMD hätte es unmöglich schaffen können abseits vom HPC etwas bei KI auf die Beine zu stellen. Und Xilinx war zu klein, um das Potential der AIE zu heben.

DevPandi schrieb:

Klar, hier in den News scheint es so, dass NVIDIA vollkommen dominant ist, dass sind sie aber nicht wegen CUDA, sondern weil sie an der Stelle die beste Hardware fürs Training haben. Klar, AMD muss bei den eigenen Matrix/Tensor-Kernen aufholen, hier müssen Sie aber primär dann nur den "Treiber" für die Frameworks entsprechend stemmen und stehen nicht in Konkurenz zu CUDA.

HPC/GPGPU und ML/DL sind also Felder, bei denen AMD eher bei Consumern, die solche Seiten wie hier lesen, als abgeschlagen angesehen werden, im professionellen Bereich aber immer noch als Alternative - und nicht nur eine "günstige" - wahrgenommen werden und entsprechend auch Aufträge bekommen.

Hier wollen einige Firmen unbedingt eine Alternative zu Nvidia. Und deshalb sehen sie über Unzulänglichkeiten bei AMD hinweg und helfen AMD.

Hier wird sich in den nächsten 2 Jahren zeigen, ob sich AMD und Xilinx wechselseitig auf ein neues Niveau heben können.

DevPandi schrieb:

Ein Problem hat AMD in diesem Bereich eher - und damit der Zirkelschluss zum ersten Absatz dieses Abschnittes - bei Anwendungen für Content-Creators. Im OpenSource-Bereich - Blender und Co - werden entsprechend Implementationen in der Regel von Entwicklern vorgenommen, die einen akuten Bedarf danach haben oder weil sie von den Herstellern unterstützt werden oder Hersteller auch entsprechende Ressourcen bereit stellen. Wenn AMD hier irgendwann "besser" sein will, dann müssen Sie Ressourcen für Blender und Co freischaufeln/schaffen, die die Entwickler dort unterstützen. Hier haben wir ein klassisches Henne-Ei-Problem. AMD schneidet nicht schlecht ab, aber auch eben nicht so gut, wie möglich wäre. Die Leute kaufen daher NVIDIA, weil es läuft und der Softwaresupport da ist. Die großen Firmen wiederum "optimieren" nicht für AMD, weil die Kundenbasis fehlt, wodurch wieder ... Zirkelschluss.

Hier war ich ehrlich gesagt sehr enttäuscht wie lange es gedauert hat, bis die HIP-Schnittstelle bei Blender in Betrieb gehen konnte und wie lange es jetzt wieder dauert bis HIP-RT für Blender verfügbar wird. Und das trotzt massiver Unterstützung von AMD.

Ich finde die Entscheidung von 2015 nach wie vor richtig, die wenigen Resourcen in die Entwicklung von ROCm zu konzentrieren. Nur damit konnte AMD wenigstens im HPC Fuss fassen. Aber so langsam müssen eben die nächsten Schritte kommen.

Dauerhaft erfolgreich kann AMD nur werden, wenn mit und für die verfügbaren RDNA-Grafikkarten GPGPU programmiert wird. Aber momentan ist das eigentliche Problem, überhaupt programmieren zu können.

DevPandi schrieb:

Und bei RT droht AMD - und Intel - an dieser Stelle das gleiche Schicksal und genau deswegen ist es wichtig, dass AMD hier Ressourcen frei macht und auch das Geld in die Hand nimmt. ...

Ich habe mich im Detail nicht mit RT beschäftigt.

Was Nvidia eindeutig von AMD und Intel unterscheidet, ist wie zielstrebig und konsequent Nvidia sich Ziele setzt und diese dann auch umsetzt. Und sich eben dann nicht dafür feiert, sondern die nächsten Ziele setzt. Nvidia hat in den letzen beiden Jahrzehnten immer gut abgeliefert und dabei konsequent mehrere neue Geschäftsfelder aufgebaut bzw. zugekauft.

AMD arbeitet erst seit Lisa Su und Mark Papermaster an Bord sind konsequent. Forrest Norrod hat in einem Interview ausdrücklich schlechte Execution als das Hauptproblem von AMD in den 2000er Jahren genannt.

Wie Du andeutest steht und fällt AMD im Gamingbereich mit den Konsolen. Im PC-Markt ist AMD nach wie vor ein Underdog.

Das Nvidia durch neue Technologien den Performance-Hunger der Spiele und die Leistungsfähigkeit der GPUs pusht hat meiner Meinung nach klare Gründe. Nvidia kann keine APUs anbieten. AMD und Intel bieten immer stärkere APUs an.

Nur wenn der Performance-Hunger der Spiele kontinuierlich weiter steigt kann Nvidia die APUs auf Abstand halten. Das Problem für Nvidia ist der Notebookmarkt. Auf dem Desktopmarkt werden die APUs mit ihrem beschränkten Power-Budget immer nur Einsteigerlösungen bieten können.

Im Notebookmarkt ist das Powerbudget beschränkt und nur für ein Teilsegment des Marktes können sich die dGPUs wirklich austoben. in den nächsten Jahren wird der Anteil der Notebooks zunehmen, die keine dGPU mehr haben. Dafür sorgen sowohl AMD als auch Intel. Gaming-Notebooks mit starken dGPUs werden weiter nachgefragt und es werden IMO nur die schwachen dGPUs in den Notebooks seltener werden. Es sind nicht die margenträchtigen GPUs. Aber wie es so treffend heißt, auch Kleinvieh macht Mist.

Im Desktopmarkt bin ich wirklich gespannt wie es weitergeht. Die RTX4090 wird gut laufen, weil die Creators auf diese Karten setzen. Da sind wir einer Meinung. Diese haben aktuell und auf absehbare Zeit nur die Option bei Nvidia zu kaufen. Aber wie geht es mit den kleineren Karten weiter?

Wie viele Leute sind bereit die Preisspirale bei den Gaming-Grafikkarten mitzudrehen?