adrianbauerino

Ensign

- Registriert

- Jan. 2023

- Beiträge

- 174

Hi Freunde,

ich habe da mal ein Problem ...

Das oben genannte Mainboard ist an sich ja nicht schwachbrüstig und daher wurde es erworben ...

Ich habe auf dem PCIE 1 eine 6800 XT mit hoffentlich x16

auf dem M2_1 (insgesamt sind es 4 M2 Slots) eine SN850 von WD PCIE 4.0 x 4

auf dem M2_4 habe ich nun eine Samsung 970 Evo Plus eingeklickt auf PCIE 3.0 x 4

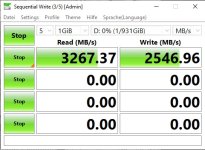

nun habe ich im SSD Benchmark festgestellt, dass weder die SN850 eine vorgegebene Leserate an die 7000 MB/s (im Test "nur" 6000) erreicht noch, dass die Samsung 970 Evo Plus auch nur die ansatzweise versprochenen 3500 MB/s für Lesen und Schreiben erreicht

(hier sind es nur 2200 beim Lesen und 1500 beim Schreiben)

Ich habe mir dann Gedanken gemacht, was meine CPU an Lanes zur Verfügung stellt und bin bei dem 5900x auf 24 Lanes gekommen ...

hiervon werden nun 16 für die GPU und 4 für die M2_1 in 4.0 x 4 genutzt ... demzufolge müssten auf M2_4 doch noch volle 4 Lanes zur Verfügung stehen die die M2_4 dann komplett aus dem Chipsatz befeuern können und maximale Geschwindigkeit bedeuten oder nicht ? Eventuell habe ich auch keinen Denkfehler

hier nochmal aus dem Handbuch die einzelnen Slots

Danke für die Hilfe

ich habe da mal ein Problem ...

Das oben genannte Mainboard ist an sich ja nicht schwachbrüstig und daher wurde es erworben ...

Ich habe auf dem PCIE 1 eine 6800 XT mit hoffentlich x16

auf dem M2_1 (insgesamt sind es 4 M2 Slots) eine SN850 von WD PCIE 4.0 x 4

auf dem M2_4 habe ich nun eine Samsung 970 Evo Plus eingeklickt auf PCIE 3.0 x 4

nun habe ich im SSD Benchmark festgestellt, dass weder die SN850 eine vorgegebene Leserate an die 7000 MB/s (im Test "nur" 6000) erreicht noch, dass die Samsung 970 Evo Plus auch nur die ansatzweise versprochenen 3500 MB/s für Lesen und Schreiben erreicht

(hier sind es nur 2200 beim Lesen und 1500 beim Schreiben)

Ich habe mir dann Gedanken gemacht, was meine CPU an Lanes zur Verfügung stellt und bin bei dem 5900x auf 24 Lanes gekommen ...

hiervon werden nun 16 für die GPU und 4 für die M2_1 in 4.0 x 4 genutzt ... demzufolge müssten auf M2_4 doch noch volle 4 Lanes zur Verfügung stehen die die M2_4 dann komplett aus dem Chipsatz befeuern können und maximale Geschwindigkeit bedeuten oder nicht ? Eventuell habe ich auch keinen Denkfehler

hier nochmal aus dem Handbuch die einzelnen Slots

Danke für die Hilfe