BreadPit schrieb:

Sehe grad MSI 1.2.0.A BIOS ist da für mein MSI B550I . Hat jemand schon Erfahrung damit?

Ich hab jetzt Erfahrung damit

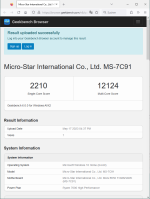

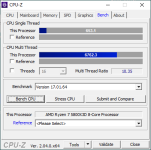

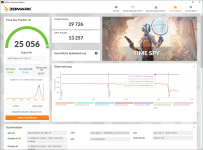

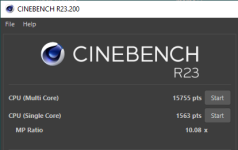

Das

1.2.0.A BIOS erlaubt jetzt das Einstellen von PPT / TDC / EDC, Scalar und Temp Limit in Verbindung mit CO per Core.

1.2.0.A find ich also wirklich super! Die Limitierung auf 130A EDC ist damit Geschichte, rennt jetzt mit 140A und CO!

Was immer noch vorhanden ist, der der S3UV-Bug.

AMD WIE PEINLICH IST DAS EIGENTLICH DASS SEIT JAHREN PER SLEEPMODE DIE VCORE UM 0,05V ABGFESENKT WIRD, OHNE DASS DAS KORRIGIERT WIRD? Wo kann man diesen R. H. kontaktieren, das pack ich grad wirklich nicht. Wobei ich auch bei einer Firma arbeite, die so manch offensichtliche Unzulänglichkeit nicht in atemberaubendem Tempo ausmerzt...

Dennoch, ehrlich - mit so einem offensichtlichen und in einschlägigen Kreisen bekannten Bug braucht sich AMD nicht wundern über den Ruf, nicht so stabil zu sein wie Intel.

Nach dem Sleep Mode die CPU-Spannung ändern, und das über Jahre - ECHT JETZT?! Da schließe ich immer draus, dass die Programmierer ihre eigenen Produkte nicht wirklich nutzen, anders gibts das ja nicht.

Sry das musste mal raus. Bin ja AMD Fanboy seit der ersten Stunde, und (Klein-)Aktionär (leider erst seit 2020

) , aber so was........

MehlstaubtheCat schrieb:

Ich bin aktuell noch immer dran mit CL14 dann tPHYRDL auf 26 zu bekommen.

Es will mir einfach nicht gelingen, egal welche Widerstandswerte etc ich eingebe.

Das ist in SW definiert so weit ich das verstehe.

MehlstaubtheCat schrieb:

Stellt sich eben immer noch dir Frage

CL14 > tPHYRDL 28

CL15 > tPHYRDL 26

letztes scheint bei mir nur in AIDA etwas niedrige Latenz zu geben.

Genau das. Latenz niedriger, Durchsatz quasi gleich, ich fahre also CL19/tPHYRDL26 @ 1,30V statt 18/28 @ 1,32V.