Krautmaster

Fleet Admiral

- Registriert

- Feb. 2007

- Beiträge

- 24.418

Eleanor1967 schrieb:Ich glaube Intel kann das besser bewerten als du ob das Sinn macht oder nicht.

Krethi & Plethi schrieb:da wäre ich mir nicht so sicher, SMT4 bei so schwachen kernen wird nicht viel bewirken, wenn es kaum ressourcen gibt bringt auch ein lückenfüller nix!

da bin ich mir sogar ziemlich sicher, ziemlich also quasi ganz sicher, ja doch, relativ sicher

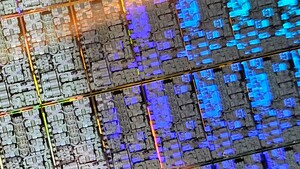

Bei dem Intel Monster geht es ja weniger um maximale DP Leistung, viel eher darum diese auch wirtschaftlich und vergleichsweise einfach abrufen zu können. Wer spezielle, sehr spezielle Szenarien hochoptimieren kann ist mit ner reinen klassischen GPU meist besser beraten. Schau dir 5D bei der HD5850 an, die haut heute noch was Crunchen und Mining angeht Hawaii in die Pfanne, gerade auch bei / Transistor Leistung. Weils eben perfekt auf die Architektur gepasst hat...

Nai hat das super erklärt. Viele Szenarien passen auf PHI weit besser als auf eine GPU die ebenfalls zunehmend breiter aufgestellt wird. Es ist immer Frage der Anwendung... die Systeme als solche nur schwer vergleichbar.

Auf dem PHI sollte man vergleichsweise einfach Windows / Linux booten können... versuch das mal auf Hawaii. Geht sicher... nur mit welchem Aufwand.

Zuletzt bearbeitet: