Armandex0 schrieb:

Für mein begrenztes Verständnis steht in dem zitierten Artikel eigentlich prinzipiell genau das, was Nai gesagt hatte...

[...]

Sofern HBM keine Möglichkeit der Speicherverschränkung hätte, wäre ja die ganze tolle Bandbreite plötzlich "für die Katz" und man müsste ständig für mehr Bandbreite -also das Interface am Grafikchip- sorgen wenn man dann doch mal mehr Speicher verbauen möchte?

Inwiefern steht da genau das was er gesagt hat?

Dies ist doch eindeutig Gegenteilig:

Nai schrieb:

weil sie dank des interleaved Layouts sowieso immer in etwa gleich belastet werden, bzw. bei unterschiedlicher Taktung immer der langsamste Kanal das gesamte Interface limitieren wurde.

Technische Beschreibung schrieb:

All DRAM timing restrictions are limited to a single memory module and not across memory modules.

Übersetzung: Alle DRAM Timing Beschränkungen sind limitiert auf ein einzelnes "memory module" und nicht übergreifend auf alle memory module (sollte hier nochmals die Definition von "memory module" aus der Quelle nötig sein, übersetze ich diese auch gerne)

Das tFAW timing verhindert zudem, dass mehr als 4 banks Interleaved angesprochen werden können in einem rotierenden Zugriff:

To make things worse, the DDR protocol puts another limitation for DRAM is tFAW timing. It restricts access of more than 4 banks in a rolling time window - tFAW.

->Damit ist nachgewiesen, dass Interleaving nicht über alle Speichermodule hinweg stattfindet. Damit ist schon die Grundlage überhaupt nicht gegeben zu behaupten deswegen können einzelne Speicher Segmente nicht unterschiedlich getaktet werden hinfällig.

Die weitere Annahme, dass HBM überhaupt Interleaving benötigt um nicht zu langsam zu sein ist fehlerhaft.

Auf dir Frage hin auf welches Weise sonst HBM optimiert wenn nicht mit Interleaving, habe ich auf die HBM Specs verwiesen die das beschreiben.

Was sollte bei HBM so konkret anders sein, dass das interleaved Layout nicht mehr benötigt wird?

Daedal schrieb:

Es nennt sich Dual Command Interface und ist in der selben Quelle beschrieben die du schon mehrfach selber verlinkt hast zu HBM.

Hier gerne auch die detailierte Beschreibung der relevanten Teile:

Aus der Hotchips Quelle:

http://www.hotchips.org/wp-content/...Bandwidth-Kim-Hynix-Hot Chips HBM 2014 v7.pdf

Seite 15:

Row/column input through different pins

->Daraus folgen Änderungen im Zugriff auf den DRAM, wie folgt beschrieben auf Seite 16:

Es ermöglicht den bisher nicht möglichen

Single Bank Refresh

->Daraus folgt die auf Seite 17 beschriebene Optimierungsmöglichkeit mit der Überschrift:

Command bus efficiency can be maximized

Darunter stehen die verwendeten Techniken: Dual Command & REF single bank

Die zweite verfügbare technische Quelle von der Memcon führt dies nun detailierter weiter:

http://www.memcon.com/pdfs/proceedings2014/NET104.pdf

Auf Seite 23 wird das

Pseudo Channel Konzept vorgestellt und auf Seite 24 ist es grafisch dargestellt

->Das was auf Seite 24 als

Legacy Mode beschrieben ist, ist genau das was Nai die ganze Zeit erklärt (auch wenn er Interleaving falsch definiert, was aber keine Rolle spielt bei dieser Argumentation.)

Das was unter

Pseudo-Channel Mode steht ist der Ersatz für Interleaving im Legacy Mode. Dies stellt einen Channel dar.

Hier eine Darstellung des selben Sachverhalts über alle Channels verteilt ("Bank n" bedeutet eine beliebige Anzahl von Bänken die sich alle ebenso unabhängig verhalten) - die Folie sollte auch schon bekannt sein aus dieser Diskussion hier im Thread:

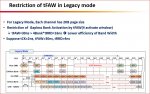

Weiterführend wird auf der Seite 25 das Limit für Interleaving im "Legacy Mode" nochmals aufgezeigt

Restriction of Gapless Bank Activation by tFAW(4 activate window)

=> tFAW=30ns > 4Bank*tRRD=16ns

=>Lower efficiency of Band Width

Man sieht sehr gut wie Interleaving nach wie vor nicht die Lücken vollständig schließen kann um die Effizienz zu verbessern. Daher geht HBM einen Schritt weiter OHNE klassisches Interleaving nutzen zu müssen. Die Effizienz wird über die Pseudochannels ebenso erreicht wie bei Interleaving, mit dem Unterschied dass es nach 4 "windows" eben keine "Gap" (Lücke) gibt

Anders hier bei HBM, die Aufgrund des Pseudo-Channels keine Lücken mehr haben nach 4 "windows" sondern eine Vollständige lückenlose Auslastung des DRAMs:

Aus diesem völlig anderen Aufbau des Speichersubsystems ergibt sich folgende Zusammenfassung meiner Ausführung:

Das Feature des Single Bank Refresh ist die Zentrale Änderung die HBM einige Eigenschaften verleihen die bisher nciht möglich waren. es basiert darauf, dass HBM deutlich mehr I/O Pins zur Verfügung hat (auch das steht am Anfang in beiden Quellen) und diese wiederum exklusiv für den Row oder Column Zugriff genutzt werden können (Auch das steht in selbigen beiden Quellen).

Und nun muss man noch als zusätzliche Information zufügen, dass der Speichercontroller für HBM auf dem Speicher selber sitzt und nicht in der CPU oder GPU wie man das bisher gewohnt war. Auf diese Weise ist die drastische Reduzierung des Speicherinterfaces möglich.

http://en.wikipedia.org/wiki/High_Bandwidth_Memory

High Bandwidth Memory combines through-silicon vias (TSV) and microbumps to connect multiple (currently 4 to 8) dies of memory cell arrays on top of each other. The memory controller is contained on a separate die at the very bottom of the stack.

Und nein das hier habe nicht ich bei Wikipedia eingetragen:

The HBM DRAM is tightly coupled to the host compute die with a distributed interface. The interface is divided into independent channels. Each channel is completely independent of one another. Channels are not necessarily synchronous to each other. The HBM DRAM uses a wide-interface architecture to achieve high-speed, low-power operation. The HBM DRAM uses differential clock CK_t/CK_c. Commands are registered at the rising edge of CK_t, CK_c. Each channel interface maintains a 128 bit data bus operating at DDR data rates.

Da ich allerdings hier erlebt habe wie sogar seriöse technische Quellen schlecht geredet wurden habe ich das ganze etwas mehr ausgeführt. Der Fakt bleibt bestehen, dass bei HBM die Speicherbausteine je 128-bit Channel unterschiedlich konfigurierbar sind, was deren Verarbeitungsgeschwindigkeit betrifft. Dies ergibt noch weitere Eigenschaften, die ich jetzt aber nicht auch noch hier einbringen will, da es schon so recht komplex ist. Ich führe es gerne weiter aus wenn wir uns auf diese Basis einigen können.

Sorry für den langen post, doch es sind nun mal grundlegende Dinge die aufeinander aufbauen und Abhängigkeiten schaffen. Gerne lass ich mir von jemandem einen logischen Fehler in den Ausführungen zeigen, doch bitte dann auch mit einer Quelle die belastbar ist und auch das enthält was ausgeführt wird.

Aber sicher cool für FHD-Nutzer, da wirds gut gehen und viel bringen.

Aber sicher cool für FHD-Nutzer, da wirds gut gehen und viel bringen.