Einhörnchen schrieb:

Offenbar gehörst du zu den wenigen, die Einblick in die Verträge zwischen TSMC und AMD/Nvidia haben. Es gibt übrigens spannende Diskussionen, wieso die Verbesserung der Yield-Rate bevor Nvidia in den Massenproduktion ging so schleppend war, wieso in DX11 nicht dokumentierte Features sind, die Fermi verwendet und wie interessiert TSMC daran ist, dass NV nicht auch zu GF geht.

zum thema kosten: ist ganz einfach zu sehen dass bei grösseren chips die kosten mehr als linear ansteigen.

der lineare teil ist glaub ich jeden mal klar, wir haben einen waver mit der fläche A, daraus würden sich wenn optimale aufteilung möglich wäre x=A/b chips mit der fläche b ausgehen.

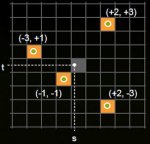

der erste nachteil grosser chips kommt dazu wenn man bedenkt dass ein waver rund ist, dadurch entsteht natürlich verschnitt am rand. dieser verschnitt steigt mit der grösse der chips an. das ist ganz einfach nachzuvollziehen, zeichne einen kreis und versuch möglichst viele ganze rechtecke reinzubekommen, bei grösseren rechtecken entsteht viel mehr ungenützte fläche

der nächste punkt sind fertigungsfehler die pro waver auftreten. die entstehen durch verschiedenste gründe, zb durch unreinheiten des wavers, unregelmässigkeiten beim beschichten/ätzen, probleme in der lithographie... wie genau ist für die behandlung der kosten aber eigentlich nicht relevant, es reicht zu wissen dass die anzahl der fehler pro waver sowie die positioninen statistisch verteilt sind.

gehen wir von zwei unterschiedliche chips aus von chip a gehen sich 100 auf den waver aus vom chip b 150. jetzt nehmen wir den simpelsten fall an dass auf beiden wavern 10 fehler sind die gleichmässig über die fläche verteilt sind und alle fehler so schlimm sind dass der chip der getroffen wird nicht funktionsfähig ist. damit sind dann von typ a 90/100 chips funktionstüchtig (90% yield), während bei chip b 140/150 chips funktionstüchtig sind (93,3%) yield. bei 20 fehlern pro waver ergibt die selbe rechnung 80% für a und ~87% für b, das zeigt dass mit steigender anzahl der fehler die yields immer weiter auseinander driften. (das ist nur ein simples modell, in realität gibt es ja uach die möglichkeit dass der selbe chip von mehreren fehlerstellen betroffen ist was mit ansteigender fehlerstellenanzahl immer warscheinlicher wird, die die drift etwas abschwächt da die warscheinlichkeit dafür bei grösseren chips schnelelr ansteigt)

zusammenfassend hat der grosse chip zu dem nachteil dass sich schon linear gerechnet weniger pro waver ausgehen die nachteile dass bei ihnen mehr verschnitt entsteht, und sie bei fehlern stärker betroffen sind. was dazu führt dass kosten pro chip weitaus stärker von der fläche abhängig sind als man zuerst annimmt.

um die exakten kosten zu kennen, müsste man wissen wie teuer ein waver der jeweiligen chips in 40nm ist. die kosten pro waver sind aber kein allgemeines fixum sondern hängen von der technik und auch der anzahl der bearbeitungsschritte ab.ich gehe davon aus dass aber beide high end graphik chips vergleichbar teure waver haben, wäre was anderes wenn du hier einen graphik chip und einen eher simplem chip wie ein ram modul vergleichen würdest.

ein in 40nm technik bearbeiteter waver ist dabei wesentlich teurer als zb. ein alter in 90nm gefertigter waver, aber da die kosten nicht in dem masse steigen wie die anzahl der zusätzlich erzielten chips bei ienem shrink ist ein shrink in den meisten fällen sinnvoll. hab irgendwo gelesen dass die kosten pro waver momentan im bereich von einigen tausend $ sind (glaub noch <10000$).