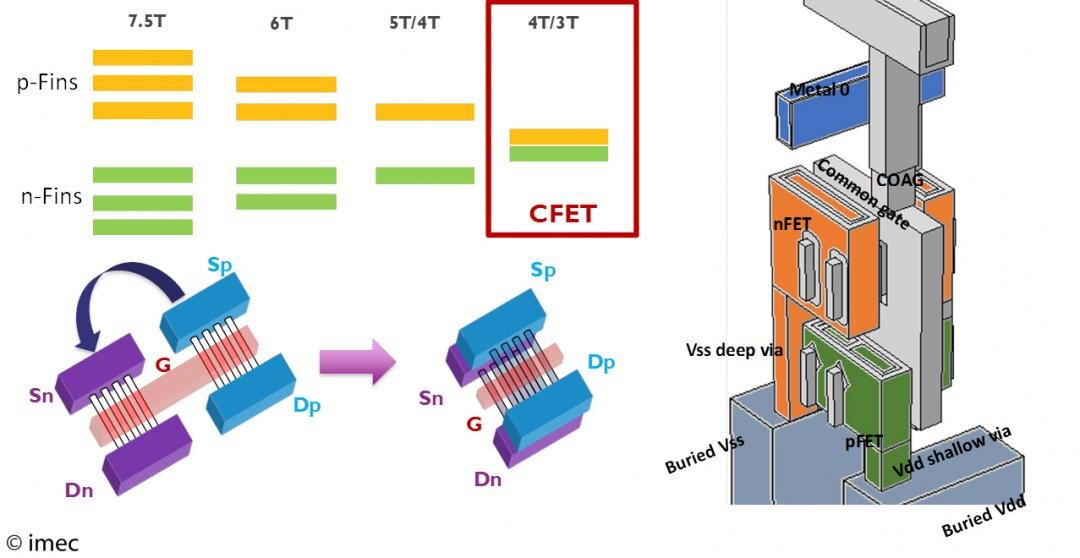

@Forum-Fraggle Doch, das ist schon richtiges 3D-Stacking. Aber die Bezeichnung ist etwas anderes als 3D-Schaltpläne, da hast du schon recht. Soweit ich weiß, gibt es keinerlei Pläne oder Forschung für 3D-Schaltpläne, weil das einfach mit den aktuellen Verfahren in der Lithographie gar nicht durchsetzbar wäre. Schau dir mal in der Grafik rechts an, was da für 3D-Aufbauten notwendig sind, um nur einen 2D-Schaltplan sauber miniaturisiert zu bekommen:

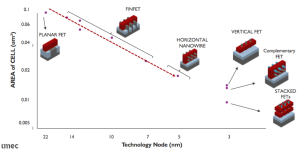

Die existierenden 3D-Verfahren sind einmal das Gate-All-Around, das ermöglicht, einen Transistor dreidimensional Aufzubauen. Da wird das Gate von allen Seiten umschlossen, anders als beim FinFET, der deswegen nur als 2.5D gilt.

Und dann gibt es noch das Stacking von Chips auf Chips. Da galt die Integration von HBM und Prozessor-Chip auf einem Interposer als 2.5D, weil es zwei verscheidene Chip-Typen waren, die aufeinander gestapelt wurden. AMDs 3D-Stacking ist dann richtiges 3D, weil zwei Logik-Chips in moderner Fertigung aufeinander gestapelt werden. Die Leitungen verlaufen in dem Fall auch teilweise dreidimensional und man bekommt einen Stapel aus Schaltkreisen auf Schaltkreisen. Also man bekommt genug 3D.

Die existierenden 3D-Verfahren sind einmal das Gate-All-Around, das ermöglicht, einen Transistor dreidimensional Aufzubauen. Da wird das Gate von allen Seiten umschlossen, anders als beim FinFET, der deswegen nur als 2.5D gilt.

Und dann gibt es noch das Stacking von Chips auf Chips. Da galt die Integration von HBM und Prozessor-Chip auf einem Interposer als 2.5D, weil es zwei verscheidene Chip-Typen waren, die aufeinander gestapelt wurden. AMDs 3D-Stacking ist dann richtiges 3D, weil zwei Logik-Chips in moderner Fertigung aufeinander gestapelt werden. Die Leitungen verlaufen in dem Fall auch teilweise dreidimensional und man bekommt einen Stapel aus Schaltkreisen auf Schaltkreisen. Also man bekommt genug 3D.