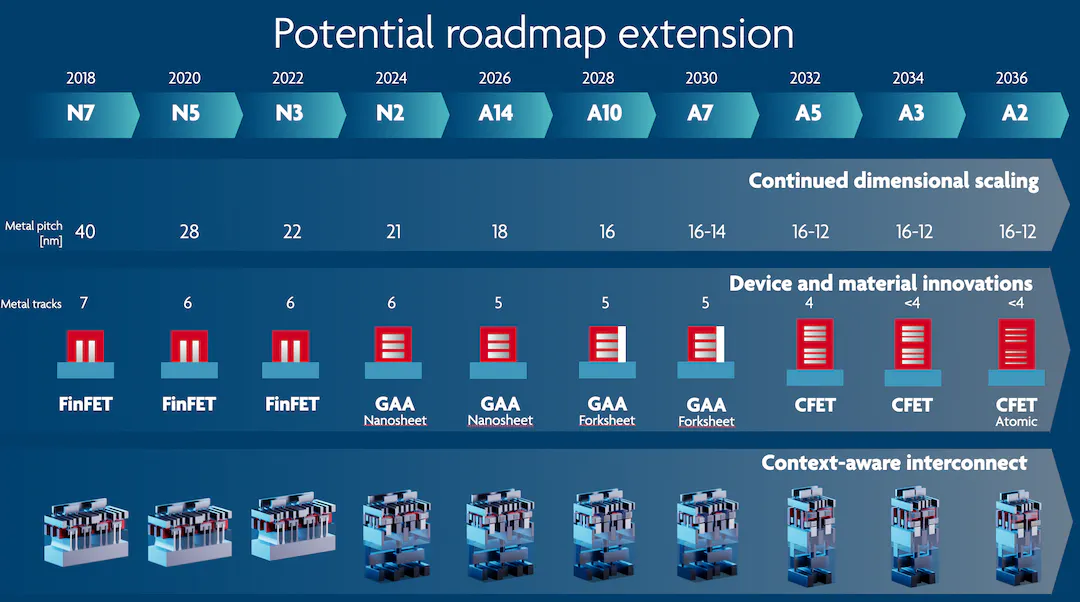

Wenn man sich anschaut wie es weitergehen soll, geht es nicht in erster Linie um kleinere Strukturen, sondern, um einen komplexeren Aufbau der Transistoren.

Der Skalierungseffekt von CFET liegt, darin dass man 2 Transistoren übereinander stapelt. Dafür muss der Metall-Pitch nicht unbedingt verkleinert werden.

Eine weitere durchgreifende Änderung wird Backside Power Delivery bringen. Die Datenleitungen bleiben auf der Frontside während das Power Delivery Network auf die bisher vollkommen ungenutzte Backside wandert. Einer von vielen Vorteilen ist, dass für die Kontakte mehr Platz zur Verfügung steht. Man muss den Metall-Pitch nicht mehr im selben Maß verkleinern.

Und das sieht man auf der Potential Roadmap Extension von IMEC ziemlich deutlich. Es kursieren unterschiedliche Varianten dieser Roadmap mit variierenden Angaben zum Metall-Pitch.

Allen Varianten der Potential Roadmap Extension, die ich gesehen habe, ist gemeinsam, dass der Metal Pitch von A14 mit 18 nm angeben ist.

TSMC hat vor zwei Jahren Kontaktstrukturen mit einem Pitch von 18 nm demonstriert.

Das könnte bedeuten, dass TSMC A14 ohne High-NA hinbekommt. Und mehr Zeit zu haben eine komplexe neuen Maschinerie kennen zu lernen bevor man sie tatsächlich einsetzen muss, ist jetzt auch nicht schlecht.

Zum Thema Intel 10 nm und EUV. Intel 7 verwendet kein EUV, also kann das Fehlen von EUV nicht der Grund sein.

Ich sehe bei Intel 10 nm das eigentliche Problem nicht darin, dass Intel sich beim ersten Wurf zu viel vorgenommen hat. Was ich nicht nachvollziehen kann, dass Intel so viele Versuche gebraucht hat um das Problem zu beheben.

Noch eine Anmerkung zu ASML. Mit den EUV-Lithografiesystemen von ASML alleine wird eine Halbleiterfertigung nicht funktionieren.

Der Skalierungseffekt von CFET liegt, darin dass man 2 Transistoren übereinander stapelt. Dafür muss der Metall-Pitch nicht unbedingt verkleinert werden.

Eine weitere durchgreifende Änderung wird Backside Power Delivery bringen. Die Datenleitungen bleiben auf der Frontside während das Power Delivery Network auf die bisher vollkommen ungenutzte Backside wandert. Einer von vielen Vorteilen ist, dass für die Kontakte mehr Platz zur Verfügung steht. Man muss den Metall-Pitch nicht mehr im selben Maß verkleinern.

Und das sieht man auf der Potential Roadmap Extension von IMEC ziemlich deutlich. Es kursieren unterschiedliche Varianten dieser Roadmap mit variierenden Angaben zum Metall-Pitch.

Allen Varianten der Potential Roadmap Extension, die ich gesehen habe, ist gemeinsam, dass der Metal Pitch von A14 mit 18 nm angeben ist.

TSMC hat vor zwei Jahren Kontaktstrukturen mit einem Pitch von 18 nm demonstriert.

Das könnte bedeuten, dass TSMC A14 ohne High-NA hinbekommt. Und mehr Zeit zu haben eine komplexe neuen Maschinerie kennen zu lernen bevor man sie tatsächlich einsetzen muss, ist jetzt auch nicht schlecht.

Zum Thema Intel 10 nm und EUV. Intel 7 verwendet kein EUV, also kann das Fehlen von EUV nicht der Grund sein.

Ich sehe bei Intel 10 nm das eigentliche Problem nicht darin, dass Intel sich beim ersten Wurf zu viel vorgenommen hat. Was ich nicht nachvollziehen kann, dass Intel so viele Versuche gebraucht hat um das Problem zu beheben.

Noch eine Anmerkung zu ASML. Mit den EUV-Lithografiesystemen von ASML alleine wird eine Halbleiterfertigung nicht funktionieren.