TechFA

Lieutenant

- Registriert

- Okt. 2018

- Beiträge

- 777

Korrekt, ja.Convert schrieb:Wenn man mit EUVL wie TSMC so viel Erfahrung hat, dann ist EUVL double-patterning günstiger.

TSMC wird so oder so allein durch ihren Expertisen-Vorsprung selbst noch auf Low-NA und mit Double-Patterning günstiger als Intel produzieren können. Das wird dann Intel mit High-NA und bloß Single-Patterning kontern wollen, was dann wiederum wird massiv in die Hose gehen …Convert schrieb:Wen man wie Intel nicht so viel Erfahrung hat und Double-Patterning mit EUVL nicht zuverlässig hinbekommt und der Ausschuss deswegen steigt …

Das ist dann Intel's finanzielle Selbst-Strangulierung.

Nein. So oder so wird Intel bei dem Thema EUVL keinesfalls günstiger als TSMC produzieren können, dafür ist der Vorsprung an Erfahrung von TSMC und Anderen gegenüber Intel schon seit Jahren viel zu groß.Convert schrieb:… dann kann für Intel High-NA Single-Patterning gar günstiger sein.

High-NA mit Single-Patterning ist schon in der Theorie kostspieliger als Low-NA selbst mit Double-Patterning!

Zudem hat TSMC und Andere in diesem Falle trotz Double-Patterning keinen Malus von kleineren Die-Größen, unter dem Intel dann noch immer stünde. Kennst Du den Artikel?

Genau … Weil ja auch Niemand von uns mit ansehen konnte wie es Intel bei der Integration von Experimental-Techniken (aka "First to market") die letzte Dekade hat immer wieder prominent vergeigt.Convert schrieb:Intel spricht öffentlich darüber, dass die Maske 6x12 sein kann, so dass Stitching eingespart werden kann:

Es hat schon einen Grund, weswegen Intel ihre (Foundry-) Profitabilität über Monate und mittlerweile Jahre sukzessiv nach unten korrigierte und um 2020 noch von 2024, dann 2025 oder 2027 und jetzt 2030 spricht.

Da hast Du natürlich Recht. Mein Fehler!Convert schrieb:RX 6900 hatte noch ein Chip mit 519 mm² in N7P-Prozess (DUV). Die RX 7900XTX hat keinen Chip mit 529 mm². Der größte Chip der 7900XTX ist dank Chiplets 300mm² in 5nm (EUV). Die RX 9070 (XT) auf Navi48-Basis wird mit ~350-380mm² (4nm) spekuliert, ähnlich zu der noch halbwegs bezahlbaren (UVP) RTX 5080/RTX4080. Also alles unterhalb der von dir genannten 429mm² im EUV-Prozess.

Ich hatte bei der bekannt-großen Nvidia RTX 5090 (750 mm²) einfach analog dazu nach einem entsprechend großen Pendant im AMD-Lager gesucht und dann die RX 7900XTX per schneller Google-Suche als Beispiel genommen, was nur die Gesamtsumme aller Dies wäre.

Ich hab' auch nicht alle Spezifikationen im Kopf, und hatte keine Ahnung über das MCP der RX 7900 und die jeweiligen zusätzlichen Chiplets des Infinity Cache. War also keine Absicht in dem Sinne, da ich lediglich bloß exemplarisch unterstreichen wollte, daß High-NA zwar einen höheren Wafer-Durchsatz hat, allerdings dafür mit kleinerem Rektil daherkommt kommt.

Laut TechPowerUp's GPU-Datenbank hat AMD's RX 7900XTX natürlich tatsächlich einen deutlich kleineren Die von bloß 304,35 mm² für den eigentlichen GPU-Kern, die verbleibende Fläche entfällt richtigerweise auf die Chiplets des Infinity Cache in den sechs MCD-Chips.

Intel nutzt keine Chiplets, sondern ihre Tiles. Da gibt es zwischen den beiden teils gravierende Unterschiede!Convert schrieb:Intel nutzt schon jetzt Chiplets bei ihren Server-CPUs mit Intel 3 Fertigung und auch bei ihren Arrow Lakes in TSMC 3nm Fertigung nutzt Intel auch Chiplets. Wo wäre da für Intel jetzt ein Verlust, wenn die eh schon auf Chiplets umgestiegen sind?

Im Übrigen sprach ich nicht generell über Intel, sondern grundsätzlich über die zukünftige Beschränkung der Größe des Die, welche in aller Zukunft bestenfalls gleich bleiben dürfte. Erst recht bei irgendwas High-NA.

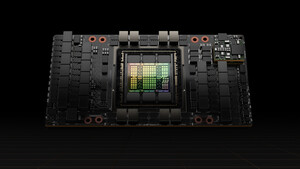

Ging eher Richtung GPU, wo ja Nvidia seit Jahren mit riesigen Dies vorprescht …