R

RogueSix

Gast

@Sherman789

Wo hat denn Intel Vorsprung? Sie mussten gerade erst mit eingezogenem Schwanz eingestehen, dass sie Lunar und Arrow Lake komplett bei TSMC fertigen lassen müssen, weil ihre eigenen Herstellungsprozesse für keine tile etwas taugen.

Bei Raptor Lake haben sie zwei Jahre und zwei Generationen am Stück degradierenden Schrott produziert.

Dazu der davon unabhängige "oxidation issue" bei -angeblich- nur einigen frühen Chargen. Intel hat aber vorsichtshalber mal keine Chargen-/Batchnummern von oxidierten CPUs veröffentlicht (vielleicht weil es doch ein viel größeres Problem war/ist?).

Dann das vernichtende Urteil von Broadcom letzte Woche, die Intel zu verstehen gegeben haben, dass ihr "Heilsbringerprozess" (laut Gelsinger) 18A niemals im Zeitplan HVM-ready sein wird.

Den 20A Prozess musste man gar komplett einstampfen, weil da wohl nur Abfall bei produziert wurde. Ursprünglich sollte der Prozess mal eine wichtige Brücke auf dem Weg zu 18A darstellen. Jetzt werden alle Tiles von Lunar und Arrow Lake komplett bei TSMC gefertigt, weil man 20A nicht geschissen bekommen hat.

Last but most definitely not least: 20A sollte auch BSP und GAA bei Intel einführen. Mal wieder ein Satz mit "x".

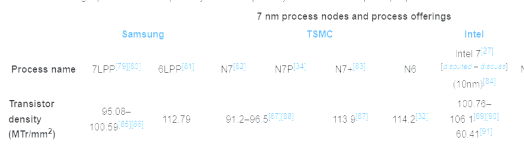

Ergo: Nur Katastrophennachrichten und ein Versagen nach dem anderen in Intels Fertigungssparte. Die Tatsache, dass sie High-NA Systeme vor TSMC bestellt und geliefert bekommen haben, bedeutet doch keinen Vorsprung. Haben die die Kisten überhaupt schon ausgepackt und aufgestellt, geschweige denn den "on" Knopf gefunden?

Ein Vorsprung wäre oder wird dann gegeben sein, wenn Intel tatsächlich irgendwann mal funktionierende Chips bei vergleichbaren geringen Defektraten (yields) wie TSMC produzieren können, die in Performance und Effizienz vor ihren TSMC Pendants liegen. Davon sind wir zum jetzigen Stand weiter entfernt als jemals zuvor seit die Probleme mit 10nm vor inzwischen gut 8(!) Jahren Intel die Führung gekostet haben...

Wo hat denn Intel Vorsprung? Sie mussten gerade erst mit eingezogenem Schwanz eingestehen, dass sie Lunar und Arrow Lake komplett bei TSMC fertigen lassen müssen, weil ihre eigenen Herstellungsprozesse für keine tile etwas taugen.

Bei Raptor Lake haben sie zwei Jahre und zwei Generationen am Stück degradierenden Schrott produziert.

Dazu der davon unabhängige "oxidation issue" bei -angeblich- nur einigen frühen Chargen. Intel hat aber vorsichtshalber mal keine Chargen-/Batchnummern von oxidierten CPUs veröffentlicht (vielleicht weil es doch ein viel größeres Problem war/ist?).

Dann das vernichtende Urteil von Broadcom letzte Woche, die Intel zu verstehen gegeben haben, dass ihr "Heilsbringerprozess" (laut Gelsinger) 18A niemals im Zeitplan HVM-ready sein wird.

Den 20A Prozess musste man gar komplett einstampfen, weil da wohl nur Abfall bei produziert wurde. Ursprünglich sollte der Prozess mal eine wichtige Brücke auf dem Weg zu 18A darstellen. Jetzt werden alle Tiles von Lunar und Arrow Lake komplett bei TSMC gefertigt, weil man 20A nicht geschissen bekommen hat.

Last but most definitely not least: 20A sollte auch BSP und GAA bei Intel einführen. Mal wieder ein Satz mit "x".

Ergo: Nur Katastrophennachrichten und ein Versagen nach dem anderen in Intels Fertigungssparte. Die Tatsache, dass sie High-NA Systeme vor TSMC bestellt und geliefert bekommen haben, bedeutet doch keinen Vorsprung. Haben die die Kisten überhaupt schon ausgepackt und aufgestellt, geschweige denn den "on" Knopf gefunden?

Ein Vorsprung wäre oder wird dann gegeben sein, wenn Intel tatsächlich irgendwann mal funktionierende Chips bei vergleichbaren geringen Defektraten (yields) wie TSMC produzieren können, die in Performance und Effizienz vor ihren TSMC Pendants liegen. Davon sind wir zum jetzigen Stand weiter entfernt als jemals zuvor seit die Probleme mit 10nm vor inzwischen gut 8(!) Jahren Intel die Führung gekostet haben...