Wow wie negativ die Kommentare hier direkt wieder sind. Von Null Innovation würde ich hier nicht sprechen. Selbst das mittlere Schaubild besteht schon aus mehr Komponenten als die AMD Produkte, die ja bis jetzt nur aus 2 verschiedenen Chiplets pro Produkt bestehen.

Und rechts wird es dann ganz interessant: Ich verstehe das ja mal so, dass man die einzelnen Einheiten noch viel wieder "zerhackt", als man es bis jetzt kennt. Bei AMD hat die MI200 Reihe 2 Grafik Dies, die aber ja beide noch relativ groß sind. Auch Navi 31 wird wohl nur ein oder maximal 2 GCDs für über 12k Shader bekommen.

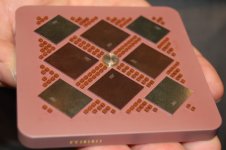

Diese Grafik hier legt her nahe, dass man zum Beispiel auf 128 oder 256 Shader pro Mini Die geht, was noch mal ganz andere Möglichkeiten gibt. Zum einen hat man natürlich Yields nahe 100% und zum anderen nutzt man auch nur dass, was das Produkt nachher auch bietet.

32EU Grafik? 2 Mini Dies. 64EU Grafik? 4 Mini Dies usw. Immer wird alles maximal genutzt, die geringe Größe sorgt dafür, dass es kaum Defekte gibt und somit wird fast nichts teildeaktiviertes verwendet.

@konkretor deine PDF handelt von Ponte Vecchio, das hat eher weniger hier mit zu tun. Ist ja auch schon älter, vom Vision Event von 2 Wochen. Hier im Artikel ist ja eben erst das NDA gefallen.

Edit: Und der "On Package Memory" in der Base Tile auf der ersten Folie confirmed wohl Intels eigenen 3D Cache.