@Ned Flanders und alle anderen die im 4-Modul-BD immer noch einen 4-Kern Prozessor sehen:

Ich habe ja ein paar Seiten vorher schon Folgendes geschrieben:

Weil hier immer noch und immer wieder die Diskussion über die Kernanzahl eines 4-Modul Bulldozers auftaucht:

Ein Modul enthält definitiv 2 tatsächliche Kerne. Jedem Kern stehen eigene Integer und bei Bedarf Floatingpoint-Ausführungseinheiten zur Verfügung. Dass heißt alle Kerne können jeweils einen Thread GLEICHZEITIG abarbeiten. Gleichzeitig heißt in ein und dem selben Takzyklus und das ist bekanntlich bei Intels HT nicht der Fall. Daran mache ich den Unterschied fest ob es sich um echte oder virtuelle Kerne handelt.

Dies gilt bei BD sowohl für Integer- als auch für bis zu 128Bit breite Floatingpoint-Instruktionen. Einzig für 256Bit breite AVX Befehle müssen sich die beiden Kerne eines Moduls die FPU teilen und evtl. der eine Thread auf den anderen warten.

Zusätzlich gibt es noch noch die (ebenfalls legitime) historische Betrachtungsweise, nachdem jede Integereinheit einen eigenen Core darstellt.

Wenn ihr BD als 4-Kern Prozessor einstuft, dann aufgrund der Tatsache, dass manche Ressourcen (256Bit AVX und L2) von den 2 Kernen eines Moduls geteilt werden. Würde man diesen Denkansatz konsequent weiterverfolgen, gäbe es im Grunde genommen überhaupt keine Mehrkernprozessoren. Jeder Sandy Bridge wäre ein Singlecore weil sich die Kerne den Speichercontroller teilen. Ein Core2Duo wäre ebenfalls ein Singlecore weil sich die Kerne den FSB teilen. Und es gibt ja bekanntlich Fälle wo ein Kern warten muss, weil ein anderer gerade massive Speichertransfers ausführt.

Also wo zieht ihr da eine logische und vernünftige Grenze? Die einzige Definition, die einen Sinn ergibt, ist die mögliche Anzahl der gleichzeitig, auf Taktebene ausführbaren Threads, entweder unter maximalen Gesichtspunkten (maximal gleichzeitig mögliche Threads) oder unter Berücksichtgung des typischen Workloads. Der typische Workload ist selbstverständlich ein sehr weit gefasster Begriff und unterliegt dem zeitlichen Wandel. Heutzutage ist es sinnvoll, Integer- und bis zu 128Bit breite Floating-Point-Instruktionen als typisch anzusehen. 258Bit AVX hat hierfür noch keine Relevanz, das mag sich aber in Zukunft ändern. Also muss man BD aus heutiger Sicht als 8-Kern Prozessor einstufen.

Oder man betrachtet es eben historisch: Zu Prozessor-Urzeiten bestand der typische Workload aus 100% Integerinstruktionen, BD hat 8 eigenständige Integer-Einheiten, kann mit jedem Takt 8 Instruktionen unabhängig und gleichzeitig bearbeiten und hat somit 8 Kerne.

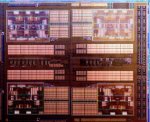

Ich bin gespannt, wer eine LOGISCHE Begründung liefert, warum BD als 4-Kerner einzustufen sei. Und dafür kann mit Sicherheit nicht die räumliche Aufteilung einzelner Einheiten auf dem DIE herhalten. Menschen können auch zu ein und derselben Familie gehören, ohne dass sie zwingend gemeinsam in einem Haus leben müssen.

Es geht mir übrigens nicht darum einfach nur Recht zu haben, ich finde es nur wichtig diesen Punkt richtig zu stellen. Wenigstens hier im Forum sollte darüber Klarheit herrschen.

Leute die sich informieren möchten, sollten hier schon richtige Tatsachen zu lesen bekommen

Beste Grüsse