Krautmaster schrieb:

@ Aylano

Das war vielleicht noch der Fall als die Fertigungskosten vergleichsweise klein waren, aber die neuen Prozesse scheinen deutlich teurer zu werden und das spürt man bei Nvidia mit GK110 genauso wie bei AMD, oder hat man da je so spät noch einen Chip in "alter" Fertigung gebracht?

Ohne Zahlen dazu scheint es immer so zu sein.

Überlege einmal, warum Intel jetzt Atom und Larrabee davor so schnell wie möglich auf 22nm brachten, nachdem sie in alter 40nm & 32nm-Fertigung beide glänzlich versagten.

Bei 300mm-Wafer @ 20nm würde AMD bei 350 vielleicht so 180 Stück rausschneiden können. Bei einer Yield von 10% (wobei man da nichteinmal volle nehmen müsste, sondern 4 oder 8-Deaktivierte CU), könnte man immer noch 18 Stück rausholen.

Mit diesen 18 Stück könnte man immer noch Treiber-Optimierungen machen und andererseits um je 3000 Euro @ FirePro-Markt verkaufen.

Damit könnte man die jetzt angeblichen 20.000 Euro Wafer locker bezahlen.

Ich weiß nicht, warum du so viel redest, aber deine Aussagen sind völlig informationslos.

G80 wurde übrigens 6 Monate vor 65nm-Mainstream & Low-End rausgebracht.

Krautmaster schrieb:

Beide Seiten ziehen ihre Chips absichtlich nach hinten raus da von rentabler Fertigung zu Rentabler Fertigung in kleinerer Größe immer mehr Zeit vergeht.

Das ist wieder nur irgendeine Aussage, die du nur empfindest, aber nicht mit Zahlen belegst.

Krautmaster schrieb:

Wenn der Chip auf GCN 2.0 setzt und vielleicht mit weitreichenderen Änderungen daherkommt, dann ist dieser sicher auch schon ne ganze Zeit lang fertig.

Aha, je weitreidender die Änderungen, desto länger muss er fertig sein?!! Interessant.

Krautmaster schrieb:

AMD kappt sich ganz schön viel Ressourcen von TSMC ab, man denke da an die Kabinis/ Temash, Brazos, dann der riesige Konsolendeal. Ich weiß nicht wie es da um AMD steht, meinst du die können unbegrenzt Fertigungskapazitäten bei TSMC?

Wie wäre es, wenn du selber mal nachschaust, anstatt mich einerseits die Welt erklären und gleichzeitig mich nach Informationen nach mir fragst, mit denen du mir die Welt erklärst. Offensichtich weißt du nicht, wie groß TSMC bzw. die Fabriken & Fertigungen sind, weil du dann so eine Aussage nicht gemacht hättest.

Thanok schrieb:

Mensch ihr beide liefert eine Tolle Show ab!

Das ist keine Snow.

Meinungsfreiheit heißt ja, dass auch völlig Unwissende Leute was sagen & meinen dürfen, so ost sie wollen.

Ich werde mich mal nicht groß einmischen da mich die Feinheiten der Architekturen eher wenig interessieren (bzw. ich mein Wissen sich auf "Gibt's halt" beschränkt). Allerdings...

Es darf sind jeder einmischen, aber wer halbwegs Bildung oder konkrete Ausbildung dazu oder keine Einbildung hat, weiß die Art wie man sich richtig einmischt.

Thanok schrieb:

Auf der anderen Seite sind Architekturänderungen, zumindest größere, immer mit einem gewissen Entwicklungsaufwand verbunden. Daher wird bei einem Refresh idR die gleiche Architektur verwendet und nur in einzelnen Punkten optimiert.

Natürlich, aber ob wirklich mehr Entwickleraufwand betrieben wurde, sieht man an der Ahnzahl der Leute. Wir können das nur über das Geschäftsbericht lesen. Nicht zu vergessen ist, dass sich die Entwicklungsgschwindigkeit pro Person auch in den letzten Jahren verändert hat.

Thanok schrieb:

Und auch bei einer Architekturänderung sind die Unterschiede nicht immer sonderlich groß. Kepler ist in vielen Punkten mit Fermi identisch, Maxwell wird auch keine neue Architektur bringen. Der größte Architektursprung der letzten Zeit war da Fermi, und darauf basieren eben jetzt erstmal die nächsten Generationen.

Neue Architekturen sind es zwar trotzdem, die Basis ist aber eben "alt".

So gesehen ist jede GPU-& CPU-Generation von AMD & Nvidia & Intel eine Weiterentwicklung, die Fälschlicherweise Neuentwicklung genannt wurde. So wie Core eine Weiterentwicklung vom Pentium III ist, der eine Weiterentwicklung von P54 ist, vondem aus Larrabee (mit riesen Vektorblock) sowie Atom und mittlerweile Quark weiterentwickelt wurde.

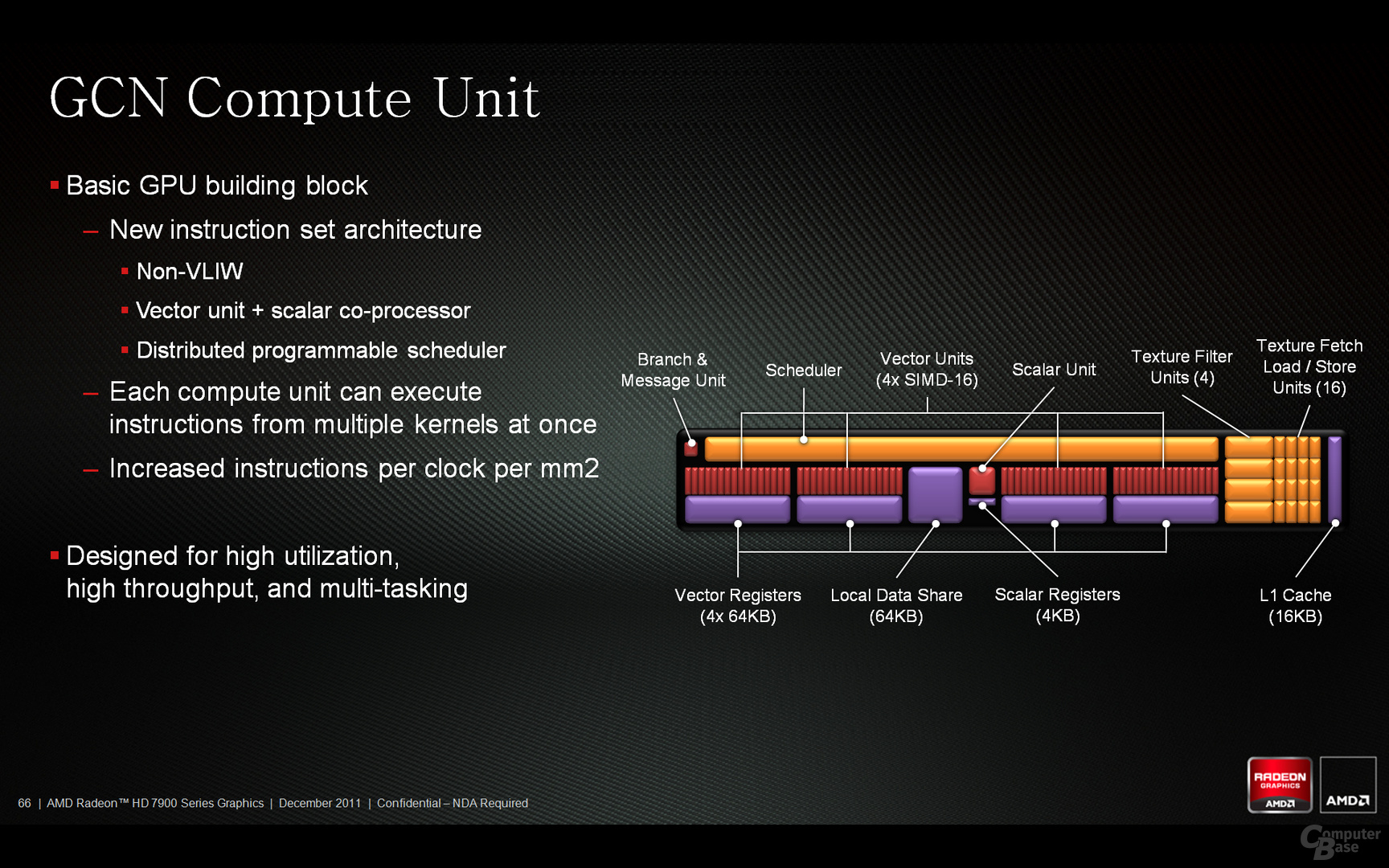

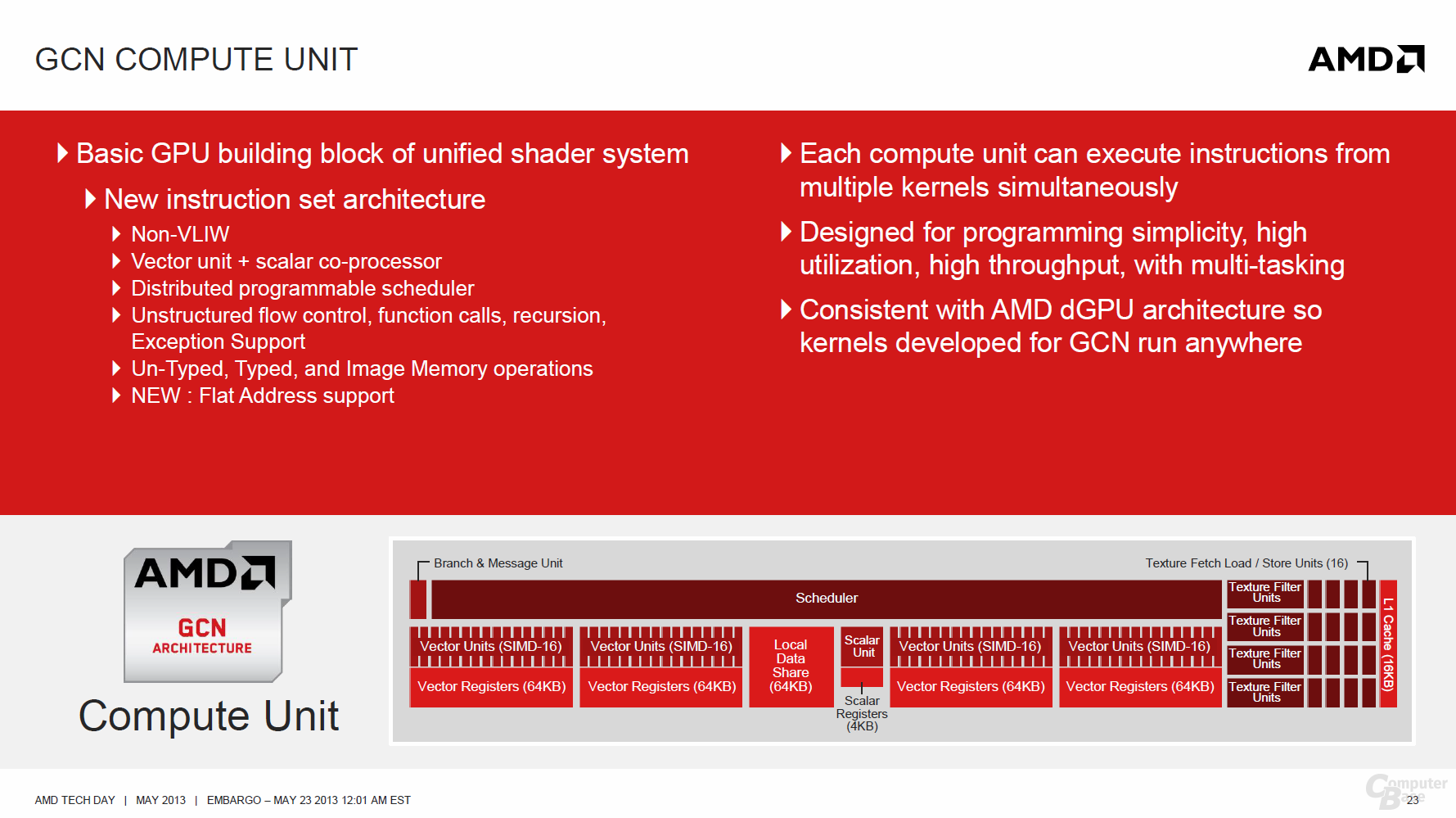

Bei GCN wurde auch nur das Front-End des CUs erneuert, während der Rest (Grafik-Engines & Co) ziemlich gleich bliebt bzw. auf DX11 angepasst wurde.

AMD hat 2 Architekur Teams.

Einer Entwickelt die Architektur im Groben weiter (DX10 --> DX11 --> GCN) und die andere kümmert sich mal um die Shader & Co einheiten oder Front-End oder VLIW-5 --> WLIW-4 Umstieg.

Hawaii müsste wieder ein Ergebnis von dem Team sein, dass die Architektur in den letzten mindestens 6 Jahren im Groben ändert.

Ich vermag mich zu irren (siehe meine Untkenntnis), aber vor GCN hat AMD doch noch auf VILW-4/5 gesetzt welches eine sehr hohe Dichte der Shader ermöglichte UND vor allem die Shader nicht vollständig auslasten konnte. Du bringst das Beispiel mit den 10% von VILW-5 auf 4 ja selbst. Genau dass war ja auch der Grund weswegen AMD vom VILW-5 Design weggegangen ist.

Richtig, deshalb haben sie ein Front-End @ CU eingebaut.

Nur damit du es weißt. Im CU gibts auch 4 SIMD mit 16 Shaders, wobei die anders sind als die alten SIMD, weil sie 16 VILW-4/5 besitzen.

Bitte kläre mich bekennenden Laien mal auf was da DER große Unterschied sein soll. Für mich klingt GCN 2.0 nach GCN 1.0 mit einigen Änderungen aber im Grunde gleicher Architektur.

Erklären kann ich es nichts, weil ich keine konkreten Infos dazu habe, aber spekulieren.

Ich hätte für GCN 1.1 schon 4 Rasterizer spekuliert.

Ein Indiz könnte die 4 ACE @ Kabini (GCN 1.1) sein, weil GCN 1.0 mit 2 ACE immer 2 Rasterizer hatte. Den Zusammenhang kann ich nicht eklären.

Weil wieder eine grobe Weiterentwicklung ansteht, halte ich bei GCN 2.0 256-Shaders für möglich, wobei es nicht das erste mal war, dass Gerüchte die übernächste Generation betreffend. Bestes beispiel sind GCN-Gerüchte vor HD 6970-Einführung oder die Grüchte, wo man 1 GPU-Entwickelt und diese am Desgin so zusammenfügt/kopiert (1-GPU = Low-End , 2-GPU=Mainstream 3-GPUs = Performance & 4 GPUs = High-End) Diese Gerüchte von 2006, 2007 oder 2008 könnte von den Grafik-Engines so interpretiert worden sein.

Hawaii könnte schon 4 Grafik-Engines besitzen.

Also, wenn ich mit beim Spekulieren falsch vertan hatte, muss es nicht immer falsch sein, weil es genauso später kommen kann.

Übliche Verbesserungen, die man nicht in Zahlen ausdrücken kann, sind nicht nur bessere & effizientere Controllers, sondern auch Unified-Controller, die man dann besser in die APU-Einplanzen kann.

Den Schritt auf 4 Rasterizer hatte ich schon bei GCN 1.1 am Wahrscheinlichsten halte

Wobei damals ich 2 Big-Grafik-Engine mit je 2 Rasterizer (wie beim HD 5870) oder 4 Normale-Grafik-Engine mit je 1 Rasterizer für möglich hielt.

Bei GCN sollten es eher 4 Normale-Grafik-Engine mit je 1 Rasterizer sein.

Wenn die CU nicht auf 256-Shaders umgebaut werden, dann muss irgendwas anders groß umgebaut werden.

Dem Umbaut des Front-End auf 256-Shader halte ich deshalb am Wahrscheinlichsten, weil die Grafik-Engine (auf 2 Big oder 4 Normalo) schon bei GCN 1.1 umgebaut sein müsste. Wenn dort die groß umgebaut wurden, dann müsste die Grafik-Engine generell bzw. Typos komplett neu entwickelt werden. Also, vielleicht dass nachdem die CU auf HSA-fähig umgestellt wurde, dann auch die Grafik-Engine auf HSA-fähig umgetellt wird und so den nächsten Flaschenhals beseitigt.

Für mich klingt GCN 2.0 nach GCN 1.0 mit einigen Änderungen aber im Grunde gleicher Architektur.

Wie ich schon sagte, so kannst du jede Architektur bezeichnen, weil es immer nur weiterentwicklungen sind, wo immer nur Teile weiterentwickelt werden.