Convert schrieb:

XDNA ist keine Antwort auf meine Frage, sondern Teil meiner Frage. Die Frage war: Warum wird Xilinx AI (XDNA) nicht hoch skaliert auf 300W und stattdessen nur CDNA für AI optimiert?

Das war auch meine erste Überlegung, aber bei näherer Betrachtung sind mir schon einige Zweifel gekommen.

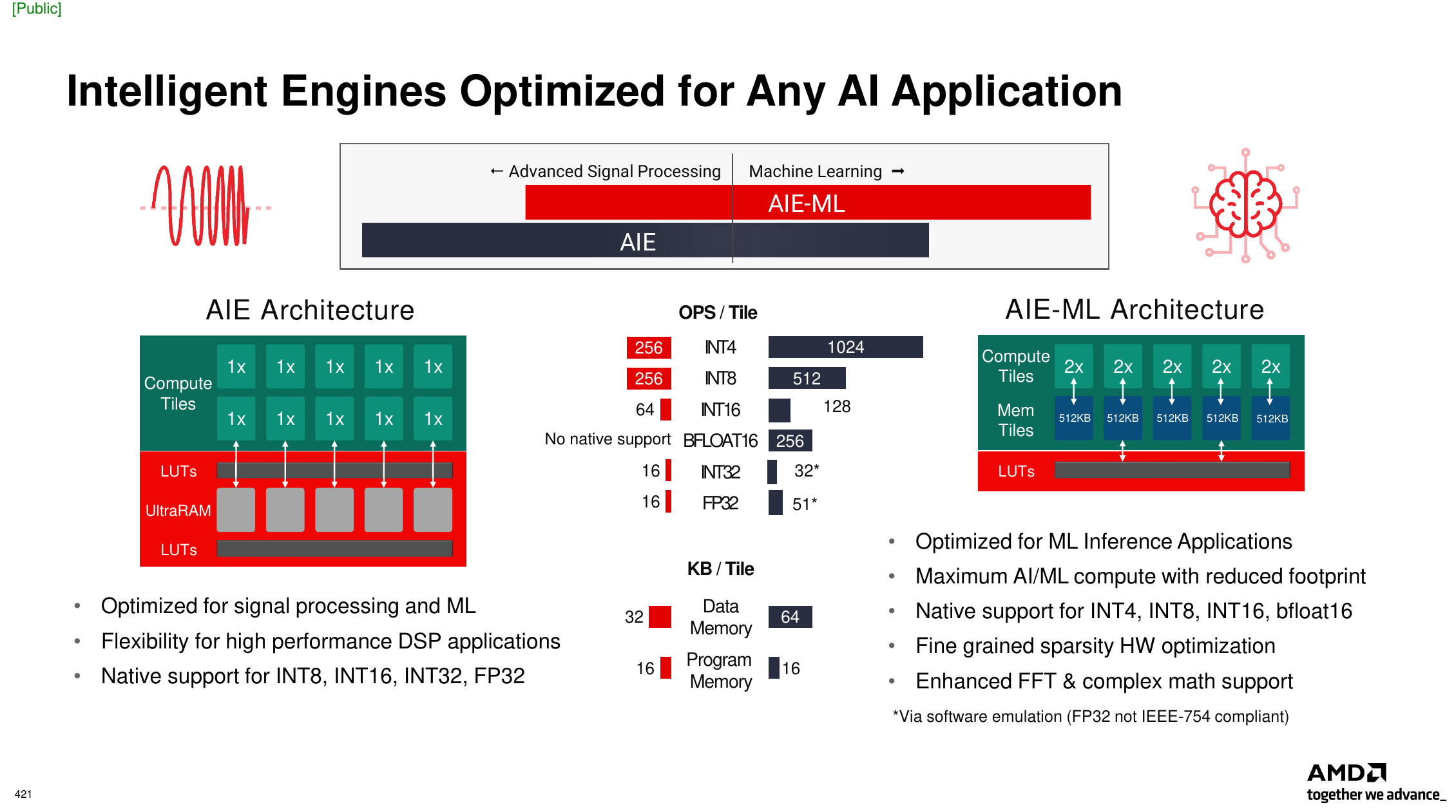

Die AIE gibt es in zwei Ausführungen (Generationen):

Die Zahlenangaben sind Operationen je Takt

Es fällt auf, dass die AIE ganz andere Datenformate unterstützt als es bei den Datacenter AI Beschleunigern der Fall ist. Die AIE setzt hauptsächlich auf Integerformate und hat zum Beispiel gar kein FP8.

David McAfee im Interview mit

TPU

TPU: AMDs KI-Hardware-Ansatz scheint ein wenig fragmentiert zu sein. Beim Ryzen 7040 "Phoenix" gibt es Ryzen AI und ein umfassendes Hardware-Feature-Set. Bei den Radeon RDNA3 GPUs gibt es AI Accelerators (skalare Matrix-Mathematik-Beschleuniger) und bei Zen 4 gibt es Unterstützung für AVX-512, bfloat16 und VNNI. Sehen Sie eine Möglichkeit, diese zusammenzuführen, um eine einheitlichere Schnittstelle für ISVs zu schaffen?

David McAfee: Ja, es gibt eine Möglichkeit. Was ich sagen kann, ist, dass verschiedene Modelle verschiedene Arten von Präzision bei der Ausführung bevorzugen. Wenn man sich die GPU-Berechnungen ansieht, sind FP16 und FP32 seit Jahren die effizientesten Operatortypen, die die GPUs lieben. So zeichnen sich sowohl unsere GPUs als auch die von NVIDIA bei dieser Art von Berechnungen aus. CPUs, ja, VNNI, bfloat16, all diese Anweisungen wurden dem x86-Befehlssatz hinzugefügt. Wenn ich mir Ryzen AI oder XDNA ansehe, denke ich, dass das Wichtigste an dieser Engine ist, dass sie wirklich auf niedrigpräzise Integer-Operationen abgestimmt ist, also INT8, INT16. Einige Leute sprechen sogar von INT4. Die Ryzen-KI-Engine bringt nicht notwendigerweise neue Befehlssätze für unsere neuen Befehlstypen oder neue Operatortypen in dieses Modell ein, sie ist einfach nur hocheffizient bei Multiplikations-, Akkumulations- und Sammeloperationen, so wie man sich vorstellen kann, dass die Schichten in einem neuronalen Netzwerk in der Lage sind, dies auf eine Art und Weise zu tun, bei der man eine Engine erhält, die komplett darauf ausgelegt ist. Ich denke, dass all diese verschiedenen Arten von Ausführungsmodulen einander in gewisser Weise ergänzen.

Bei der Ryzen-KI und dem Grund, warum sie in einem Notebook steckt, geht es sowohl um den Durchsatz pro Watt und die Leistung pro Watt als auch um die Fähigkeiten. Denn die Wahrheit ist, dass viele dieser Engines und Modelle genauso gut auf der CPU oder GPU laufen, wenn sie auf die richtige Weise für diese Befehlstypen quantisiert werden. Die ultimative Vision hier ist, dass das, was Sie heute sehen, die frühen Anwender von KI sind oder Dinge wie die Verarbeitung von Video-Feeds, Augen-Blick-Korrektur, Hintergrund-Segmentierung und solche Dinge. Ich denke, die ultimative Vision ist, dass KI etwas wird, das vielleicht nicht ständig, aber regelmäßig als Hintergrundaufgabe in Ihrem System ausgeführt wird. Es ist sehr wichtig, eine hochgradig energieoptimierte Engine in Ihrem SoC zu haben, um dies tun zu können, ohne die Batterielebensdauer zu verkürzen oder übermäßige Wärme zu erzeugen. Ich denke, die Realität ist, dass eine CPU zwar all diese Dinge tun kann, aber nicht für diese Art von Arbeit optimiert ist. Für mich ist das eine Analogie: Wenn Sie einen VP9-Videostream auf der CPU dekodieren, wird das Ihre Akkulaufzeit absolut zerstören. Wenn Sie das mit einer Videowiedergabe-Engine machen, die dafür optimiert ist, können Sie stundenlang Videos abspielen. Ich denke, das ist eine ziemlich gute Analogie, um darüber nachzudenken, was die Ryzen-KI-Engine ist und was sie in Bezug auf die Ermöglichung kontinuierlicherer Operationen von KI als Teil der Anwendung und des Betriebssystems tun wird.

Zu CDNA: MI300 investiert noch ziemlich heftig in FP64 während Nvidia das Gewicht schon deutlich in Richtung AI verschoben hat.

Convert schrieb:

Xilinx AI war ja schon fertig in Produkten, man hätte es nur hoch skalieren müssen auf größere Chips, mit mehr Speicher und eben 300W+ Verbrauch.

Die Alevo V70 ist erst dieses Jahr erschienen. Und hier wundert es mich viel eher, dass AMD diese Karte nicht in den Fokus rückt.

Convert schrieb:

Wäre doch schneller realisierbar und effizienter als ein CDNA-HPC-Beschleuniger auf AI zu optimieren.

CDNA 3 wird für El Capitan und den HPC-Markt benötigt. Beides könnte mit XDNA nicht abgedeckt werden.

DevPandi schrieb:

Dann bekommst du von mir die einfache Antwort: KI Training ist etwas anderes als später die KI-Ausführung.

Ja.

Aber KI-Ausführung aka Inference ist kein einheitliches Feld.

DevPandi schrieb:

XDNA ist für die Ausführung optimiert, CDNA für das Training.

CDNA wird sowohl für Training als auch Inference eingesetzt. Und bei Inference ist die MI300 der H100 deutlich überlegen. Der große Speicher ist gerade bei Modellen mit sehr vielen Parametern von Vorteil.

AMD stellt das Produktportfolio wie folgt dar:

Das Video ist von der Computex und überwiegend nicht auf Englisch

Auf dem FAD 2022 hatte ich den Eindruck, dass XDNA breit eingeführt wird. So wie es diese Folie zeigt:

Der Adaptive SoC ist das

@Convert mit der 350 W Karte meinst.

Die Frage ist hat sich in den letzten 1,5 Jahren die Vision geändert, oder braucht das alles eben seine Zeit.

Wenn man sieht wie sich AIE und AIE-ML unterscheiden, halte ich es durchaus für möglich, dass AMD eine AIE-Variate entwickelt, die auch ins Data Center mit den dort üblichen Modellen passt.

Skysnake schrieb:

CDNA White paper:

https://www.amd.com/content/dam/amd...-docs/white-papers/amd-cdna-3-white-paper.pdf

Programming der AMD Instinct MI300 APU:

https://nowlab.cse.ohio-state.edu/s...blicSC23ESPM2ProgrammingAMDInstinctMI300A.pdf