Icke-ffm schrieb:

Der Servermarkt ist ein Fachmarkt, wo die Kunden zu 80% Fachleute sind, die sich selbst Informieren was es gibt, die restlichen 20% kannst mit Marketing überzeugen und das geld holen da die dann 40% Umsatz zu bringen.

Und wer stellt die Dokumente bereit, mit denen sich die Fachleute informieren können?

Wie gesagt, es fällt auf was alles an Dokumenten es zu den Produkten aus der Erbschaft von Xilinix gibt und wie spärlich die Dokumentationen zu den klassischen Produkten von AMD im Vergleich dazu ist.

Ich bin der verrückten Meinung dass ein Unternehmen erklären können muss, warum es ein Produkt auf den Markt bringt. Also für welche Zielgruppe bzw. Anwendung es vorgesehen ist. Was es von den anderen Produkten unterscheidet, die das Unternehmen anbietet. Und das ist erst der Anfang, ...

Aber belassen wir es vorerst dabei. Auf meine Leseliste steht ein Buch zu dem Thema, wenn ich durch bin werde ich wahrscheinlich besser artikuieren können, was ich meine.

Als Abschluss ein

Zitat von Daniel Nenni:

In my career I have seen many great products fail and many mediocre products succeed. The difference is of course sales and marketing.

Icke-ffm schrieb:

Das Macht AMD seit MI250 schon und ist mit MI300 wohl auch recht erfolgreich, aber steckt noch in den Kinderschuhen, oder aber es gibt schlicht nicht genügend Kapazität fürs packaging reicht einfach nicht aus.

RDNA und CDNA sind von den erzielbaren Preisen komplett andere Kategorieren. Und das war es schon vor dem explodierenden AI-Bedarf. Und die erzielbaren Preise definieren den Kostenrahmen in dem ein Produkt erstellt werden kann.

Fanout, eingebettete Siliziumbrücken oder Silizium Interposer sind lange eingeführte Techniken. Kinderschuhe finde ich deshalb unpassend. Aber Siliziumbrücken und Silizium Interposer wurden bisher nicht in Massenprodukten eingesetzt.

Fanout ist die mit deutlichem Abstand die günstige von diesen, und deshalb hat AMD sie für RDNA 3 verwendet.

Aber die Verbindungsdichte von Fanout genügt nicht um zwei oder mehr GDC zu einer GPU zu integrieren. Dazu sind mindestens Siliziumbrücken erforderlich.

Icke-ffm schrieb:

Richtig, aber wieso hat TSMC als reine Foundry obwohl sie 1/4 weniger Produzieren dann noch immer nahezu die selben gewinne ?,

Die Bruttomarge ging 2023 im Vergleich zu 2022 deutlich zurück. TSMC leidet eben auf einem extrem hohen Niveau.

Aus TSMC Management Report Q4 2023

Die Überkapazitäten ergeben sich auch, weil TSMC die CAPEX zurückgefahren hat, aber nach wie vor auf hohem Niveau hält. D. h., massiv Waferkapazität aufbaut.

Icke-ffm schrieb:

weil sie eben auch gewinne einfahren mit Geräten/Gebäuden/Investitionen, die längst abgeschrieben sind.

TSMC hat von 2022 auf 2023 einen Rückgang der verkauften Wafer um 3,2 Mio hinnehmen müssen, also ca 20 %. Die Einnahmen gingen aber deutlich weniger zurück weil das TSMC mit mehr Wafern bei 3 nm und 5 nm kompensieren konnte.

Bei den klassischen Nodes hat TSMC den größten Konkurrenzdruck und die Anlagen der Konkurrenz wären ebenfalls abgeschrieben. Andererseits gibt es auch so etwas wie Erhaltungsinvestitionen und Wartungskosten, was aber für TSMC wie die Konkurrenz gilt.

Aus TSMC Management Report Q4 2023

Um nicht missverstanden zu werden, 5 nm war die ganze Zeit schlecht ausgelastet.

Ich habe für Q1 2024 noch keine exakten Zahlen zu den Umsätzen weil der Financial Report für dieses Quartal noch nicht ausgewiesen wurde.

AFAIK sind die Waferkapazitäten bei 7 nm und 5 nm ähnlich groß. Bei den deutlich höheren Preisen von 5 nm muss der Waferumsatz bei Vollauslastung auch deutlich über dem Peak von 7 nm liegen. Das ist nicht der Fall.

Und wie gesagt hat TSMC in Quartalskonferenzen zu Q1 2023, Q3 2023 und Q4 2024 darüber geredet ungenutzte N5 Kapazität für N3 zu verwenden.

Icke-ffm schrieb:

Fast, aber nein dann werden die nächsten Jahre Interessant, und wenn mir Die Zahlen zusagen gehe ich auch wieder all in bei AMD und hoffe auch die nächsten 1000% gewinn, was sich dann endlich lohnen würde

In den aktuellen Kursen, auch in denen nach dem Rückschlag, ist schon sehr viel Erfolg mit AI eingepreist. Den muss AMD erst noch einfahren, um die aktuellen Kurse zu rechtfertigen.

Wenn Du bei den ersten 1000% Kurssteigerung nicht genug rausgeholt hast, dann hast Du zu wenig investiert. Und zweitens bist Du zu spät eingestiegen. Mit einem bisschen Vertrauen im Jahr 2015 wäre deutlich mehr als Faktor 10 drin gewesen, :-).

2015 gingen Lisa Su und Mark Papermaster auf Tour bei Privatinvestoren, um mit Zen Geld einzusammeln. Das mit dem Potential von Zen hat sich herumgesprochen, weshalb die Kurse angezogen haben. So viel zum Thema die Börse hat keine Ahnung, ...

Dass der Aktienkurs nochmal um den Faktor 10 steigt wird IMO sehr sehr lange dauern.

Icke-ffm schrieb:

Intel und AMD werden vor dem Q3 Ihre neuen Customer Produkte sammt Leistungsdaten (eigene) vorstellen.

daher ist es recht einfach das kommende Jahr abzusehen. Q2 ist das Schlüsselquatal für 24

Aber die ganzen Produkte kommen frühestens in Q3 auf den Markt und somit haben sie auf die Zahlen von Q2 praktisch keinen Einfluss. Bzw. allenfalls negativen Einfluss, weil Käufe aufgeschoben werden.

Und wir hatte es doch von den Quartalsabschlüssen, oder? Und genau wegen der ganzen Produktvorstellungen halte ich alles nach Q2 für viel interessanter.

Wobei die Consumer Produkte aus AMD Sicht das langweiligste sind. Die Erwartungen an RDNA 4 sind nicht sonderlich hoch. Technisch wird sich aller Voraussicht nach an den Desktop CPUs außer dem Kern wenig tun. Einzig Strix Point hat einen gewissen Reiz da es eine Hybrid APU ist, mich interessiert wie die 12 Kerne organisiert werden und ich mit Spannung darauf warte was XDNA 2 tatsächlich ist. Sind es lediglich mehr Tiles, wie die Leaks suggerieren oder steckt AIE-ML v2 dahinter.

Das einzig richtig spannende Produkt für Consumer ist IMO Strix Halo. Und das weniger wegen der 40 CUs, sondern wegen der Gerüchte, die sonst noch herumwabern. Einige behaupten Strix Halo wäre ein Ausblick auf Zen 6. Mit Fanout und Zen 5LP Kernen im IOD. Low Power Kerne wären genau das was man bräuchte um die Effizienz bei kleinen CPU-Lasten massiv zu erhöhen. Denn dann könnte man diese kleinen Lasten auf dem IOD abarbeiten. Damit ware es möglich die CCDs und den Infinity Fabric zu den CCDs schlafen zu legen.

Aber Strix Halo kommt erst nächste Jahr.

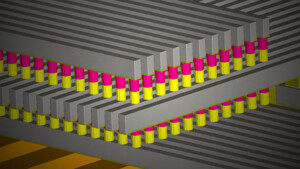

Bei den EPYC interessiert es mich sehr wie AMD die zusätzlichen CCDs unterbringt und vor allem wie der Inifinty Fabric geroutet wird. Sollten die Schemas von YuuKiAnS die tatsächliche Anordnung wiedergeben,

kann dass nicht mit dem bisherigen Routing funktionieren.:

aus: Pioneering Chiplet Technology and Design for the AMD EPYCTM and RyzenTM Processor Families

Bisher wurde der Infinity Fabric unter der L3-Caches der CCDs hindurch geroutet und die I/O durch die Lücke zwischen CCD.