foofoobar

Commodore

- Registriert

- Dez. 2011

- Beiträge

- 4.162

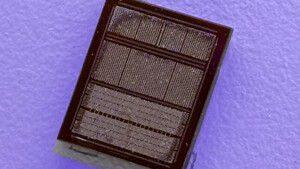

-Ps-Y-cO- schrieb:Ein HBM-Chip der ersten Generation soll einen Speicherdurchsatz von 128 Gigabyte pro Sekunde ermöglichen und damit DDR- und GDDR-Speicher weit hinter sich lassen. Bei der nachfolgenden Generation werden bis zu acht DRAM-Schichten mit höherer Speicherdichte und ein Durchsatz von 256 GB/s prognostiziert. GDDR5 erreicht bei aktuell maximal 3.500 MHz pro Chip einen Durchsatz von 28 GB/s.

Die Daten müssen über die Pins vom Gehäuse auch rein und raus. Und an den Latenzen wird sicherlich nicht ändern.

Siehe hier: http://www.setphaserstostun.org/hc26/HC26-11-day1-epub/HC26.11-3-Technology-epub/HC26.11.310-HBM-Bandwidth-Kim-Hynix-Hot%20Chips%20HBM%202014%20v7.pdf Seite 5.

Da steht was von RLC decrease, mal sehen wie viele Chips/Pins an einer Leitung ansteuerbar sind, wenn das man keine PtP Verbindung werden wird.

Über den PHY bzw. Layer0 bzw. Bandwith per Pin der Verbindung steht da nichts!

Zuletzt bearbeitet: