Solavidos schrieb:Würde gerne wissen, woran das liegt, denn bei Samsung oder Intel arbeiten ja auch top Leute.

Ich denke hier sieht man sehr gut die Unterschiede in der Unternehmenskultur. TSMC hat es offenbar geschafft ein System zu schaffen in dem technischer Fortschritt erzielt wird und auch in der Fertigung ankommt. Und natürlich auch die richtigen Prioritäten gesetzt.

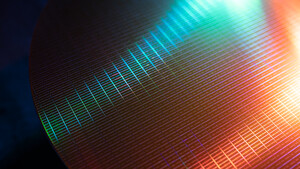

Die Chipfertigung umfasst so viele Fachbereiche, dass ein Rückstand in einem fatale Auswirkungen haben kann. Es würde reichen wenn sie die Chemie für den Belichtungslack nicht hinbekommen z.B.

Oder wenn das Management zu konservative Entscheidungen trifft und so kein Fortschritt erzielt wird.