BlackWidowmaker schrieb:Ich glaube das Problem liegt daran, daß in den Köpfen der Menschen eine SSD auch bloß ein Massenspeicher ist, mit neuer Technik.

Das ist doch gut so, stimmt nämlich auch.

BlackWidowmaker schrieb:SATA - das S steht für seriell, das was macht wenn man mit einem magnetischen Dingbums...

Das ist grober Unfug. Die Schnittstelle hat nichts damit zu tun wie die Schreib-/Leseköpfe die Daten lesen/schreiben. Der Kopf wird auch nicht von der CPU gesteuert und die Daten werden auch nicht vom Lesekopf direkt in den RAM oder die CPU-Register geschrieben. Der Kopf kommuniziert erst einmal nur mit seiner eigenen Laufwerkselektronik, die besteht im wesentlichen aus einem Controller und mehreren Puffer-Speichern. Daten, die vom Controller über das Interface zum Rechner geschickt werden kommen entweder aus diesen Puffern oder eben aus dem eigenen Cache. Lange Zeit hat man ein paralleles Interface benutzt (wer erinnert sich nicht an die Flachbandkabel). Bei parallelen Interfaces hat man das Problem, dass man nur mit niedrigen Taktraten arbeiten kann ohne Timing-Probleme zu bekommen. Da ist es viel einfacher ein serielles Interface zu wählen und dafür den Takt hochzujagen.

Das macht nur bei der Softwaretechnik irgendeinen Sinn. Der Haken dabei ist, dass es nur wenige Probleme gibt, die beliebig parallelisierbar sind. Sobald ein Rechenschritt von dem Ergebnis eines vorherigen abhängt, ist es aus mit Parallelisierbarkeit. Das ist ein Problem in der Natur der Sache. Du kannst optimieren, versuchen es zu umgehen, aber auslöschen kannst du es nicht.BlackWidowmaker schrieb:Nix da mit seriell sondern alles streng parallel.

BlackWidowmaker schrieb:Nix da mit 64-Bit Windows, sondern Hard- und Software mit 1024-Bit aufwärts rechnet. Anstatt Caches und Turbos und schlag-mich-tot Power durch Parallelität.

Die Bitbreite, mit der eine CPU arbeitet sagt nicht über deren Geschwindigkeit aus. Es sagt nur etwas darüber aus, wie groß der Zahlenbereich ist, mit der es "auf natürliche Weise" umgehen kann. Da man die meisten "normalen" Probleme eher mit kleinen Zahlen arbeiten, wäre eine 1024-Bit CPU kaum schneller. Sie wäre höchstwahrscheinlich sogar deutlich langsamer, weil man sie nicht ansatzweise so hoch takten könnte wie aktuelle 64-Bit CPUs.

BlackWidowmaker schrieb:Anstatt SSDs mit 8-Kanal Kontroller, SSDs mit 128-Kanal bauen da dafür auf RAM verzichten.

a) Du müsstest dann aber auch min. 128 Flashbausteine verbauen. Bei den gängigen Größen wäre das eine sehr teure Sache.

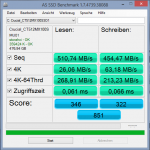

b) Mehr Kanäle erhöhen nur den Durchsatz, verringern aber nicht die Latenz. Deswegen sind Flash-Bausteine kein praktikabler RAM-Ersatz. Ein RAM-Baustein hat eine Zugriffszeit von ~10ns. Ein Flash-Baustein hat Zugriffszeiten, die um den Faktor ~2500 (lesen) bzw. 20.000 (schreiben) höher liegt.

BlackWidowmaker schrieb:Nein, das stimmt nicht. jeglicher Massenspeicher auf Magnetbasis ist auf serieller Basis aufgebaut. Es kann prinzipiell nur 1 Bit (pro Lesekopf) gleichzeitig ausgelesen/geschrieben werden. Flash Speicher ist dagegen wie RAM prinzipiell beliebig parallelisierbar. Die Einschränkungen diesbezüglich sind eher wirtschaftlicher Natur.

Das mag ja prinzipiell richtig sein, bringt dir in der Realität für gewöhnlich aber nichts, denn das kommt erst zum tragen, wenn du sehr große Datenmengen (am Stück) hin- und herschiebst.

BlackWidowmaker schrieb:Das wovon ich spreche würde bedeuten einen Computer für Flash-Speicher zu bauen, anstatt Flash-Speicher für herkömmliche Computer einzusetzen. Das würde verlangen eine komplett von Grund auf neu konzipierte Hardwarearchitektur, ein auf Grund auf neu entwickeltes BS ohne irgendwelche Legacy-Schranken und entsprechend völlig neue Software die für so einen Computer optimiert wäre.

Wenn es nur so einfach wäre. Das Problem ist nicht die Hardware-Architektur. Stark parallel arbeitende Architekturen gibt es (Grafikkarten oder auch einige exotische Supercomputer). Die bringen aber leider nur dann Vorteile, wenn man Probleme zu lösen versucht, die gut parallelisierbar sind. Viele heutige Anwendungenfälle sind dies aber nicht und damit bleiben solche Architekturen auch weiterhin nur für Spezialanwendungen geeignet.

Zuletzt bearbeitet: