Colindo schrieb:

Ich dachte an das hier:

Anhang anzeigen 1219678

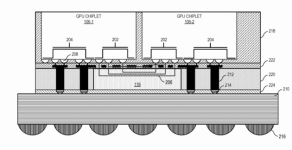

Das ist die MI 200, die entsprechend des Patents US20200409859 "GPU CHIPLETS USING HIGH BANDWIDTH CROSSLINKS" umgesetzt wurde. 118 ist die passive Siliziumbrüche die die beiden GUP Chiplets 106-1 und 106-2 verbindet. Im Patent heißt 118 passive crosslink.

210 ist im Patent explizit ein "circuit board" aus keramischen oder organischen Material.

Die schnellen Verbindungen laufen in der 118 der Siliziumbrücke, die langsameren im RDL 222 . Das Circuitboard 210 dient hauptsächlich zur Verbindung zu den C4 Bumps 216.

Es gibt keinen Interposer, durch den bei klassischen 2.5D-Verfahren wie CoWoS von TSMC alle Verbindungen zwischen den Chips laufen. Durch den Verzicht auf den großen Interposer spart AMD erheblich Kosten ein. Da das Recticlelimt von 26 mm x 33 mm auch für die Interposer gilt, erfordert das Belichten von großen Interposern einen großen Aufwand. Eine kleine Siliziumbrücke lässt sich sehr einfach fertigen.

Die GPU-Chiplets werden durch Microbumps 208 mit dem RDL 222 verbunden.

212 sind Kupferposten, die über der RDL erstellt werden und die den RDL 222 mit dem circuit board 210 verbinden. 218 und 220 sind sogenannte Molding Layer. Molding meint das vergießen der Chiplets mit einem wärmeleitfähigen Polymer. Das ist ein Kernschritt des FanOut-Prozesses. Das verleiht dem ganzen die mechanische Stabilität.

RDL = Redistribustion Layer.

Wäre RDL 222 direkt mittels Microbumps mit dem Substrat verbunden, hätten wir ein klasischen FanOut wie TSMC InFo oder Fan-Out Chip on Substrate (FOCoS) von ASE. Die oben gezeigte Variante entspricht sFOCoS von ASE. Die Variante mit Siliziumbrücke bei TSMC heißt InFO-L(SI). Ob TSMC auch Kupferposten verwendet weiß ich momentan nicht. Beides ist vergleichbar mit Intels EMIB.

Colindo schrieb:

Du denkst wahrscheinlich hieran:

Anhang anzeigen 1219679

Auch, es gibt in den Patenten andere Darstellungen, die mehr verraten, siehe unten

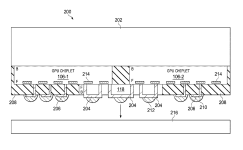

312 und 314 sind die aktiven Schaltkreise. 304 sind die TSV. Wenn man genau hinschaut erkennt man dass es hier zwischen TSV und den GCD

keine Microbumps gibt. Das heißt die TSV die durch die Active Bridge gehen, werden direkt mit der Metalisierungsebene der Chiplets verbunden.

Das fehlen der Microbumps ist für mich der eindeutige Hinweis, dass hier TSMC SoIC geplant ist. Wie beim 5800X3D. Da keine Microbumps erforderlich sind, ist eine Verbindung mit kleinen Abständen und hervorragenden elektrischen Eigenschaften möglich. Die Bandbreitendichte und Effizienz des Datentransfers sind im Vergleich zu anderen Verbindungstechniken enorm.

Die Anordnung GCD oben Active Bridge unten erwarte ich nicht. Sie hat den Vorteil, dass die GDC besser gekühlt werden da der Kühler oben ist. Allerdings ist die Signalführung ungünstiger, da alle Signale (Speicher, CPU) und die Versorgungsleitungen zu den GDCs IMO durch die Active Bridge geführt werden müssen.

Diese Grafikzeigt die Anordnung die ich eher erwarte, die Metalisierung auf den Chiplets (GCD!) die Active Bridge (X3D!) auf der Rückseite der GCD. Da der Zugriff auf den GDDRAM und CPU von den Chiplest erledigt wird, gibt es keinen Bedarf für viele externe Verbindungen zur X3D. Es werden allerdings viele TSV von der Vorderseite F auf die Rückseite B des GCD geführt. Da hier keine Microbumbs gebildet werden wird ein Hybridbondingprozess wie TSMC SoIC verwendet.

Die Anordnung von Bild 5 D entspricht dem 5800X3D. Auch wenn die meisten Grafiken etwas anderes suggerieren. Auch beim 5800X3D sind die Metalisierungsebenen mit den Bumps an der Vorderseite des CCDs und die TSV gehen durch den CCD zum 3D-Cache der auf die Rückseite des CCDs aufgebracht wird..

Es gibt

keinen RDL was gegen FanOut spricht es gibt

keinen Interposer was gegen 2.5D spricht.

Natürlich kann AMD so eine GPU auf einen RDL oder Interposer setzen um die GPU in ein größeres Package zu integrieren. Ich gehe davon aus, dass sie nur auf ein Substrat kommt.

Falls RDNA3 eine Multi-GPU wird dann entsprechend dieser Patente d. h. mit TSMC SoIC. Deshalb gehe ich davon aus, dass der 5800X3D und Milan-X nur die Generalprobe sind.

Ich bin mir relativ sicher, dass AMD dem Rectile Limiit (26mm x 33 mm) nicht nahe kommen wird. Meiner Meinung nach hat AMD sich entschieden den Weg über das Advanced Packaging zu gehen.