M

Mickey Cohen

Gast

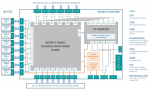

ITX schrieb:Das macht endlich mal Sinn! 👍

Aber sind die 4 Lanes, die normalerweise zum Chipset gehen würden, auch "flexible" wenn die CPU "stand alone" betrieben wird? Werden wir wohl erst erfahren wenn Matisse offiziell vorgestellt wird.

interessante frage, kann ein ryzen überhaupt standalone laufen?