SaschaHa

Commodore

- Registriert

- Nov. 2007

- Beiträge

- 4.969

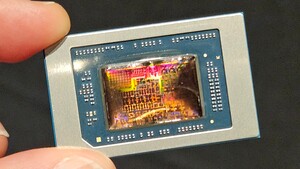

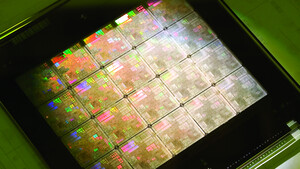

96 Kerne bei Zen 4 (bzw. 50% mehr als bisher) habe ich schon länger vermutet, da TSMC's 5 nm-Fertigung ja etwa 84% mehr Transistoren erlaubt und die einzelnen Kerne ja wieder etwas erweitert werden (Sprich: 50% mehr Kerne + ~20% mehr Komplexität pro Kern = ~80% mehr Transistoren).

Was ich hier aber eher für unplausibel halte, sind die 6096 Kontaktflächen, um dies zu erreichen: Die 96 Kerne wären - wie oben beschrieben - dank 5 nm auch bei etwa der gleichen Fläche wie bisher möglich.

Betrachtet man zudem die bisherigen TR-CPU, sieht man, dass dort bereits jetzt deutlich mehr Platz auf den Platinen vorhanden ist, sodass theoretisch sogar jetzt schon mehr als 64 (Zen 3) Kerne möglich gewesen wären.

Die 96 Kerne halte ich daher selbst unter Berücksichtigung einer höheren Komplexität pro Kern für absolut plausibel bei etwa gleichbleibender Sockel-Größe. Sollte diese aber derart (um etwa 50%) steigen, dürften auch 128 oder gar 144 Kerne möglich werden, wobei ich 144 aber eher für unrealistisch halte.

Ich denke, der nächste Sockel wird entweder eher auf ca. 4500 Pins und bis zu 96 Kernen hinauslaufen, oder aber - bei 6096 Pins - auf bis zu 128 Kerne (alleine schon wegen der psychologischen "mehr als Hundert"). Kommt aber natürlich auch darauf an, wie weit sich Zen 4-Kerne von ihrem Vorgänger unterscheiden und was für Zen 5 geplant ist. Sollte bis Zen 5 bereits eine mehr als 60% höhere Komplexität gegenüber Zen 3 geplant sein, sind die Spekulationen durchaus plausibel.

Was ich hier aber eher für unplausibel halte, sind die 6096 Kontaktflächen, um dies zu erreichen: Die 96 Kerne wären - wie oben beschrieben - dank 5 nm auch bei etwa der gleichen Fläche wie bisher möglich.

Betrachtet man zudem die bisherigen TR-CPU, sieht man, dass dort bereits jetzt deutlich mehr Platz auf den Platinen vorhanden ist, sodass theoretisch sogar jetzt schon mehr als 64 (Zen 3) Kerne möglich gewesen wären.

Die 96 Kerne halte ich daher selbst unter Berücksichtigung einer höheren Komplexität pro Kern für absolut plausibel bei etwa gleichbleibender Sockel-Größe. Sollte diese aber derart (um etwa 50%) steigen, dürften auch 128 oder gar 144 Kerne möglich werden, wobei ich 144 aber eher für unrealistisch halte.

Ich denke, der nächste Sockel wird entweder eher auf ca. 4500 Pins und bis zu 96 Kernen hinauslaufen, oder aber - bei 6096 Pins - auf bis zu 128 Kerne (alleine schon wegen der psychologischen "mehr als Hundert"). Kommt aber natürlich auch darauf an, wie weit sich Zen 4-Kerne von ihrem Vorgänger unterscheiden und was für Zen 5 geplant ist. Sollte bis Zen 5 bereits eine mehr als 60% höhere Komplexität gegenüber Zen 3 geplant sein, sind die Spekulationen durchaus plausibel.