.Sentinel.

Admiral

- Registriert

- Okt. 2007

- Beiträge

- 8.650

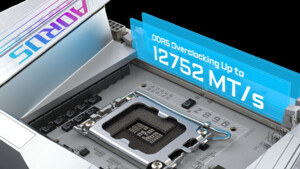

Fast... Die Latenz hängt ja auch in Relation an den Taktzyklen und wird mit steigendem Takt "virtuell" wieder niedriger.TøxicGhøst schrieb:Warum werden jedesmal bei neuem Arbeitsspeicher die Latenzen höher? Bei DDR3 war für die meisten noch CL9 Standard, jetzt bei DDR4 sind es CL16.

Nach dem Motto "Verdoppelung der Bandbreite, Verdoppelung der Latenz" oder wie?

Aber im Großen und Ganzen tritt man mit der Latenz seit ewigen Zeiten dadurch fast auf der Stelle.

Man versucht das zwar durch immer größere Caches zu kaschieren, aber dennoch geraten Multicore- Systeme inzwischen in einigen Szenarien immer öfter an den Punkt, wo sie Wartezyklen einschieben, weil auf Daten gewartet werden muss.

Siehe auch:

https://en.wikipedia.org/wiki/Random-access_memory#Memory_wall