@v_ossi

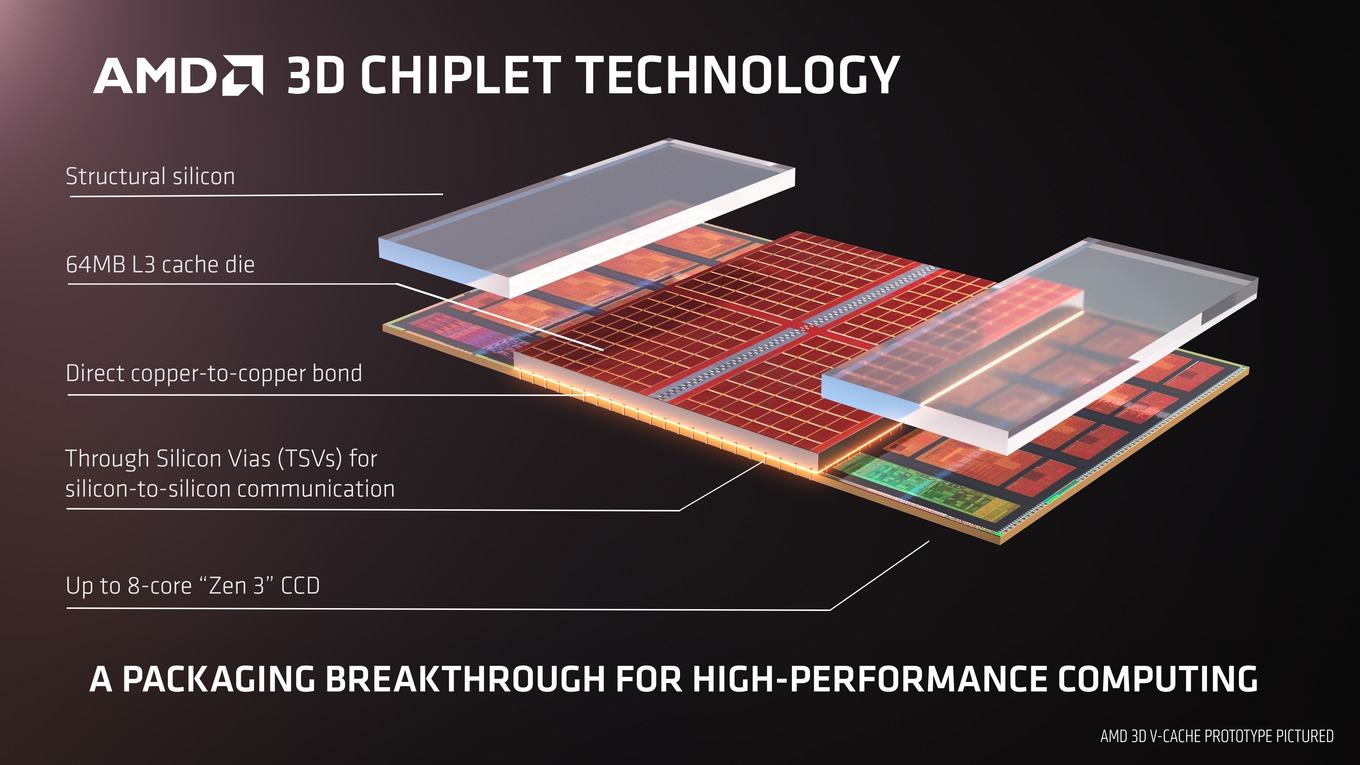

Das Silizium wird stark abgeschliffen und der Cache überlappt nur mit dem Cache (zumindest nach Marketing).

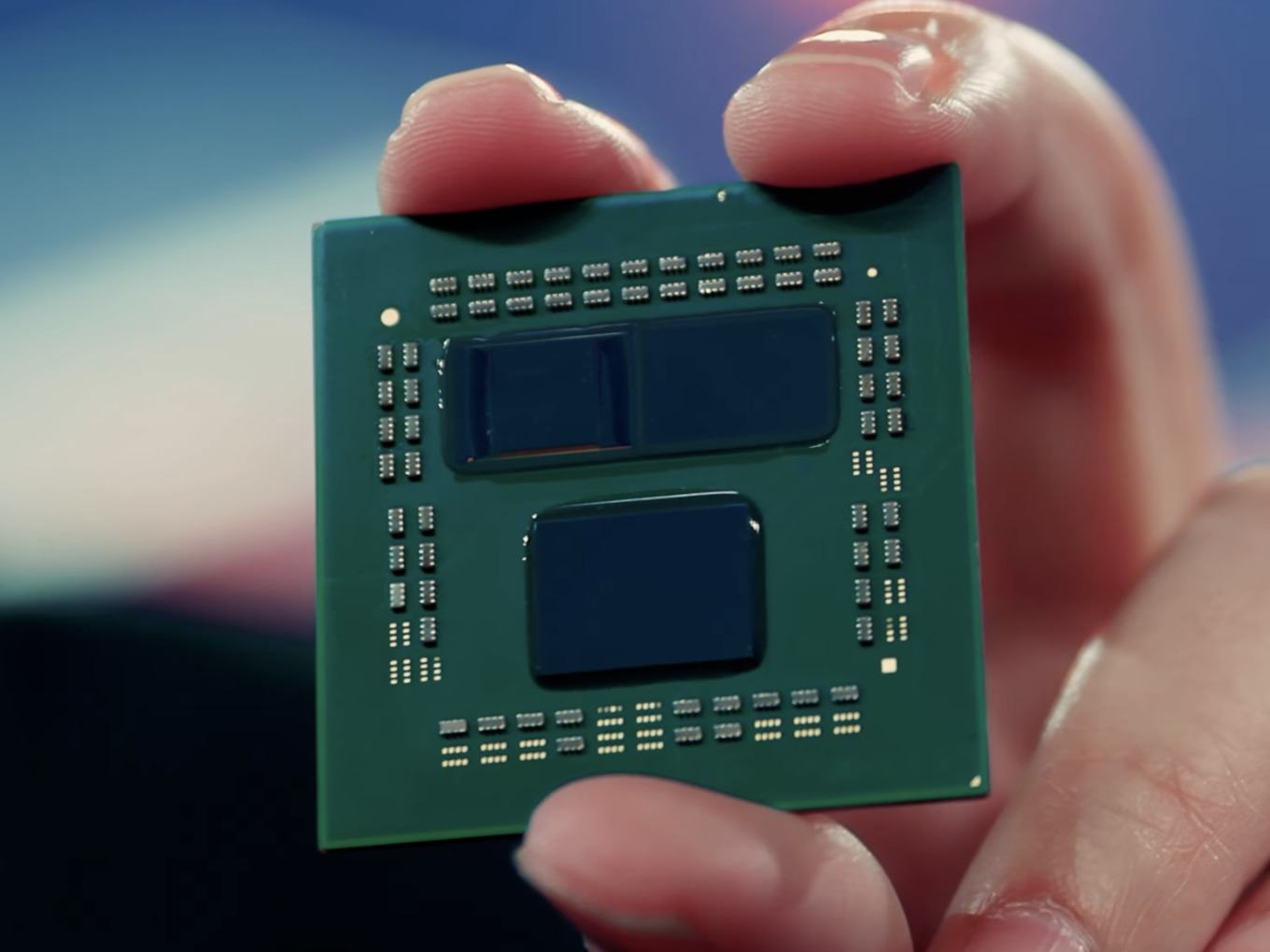

Theoretisch sollte der Impakt nichtig sein, u.U. sogar positiv, da weniger Silizium als "Dämmschicht" zwischen IHS und Core ist.

Bild bei HWLuxx

Das Silizium wird stark abgeschliffen und der Cache überlappt nur mit dem Cache (zumindest nach Marketing).

Theoretisch sollte der Impakt nichtig sein, u.U. sogar positiv, da weniger Silizium als "Dämmschicht" zwischen IHS und Core ist.

Bild bei HWLuxx