RKCPU schrieb:

Im Mobilbereich max 16 Zen5, dafür aber auch 4x Zen5 plus 8x Zen5c nach aktuellen Spekulationen.

Das Problem liegt im Wort Spekulationen.

Ich halte es für sehr wahrscheinlich, dass sowohl Dragon Range als auch die beiden Phoenix Zen 5 Nachfolger bekommen. Ob Strix Point in der genannten 4 P und 8 E Konfiguration kommt, werden wir sehen. 2 P und 4 E wie bei Phoenix 2 wäre dann aber ein großer Abstand zwischen Strix Point und Strix Point 2.

Heute hat

Harakuze5719 ein paar SKUs von 7000G und 8000U veröffentlicht. Es sind nur Phoenix 2 bzw. der Refresh enthalten. Die Grafiken enthalten aber offensichtliche Fehler. Eine Quelle nennt Harakuze5719 nicht.

RKCPU schrieb:

Sollte AMD beim Zen 5c erweiterte Modulbauweise nutzen, also shared L2, wie 1,5 MB und erweiterte shared FPU setzen dann würden 12 Cores am 8er CCX passen.

Auch hier gilt, man kann sich viel vorstellen.

Zum shared L2 für die E-Cores bei Strix Point gibt es sich widersprechende Leaks. Auch wenn mich die Idee sehr reizt, ist das Leak aus dem es stammt nicht vertrauenswürdig. Dieses Leak besteht aus 2 Screens und zeigt auf beiden Screens verschiedene Werte für die Größe des L3-Caches. Von den unsinnigen Taktraten Mal abgesehen.

Die Modulbauweise wäre ein tiefgreifender Unterschied zwischen Zen 5 und Zen 5c. AMD hat bei Zen 4c die FPU unverändert übernommen, deshalb ergibt ein so tiefgreifender Wandel für mich keinen Sinn.

RKCPU schrieb:

Die FPU ist für die meisten Anwendungen der Zen 'c' nur selten genutztes Beiwerk. Beim Zen5c Chiplet könnten dann 8 Module die 16 Cores ergeben, welche dann aber durchaus 64 MB L3 aufweisen könnten (L3 ist bei 'c' ja kompakter).

Zen 4c hatte weniger Cache je Kern als Zen 4. Der Performance hat es, wie die Benchmarks von Phoronix für Bergamo und Siena zeigen, nur wenig geschadet. Deshalb gibt es keinen Grund für AMD den L3-Cache bei Zen 5c zu vergrößern. Ich sehe auch keinen Grund für eine Zen 5c Variante mit 3D V-Cache.

Bei allen Überlegungen zu einem größeren On-Die Cache muss berücksichtig werden:

- Wenn man den Cache größer macht, leidet immer auch die Latenz. Wichtig dabei ist, dass die "Latenz-Strafe" klein ausfällt.

- AMD hat 3D V-Cache um SKUs zu fertigen, die sehr stark von mehr Cache profitieren. Es ist übrigens der Clou, dass beim 3D V-Cache die Latenz nur ein kleines bisschen leidet. Es gibt die Anmerkung von Sam Naffziger, dass 96 MByte in einer Ebene nicht möglich gewesen wäre, weil die Latenz zu schlecht geworden wäre.

- Der L3-Cache wird zwischen 5 nm und 3 nm nicht skalieren.

- Hybrid Bonding, das Verfahren mit dem der 3D V-Cache "montiert" wird, ist relativ neu und entsprechend teuer.

RKCPU schrieb:

16 Core CCX beim Zen5 stellt die Frage welche Produkte dann kommen würden, denn auf 6-Core gestutzt macht dann wenig Sinn.

Dass ich dieses Gerücht sehr skeptisch sehe, liegt vor allem an der Spekulation über die 16 Kern CCX für Zen 5 und die 32 Kern CCX für Zen 6. Und dann sagt MLID im selben Video, dass Zen 5 hat ein 8 Kern CCD und Zen 5c ein 16 Kern CCD haben soll.

Wie gesagt entweder man vertraut seinen Quellen oder man vertraut Ihnen nicht. Die Folie sagt explizit Zen 5 mit einem 16 Kern CCX und Zen 6 mit einem 32 Kern CCX. Da steht kein "up to" aus dem man interpretieren könnte, dass es Varianten gibt.

RKCPU schrieb:

Ein Ryzen 9000 mit 32 Cores je Chiplet ergibt keinen Sinn, er ersäuft in der Abwärme des DIE - selbst in 2nm Technik.

Kannst Du mir bitte Mal die Logik dahinter erklären? 32 Cores haben die 4 fache Fläche wie 8 Cores. Wenn 32 Cores mit der 4-fachen Fläche die Wärme nicht abführen können dann klappt es auch bei 8 Cores nicht.

Auch die monolithischen Dies nehmen nur eine kleine Fläche unter dem Heat Spreader ein. Das Problem, das sich bei den Ryzen gezeigt hat, ist IMO, dass die CCDs als größte Wärmequelle nicht in der Mitte sondern eher am Rand und bei Ryzen 7000 ganz am Rand des Heat Spreaders sitzen. Dadurch werden Heats Spreader und Kontaktfläche des Kühlers asymmetrisch belastet und können deshalb nicht so effektiv wirken, als wenn die Wärmequelle im Zentrum wäre.

RKCPU schrieb:

Viel Platz benötigt weiterhin der L3-Cache, da wäre eher 8er CCX mit nativ 24 MB, dazu 1-2 3D Lagen mit dann 24+48 MB bzw. 24+96 MByte sinnvoll. Der Ryzen 9600 hätte dann eben nur 24 MB, ein 9700X3D dann 8-Core 72 MB.

Ich halte es für sehr verfrüht sich über Zen 6 Gedanken zu machen. Zuerst will ich Zen 5 und Zen 5c sehen.

Warum sollte AMD den L3-Cache bei Zen 6 zurückfahren? AMD müsste für sehr viel mehr SKU 3D V-Cache anbieten. Im anderen Post willst Du den L3-Cache bei Zen 5c vergrößern, wo ist da die Logik?

Ich denke es ist nur eine Frage der Zeit bis 3D V-Cache mit mehr als einer Lage auftauscht. Aber im Desktop erst sehr viel später als im Server.

RKCPU schrieb:

Beim Zen6c ist das anders, wobei Intel ja jeweils ein Cluster mit 4 Cores bildet, je 4 ähnliche an ein 8er CCX und fertig wäre ein 32-Core.

Die Idee mit den Clustern hat mir bei den Mobilprozessoren gefallen. Bei den Servern sind die Cluster IMO eine sehr schlechte Idee.

RKCPU schrieb:

Der 'c' schleppt viel FPU und L2 mit sich rum, eigentlich zuviel Fläche, die selten benötigt wird.

Das war auch meine erste Idee.

Allerdings sehe ich inzwischen bei der Verwendung von Zen 4c in Siena einen Nutzen in einer starken FPU. Bei Bergamo je nach Anwendung*) ebenfalls. Und AMD hat die Fläche des Kerns massiv reduziert ohne die Funktion der FPU zu beschneiden. Passt doch.

*) Die Benchmarks zeigen dass Bergamo auch für massiv parallele Anwendungen funktioniert, d. h. die Cloudanbieter mit ihren single CPU Instanzen sind nicht die einzigen Anwender von Bergamo.

Das mit AVX-512 aufbohren sehe ich sehr kritisch. Was ist das Problem mit der aktuellen Implementierung? Wie viele Anwendungsfälle profitieren davon? Lohnt es sich dafür den Durchsatz durch das Front end zu verdoppeln?

Beim L2 Cache bin ich ziemlich unschlüssig. Intel braucht einen großen L2 Cache, AMD eigentlich nicht, da der L3 Cache bei Zen 4 hervorragende Latenzen hat. Dementsprechend klein war der Zuwachs an IPC durch das Verdoppeln des L2 Caches.

RKCPU schrieb:

Ich tippe mal, dass Zen 5c Modulbauweise bekommt, also 4-fach SMT FPU, 2x Integer und shared 1,5M L2 je Modul bei 2/4 Threads. Zen 6c würde dann 'nur' SMT im Vollausbau verlieren, die FPU bliebe gleich, L2 dann 2M. Teildeaktiviert wieder 2/4 SMT.

Bei Bulldozer hat sich AMD entschieden auf SMT zu verzichten und hat statt dessen 2 Integer-Module verbaut. SMD und Integer-Module wäre was neues.

Der Unterschied im Verhalten zwischen Zen 5 und Zen 5c wäre sehr groß, was wiederum erheblich höheren Aufwand bei der Validierung auslöst und für nette Probleme sorgen kann, d. h. dass sich Software auf den Zen 5 und Zen 5c unterschiedlich verhält.

Ich denke das Thema Module hat sich für Zen erledigt. Wenn AMD wieder auf sowas zurück wollte, wird es eine komplett neue Architektur geben und Zen wird beerdigt. Als Teillösung für "c"-Kerne halte ich es für extrem unwahrscheinlich.

RKCPU schrieb:

Ein 8er CCX hätte dann 4x Zen 6 plus 4x 4 Zen 6c am gleichen L3 und als APU's.

Ein CCD mit P und E Cores ergibt IMO keinen Sinn.

Die Lösung von Intel funktioniert nur, weil AMD bei der Anzahl der Kerne nicht variabel reagieren kann. Für das obere Ende des Desktops funktioniert Zen 4c nicht. AMD müsste das Konzept der "c"-Cores grundsätzlich über den Haufen werfen, wenn "c"-Kerne im High End Desktop eingesetzt werden sollen.

Phoenix 2 hat die doppelte Anzahl von E Cores. Bei Strix Point soll es mit 4 P + 8 E genauso sein. Das ist zwar anders als bei den anderen Hybrid CPUs, aber es könnte das Markenzeichen von AMD Hybrid CPUs sein. Denn da die E-Cores dieselbe IPC haben, kann die Lastverteilung zwischen P und E Cores ganz anders aussehen. Je kleiner das Power Budget ist und je geringer die Frequenz ist, desto attraktiver ist Zen 4c.

RKCPU schrieb:

Die Zen 5c und 6c DIE's dürften einen L3 bekommen, der auch via 3D Chip erweiterbar ist, wie 48 MB plus 48 MB on Top.

Dafür gibt es keinen Grund. Die TSV kosten Die-Fläche und erhöhen die Fertigungskosten. Für die Applikationen, die vom großen L3-Cache profitieren, gibt es als Basis die klassischen Kerne.

Man modularisiert, um mit wenigen Bausteinen viele Anwendungen abzudecken. Mit mehreren Kombinationen von Dies dieselbe Anwendung abzudecken, ergibt keinen Sinn und ist Resourcenverschwendung.

Nimm doch bitte das Beispiel IOD. Auch ich hätte für Siena einen eigenen IOD erwartet. Aber es kam ganz anders. Und es ist auch nachvollziehbar warum. Wir Laien schauen viel zu sehr auf die Die-Fläche. Und übersehen dabei die vielen anderen Kostenfaktoren. Einen Die für vier Plattformen zu verwenden bringt eine enorme Kostenersparnis bei der Entwicklung und Validierung dieser Plattformen. Die größere Die-Fläche wird außerdem relativiert, weil auch teildefekte Dies verwendet werden können.

RKCPU schrieb:

Wenn Du mich fragst viel zu viel Spekulation und das auch noch bei meist ziemlich langweiligen Fragen.

Das winzige was mich wirklich interessiert ist, wie organisiert AMD die Kerne bei Strix Point.

RKCPU schrieb:

aber AMD muss die teuren Wafer ab 5nm auch effizient nutzen.

Das tut AMD.

Im übrigen hätte ich erwartet, dass AMD erst mit Zen 6 auf 3 nm wechselt, aber AMD selbst hat gesagt dass Zen 5 in 4 nm und 3 nm kommt.

Bei den APUs spricht viel dafür, dass sie in 4 nm kommen. Das IOD soll ja angeblich nicht verändert werden. AMD wird aller Voraussicht nach den N3E-Prozess verwenden und hier ergibt sich für SRAM keine Verkleinerung.

Meine Erwartung ist, dass AMD mit beiden CCDs auf 3 nm wechselt. Nur mit der "c"-Variante auf 3 nm zu wechseln, ergibt für mich keinen Sinn, da man dann für die klassischen Kerne auf die Verbesserungen mit Performance bzw. Power von 3 nm verzichtet .

Was es bringen soll, die CCD zuerst in 4 nm und dann nochmal in 3 nm zu designen, erschließt sich mir nicht. Es bindet Resourcen, die in anderen Projekten fehlen. In diesem Punkt ist MLID auch ganz gewaltig von "3 nm erst 2025" abgerückt.

Die eigentlich für mich interessanten Fragen sind:

- Werden die TSV bei allen Zen 3 und Zen 4 CCD tatsächlich auf die volle Tiefe (ca. 20 µm) hergestellt, oder nur bei den Wafern die für den Einsatz mit 3D V-Cache vorgesehen sind?

Hintergrund: Das Ätzen ist ein langsamer Vorgang.

- Was bringt Zen 5 in Bezug auf Performance und Power?

- Wann kommen die einzelnen Zen 5 Produkte?

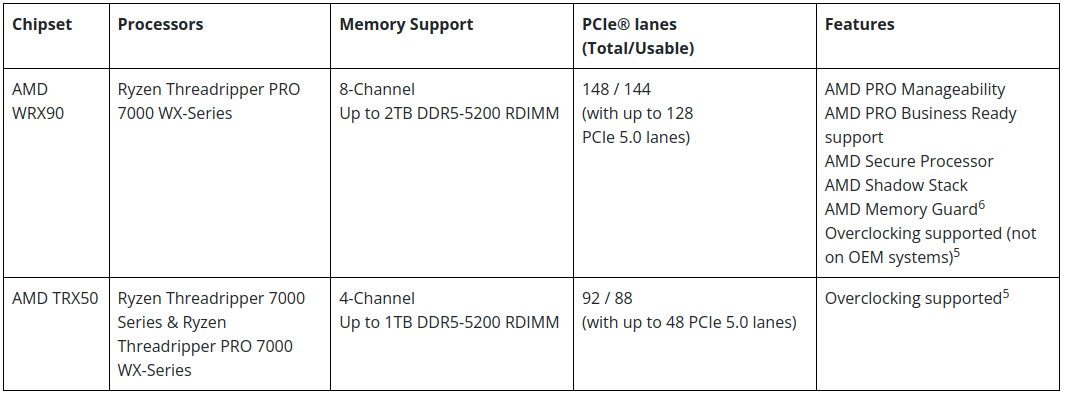

Zen 4 brachte nicht nur den Umstieg von 7 nm auf 5 nm, sondern auch die Einführung von DDR5 und PCIe 5.0 und deswegen neue Plattformen: AM5, SP5, SP6, TRX40 und WRX90. Das erforderte einen großen Aufwand bei der Validierung. Die Einführung von Zen 5 wird viel einfacher, das die Plattformen bereit sind.

- Wie wird in Zukunft der Releasezyklus bei Zen sein?

24 Monate wie hier einige meinen, wird IMO auf Dauer nicht funktionieren.

- Wie wird die AIE bei den Chiplet Ryzen und EPYC eingebunden?

- Auf dem IOD?

- Auf dem CCD?

- Als eigenes Chiplet?

- Bleibt AMD mit Zen 5 komplett auf MCM oder wechselt AMD zumindest bei einigen SKUs auf Fanout?

Mit Fanout können erheblich feinere Leiterbahnen realisiert werden. Im Umkehrschluss bedeutet es, dass eine erheblich höhere Verbindungsdichte möglich ist. Bei derselben Anzahl von Verbindungen ist das Routing erheblich einfacher. Ein Nebeneffekt wäre, dass die Chiplets mit geringerem Abstand positioniert werden könnten.

- Bleibt AMD beim einem classic CCD von Desktop bis Server oder wird es classic CCDs mit unterschiedlicher Anzahl von Kernen geben?

16 Kerne je CCD sind im Desktop unpraktisch. 6 und 8 Kerne auf dieser Bais wäre zu teuer. Eine APU mit 4 P und 8 E wird die Lücke nach unten nicht schließen. Hier wäre eine APU mit 8 P Kernen erforderlich. Oder eben ein zweites CCD.

- Wann verwendet AMD Hybrid Bonding für andere Chiplet als das Cache Chiplet

stefan92x schrieb:

Das ist also ganz grob die vierfache Wärmemenge pro CCD verglichen mit dem TR und würde daher verdammt schwer bis unmöglich zu kühlen sein.

Dazu gibt es drei Dinge zu sagen:

- Die 170 W TDP bei Ryzen 7000 sind komplett unnötig.

- Die Threadripper werden beschränkt, um sie von den EPYC besser abzugrenzen

- Nvidia bekommt bei GH100 700 Watt an Wärme abgeführt.

Das Problem ist nicht das Silizium, sondern die sehr ineffizienten Kühlungsmethoden im PC. Anstatt die Wärme gleich auch dem Gehäuse abzuführen wird sie zuerst im Gehäuse verteilt und erst dann abgeführt. Es soll ja schön leise sein.

PS828 schrieb:

wichtig ist hier inwiefern AMD möglichkeiten zur leistungsanpassung gibt. epyc geht auch bis 420W für SP5 da wirds bei TR doch sicherlich möglicheiten zum tunen geben, selbst für den Pro

5

5 Overclocking and/or Undervolting AMD processors and memory, including without limitation, altering clock frequencies / multipliers or memory timing / voltage, to operate outside of AMD’s published specifications will void any applicable AMD product warranty, even when enabled by AMD hardware and/or software. This may also void warranties offered by the system manufacturer or retailer. Users assume all risks and liabilities that may arise out of overclocking / undervolting AMD processors, including, without limitation, failure of or damage to hardware, reduced system performance and/or data loss, corruption, or vulnerability. GD-106

Overclocking wird auch bei Ryzen Threadripper PRO 7000 unterstützt. Nur die fertig konfigurierten Systeme werden es nicht unterstützen. Man wird sehen was die Boards auffahren.

IMO reichen 350 W bis 32 Kerne dicke. Bei 64 und vor allem 96 Kernen wird's dann schon dünn. Ich denke man sollte ganz gut rechnen, ob sich die 96 Kerne für die eigenen Anwendungen wirklich lohnen.